# INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS

# 2005 Edition

# ASSEMBLY AND PACKAGING

THE ITRS IS DEVISED AND INTENDED FOR TECHNOLOGY ASSESSMENT ONLY AND IS WITHOUT REGARD TO ANY COMMERCIAL CONSIDERATIONS PERTAINING TO INDIVIDUAL PRODUCTS OR EQUIPMENT.

THE INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS: 2005

# TABLE OF CONTENTS

| Chapter Scope                                                              |    |

|----------------------------------------------------------------------------|----|

| Difficult Challenges                                                       |    |

| Technology Requirements                                                    |    |

| Single Chip Packages<br>High Pin-Count Packages                            | 7  |

| Wafer Level Packaging                                                      |    |

| System in a Package (Multi-chip Packages, 3D Packaging)                    | 8  |

| Flexible Substrates and Interconnect                                       | 8  |

| Optoelectronic Packaging                                                   | 9  |

| RF Packaging                                                               | 9  |

| MEMS                                                                       | 10 |

| Medical and Bio Chip Packaging                                             | 11 |

| Biocompatibility                                                           |    |

| Bio Packaging Reliability                                                  |    |

| Integrated Circuit                                                         |    |

|                                                                            |    |

| Cost                                                                       |    |

| Reliability<br>Package and Interconnect Characterization and Simulation    |    |

| Simulation                                                                 |    |

| Reliability Testing                                                        |    |

| Soft Errors                                                                | 14 |

| Packaging Materials Requirements                                           | 14 |

| New Materials                                                              | 14 |

| Embedded and Integrated Passives                                           | 16 |

| Assembly and Packaging Infrastructure Challenges                           | 16 |

| Electrical Design Requirements                                             |    |

| Cross Talk                                                                 |    |

| Power Distribution and Power Subsystem                                     |    |

| Thermo-mechanical Challenges in Electronic Packaging                       |    |

| Mechanical Challenges<br>Mechanical Modeling and Simulation and Validation |    |

| Thermal Modeling and Simulation and Validation                             |    |

| 0                                                                          |    |

| Equipment Requirements for Emerging Package Types<br>Potential Solutions   |    |

| Wafer Level Packaging                                                      |    |

| Chip to Next Level Interconnect                                            |    |

| Package to Board Interconnect                                              |    |

| Fine Pitch Ball Grid Array/CSP Packages                                    |    |

| Socketed Parts                                                             |    |

| Embedded and Integrated Passives                                           | 24 |

| Package Substrates                                                         |    |

| Build-Up and Coreless Substrates                   |    |

|----------------------------------------------------|----|

| Rigid Substrate Technology                         | 31 |

| System in Package (SiP) – System Level Integration | 31 |

| Types/Categories of SiP's                          | 31 |

| Side by Side Placement (Horizontal Packages)       |    |

| Stacked Structures                                 |    |

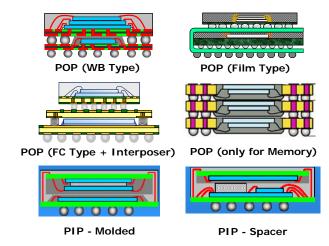

| Package-on-Package (POP), Package-in-Package (PiP) |    |

| Stacked Die Packages                               |    |

| Chip to Chip/Wafer Structure                       |    |

| Embedded Structures                                |    |

| Technologies for SiP                               |    |

| Wafer level SiP and 3 D Integration Technologies   |    |

| Technologies for Embedded Devices                  |    |

| Challenges for SiP<br>Thermal management           |    |

| System in Package Outlook                          |    |

| Wafer Thinning                                     |    |

| Glossary of Terms                                  |    |

| Cross-Cut ITWG Issues                              |    |

| Design                                             |    |

| Factory Integration                                |    |

| Die Traceability Crosscut with Factory Integration |    |

| Interconnect                                       |    |

| RF/AMS Wireless                                    |    |

|                                                    |    |

| Environment, Safety and Health                     |    |

| Modeling and Simulation                            |    |

| Metrology                                          |    |

| Test                                               | 44 |

|                                                    |    |

# LIST OF FIGURES

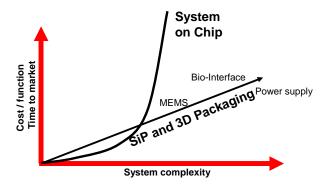

| Figure 90 | SoC and SiP Comparison for Cost per Function and Time to Market vs. Complexit                                      | y8 |

|-----------|--------------------------------------------------------------------------------------------------------------------|----|

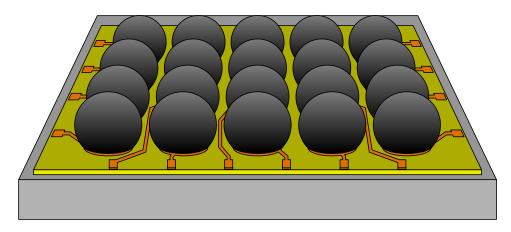

| Figure 91 | Example of a Wafer Level Package with Redistribution                                                               | 20 |

| Figure 92 | SiP Types and Categories                                                                                           | 32 |

| Figure 93 | Technologies for Stacked Packages                                                                                  | 33 |

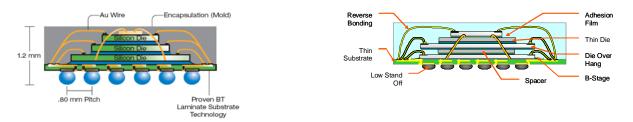

| Figure 94 | Examples of Stacked Die Packages                                                                                   | 33 |

| Figure 95 | 3D Integration Provides Space Saving and Short, Direct Interconnect Lines                                          | 34 |

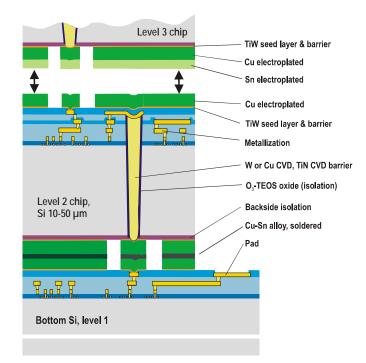

| Figure 96 | ICV-SLID Technology: Schematic for the Formation of Multiple Device Stacks                                         | 37 |

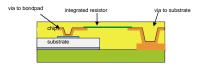

| Figure 97 | Principle of the Chip in Polymer (CiP-Fraunhofer) Structure with<br>Embedded Active and Integrated Passive Devices | 37 |

# LIST OF TABLES

| Table 93a  | Assembly and Packaging Difficult Challenges—Near-term           | 2  |

|------------|-----------------------------------------------------------------|----|

| Table 93b  | Assembly and Packaging Difficult Challenges—Long-term           | 3  |

| Table 94a  | Single-chip Packages Technology Requirements—Near-term Years    | 5  |

| Table 94b  | Single-chip Packages Technology Requirements—Long-term Years    | 6  |

| Table 95   | Materials Challenges                                            | 15 |

| Table 96a  | Chip to Package Substrate—Near-term Years                       | 21 |

| Table 96b  | Chip to Package Substrate—Long-term Years                       | 21 |

| Table 97a  | Substrate to Board Pitch—Near-term Years                        | 23 |

| Table 97b  | Substrate to Board Pitch—Long-term Years                        | 23 |

| Table 98a  | Package Substrate Physical Properties—Near-term Years           | 26 |

| Table 98b  | Package Substrate Physical Properties—Long-term Years           | 27 |

| Table 98c  | Package Substrate Design Parameters—Near-term Years             | 28 |

| Table 98d  | Package Substrate Design Parameters—Long-term Years             | 29 |

| Table 99   | Package Level System Integration                                | 35 |

| Table 100  | Processes used for SiP                                          |    |

| Table 101a | a System-in-a-Package Requirements—Near-term Years              |    |

| Table 101b | System-in-a-Package Requirements—Long-term Years                | 39 |

| Table 102a | a Thinned Silicon Wafer Thickness 200 mm/300 mm—Near-term Years | 40 |

| Table 102b | Thinned Silicon Wafer Thickness 200 mm/300 mm—Long-term Years   | 40 |

|            |                                                                 |    |

# ASSEMBLY AND PACKAGING

# **CHAPTER SCOPE**

This chapter addresses the near-term Assembly and Packaging roadmap requirements and introduces many new requirements and potential solutions to meet market needs in the longer term. Assembly and Packaging is the final manufacturing process transforming semiconductor devices into functional products for the end user. Packaging provides electrical connections for signal transmission, power input and voltage control. It also provides for thermal dissipation and the physical protection required for reliability.

Today Assembly and Packaging is a limiting factor in both cost and performance for electronic systems. This has resulted in acceleration of innovation. Design concepts, packaging architectures, materials, manufacturing processes and systems integration technologies are all changing rapidly. As traditional Moore's law scaling become more difficult, assembly and packaging innovation allowing scaling in the third dimension is taking up the slack.

This accelerated pace of innovation has resulted in development of several new technologies and expansion and acceleration of others introduced in prior years. Wireless and mixed signal devices, bio-chips, optoelectronics and MEMS have placed new requirements on packaging and assembly. The rapid adoption of these new elements in the expanding consumer electronics market has been a strong driver of innovations such as Systems in a Package (SIP), Wafer Level Packaging (WLP) and 3 Dimensional Packaging. New architectures include printable circuits, thinned wafers and both active and passive embedded devices are emerging as solutions to market requirements. The materials and equipment used in assembly and packaging are also changing rapidly to meet the requirements of these new architectures and the changing environmental regulatory requirements.

This Chapter is organized in five sections:

- Difficult Challenges

- Technology Requirements

- Infrastructure

- Potential Solutions

- Cross-Cut Issues

Wherever possible we have aligned the ITRS Assembly and Packaging chapter with other industry roadmap organizations including iNEMI, JISSO, and IPC.

# **DIFFICULT CHALLENGES**

Innovation in assembly and packaging is accelerating in response to the realization that packaging is now the limiting factor in cost and performance for many types of devices. Near term difficult challenges exist in all phases of the assembly and packaging process from design through manufacturing, test and reliability.

Many critical technology requirements are yet to be met and they are listed in Tables 93a and b below. Meeting these requirements will require significant investment in research and development. This investment is greater than current run rates and cannot be met through the current gross margin of the assembly and packaging suppliers. This gap in resources available and resources required may be the greatest of the Difficult Challenges.

| Difficult Challenges $\geq 32$ nm          | Summary of Issues                                                                                                                 |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Impact of new materials                    | BEOL materials including Cu/low $\kappa$                                                                                          |

|                                            | Direct wirebond and bump to Cu or improved barrier systems bondable<br>pads                                                       |

|                                            | Bump and underfill technology to assure low-κ dielectric integrity including lead free solder bump system                         |

|                                            | Improved fracture toughness of dielectric materials                                                                               |

|                                            | Interfacial adhesion                                                                                                              |

|                                            | Reliability of first level interconnect with low $\kappa$                                                                         |

|                                            | Mechanisms to measure the critical properties need to be developed                                                                |

|                                            | Probing over copper/low κ                                                                                                         |

|                                            | Singulation technology for circuits incorporating ultra low $\kappa$ dielectrics                                                  |

| Wafer Level Packaging                      | I/O pitch between 150 µm and 250 µm greater than 100 I/O                                                                          |

|                                            | Solder joint reliability                                                                                                          |

|                                            | Wafer thinning and handling technologies                                                                                          |

|                                            | Compact ESD structures (this applies to other package types as well)                                                              |

|                                            | TCE mismatch compensation for large die                                                                                           |

| Coordinated Design Tools and Simulators to | Mix signal co-design and simulation environment                                                                                   |

| address Chip, Package, and Substrate Co-   | Rapid turn around modeling and simulation                                                                                         |

| design                                     | Integrated analysis tools for transient thermal analysis and integrated thermal mechanical analysis                               |

|                                            | Electrical (power disturbs, EMI, signal and power integrity associated with higher frequency/current and lower voltage switching) |

|                                            | In package decoupling                                                                                                             |

|                                            | System level co-design                                                                                                            |

|                                            | EDA for "native" area array is required to meet the Roadmap projections                                                           |

|                                            | Models for reliability prediction                                                                                                 |

| Embedded Components                        | Low cost embedded passives: R, L, C                                                                                               |

|                                            | Embedded active devices at both wafer and substrate level                                                                         |

|                                            | Wafer level embedded components                                                                                                   |

| Thinned die packaging                      | Wafer/die handling for thin die                                                                                                   |

|                                            | Compatibility of different carrier materials (organics, silicon, ceramics, glass, laminate core)                                  |

|                                            | Reliability                                                                                                                       |

|                                            | Testability                                                                                                                       |

|                                            | Thin die for embedded active devices                                                                                              |

|                                            | Electrical and optical interface integration                                                                                      |

| Close gap between chip and substrate –     | Increased wireability at low cost                                                                                                 |

| Improved Organic Substrates                | Improved impedance control and lower dielectric loss to support higher frequency applications                                     |

|                                            | Improved planarity and low warpage at higher process temperatures                                                                 |

|                                            | Low-moisture absorption                                                                                                           |

|                                            | Increased via density in substrate core                                                                                           |

|                                            | Alternative plating finish to improve reliability                                                                                 |

|                                            | Tg compatible with Pb free solder processing (including rework @260C)                                                             |

| High Current Density Packages              | Electromigration                                                                                                                  |

|                                            | Thermal/mechanical reliability modeling.                                                                                          |

|                                            | Whisker growth                                                                                                                    |

|                                            | Thermal dissipation                                                                                                               |

| Flexible System Packaging                  | Conformal low cost organic substrates                                                                                             |

|                                            | Small and thin die assembly                                                                                                       |

|                                            | Handling in low cost operation                                                                                                    |

Table 93a Assembly and Packaging Difficult Challenges—Near-term

| Difficult Challenges $\geq 32 \text{ nm}$ | Summary of Issues                                                 |  |  |  |

|-------------------------------------------|-------------------------------------------------------------------|--|--|--|

| 3D Packaging                              | Thermal management                                                |  |  |  |

|                                           | Co-Design and simulation tools                                    |  |  |  |

|                                           | Wafer to wafer bonding                                            |  |  |  |

|                                           | Through wafer Via structure and via fill process                  |  |  |  |

|                                           | Bumpless interconnect architecture                                |  |  |  |

| Fine Pitch Packages                       | Tighter tolerances for fine pitch BGA                             |  |  |  |

|                                           | Minimizing kerf loss in singulation for small outline packages    |  |  |  |

|                                           | High temperature warpage for fine pitch BGA                       |  |  |  |

|                                           | Reliability to meet drop test requirements for mobile electronics |  |  |  |

| Difficult Challenges <32 nm                                                     | Summary of Issues                                                                                                                                                                 |

|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Package Cost does not follow the Die Cost<br>Reduction Curve                    | Margin in packaging is inadequate to support investment required to reduce cost                                                                                                   |

|                                                                                 | Increased device complexity requires higher cost packaging solutions                                                                                                              |

| Small Die with High Pad Count and/or High<br>Power Density                      | These devices may exceed the capabilities of current assembly and<br>packaging technology requiring new solder/UBM with:                                                          |

|                                                                                 | Improved current density capabilities                                                                                                                                             |

|                                                                                 | Higher operating temperature                                                                                                                                                      |

| High Frequency Die                                                              | Substrate wiring density to support >20 lines/mm                                                                                                                                  |

|                                                                                 | Lower loss dielectrics-skin effect above 10 GHz                                                                                                                                   |

|                                                                                 | "Hot spot" thermal management                                                                                                                                                     |

| System-level Design Capabilityfor Integrated<br>Chips, Passives, and Substrates | Partitioning of system designs and manufacturing across numerous<br>companies will make optimization for performance, reliability, and<br>cost of complex systems very difficult. |

|                                                                                 | Complex standards for information types and management of information quality along with a structure for moving this information will be required.                                |

|                                                                                 | Embedded passives may be integrated into the "bumps" as well as substrates.                                                                                                       |

| Emerging Device Types<br>(Organic, Nanostructures, Biological)                  | Organic device packaging requirements not yet define (will chips grow their own packages)                                                                                         |

| that require New Packaging Technologies                                         | Biological packaging will require new interface types                                                                                                                             |

#### Table 93b Assembly and Packaging Difficult Challenges—Long-term

There are signs that the technical community is responding:

- University research in packaging is increasing around the world

- Chemical companies have increased their investment in the new materials required to meet the future needs across a broad front from low κ materials and high κ materials to new polymers for integrated passive components.

- Venture capital investment in packaging and interconnect technology is increasing after several years of absence

- Equipment companies are investing in new capability to meet the needs of emerging requirements for making and handling thinned wafers, thinned die and both wafer level and 3D packaging

- Government and Private research institutes are increasing their investment in this area:

- Fraunhofer Institute, IMEC, LETI, IME and ITRI are prime examples

- Independent device manufacturers are investing in new packaging technology to meet the requirements of their products

- Consumer product companies are driving innovation in SiP and other new system integration architectures

Even with this increased investment the current level is inadequate to meet the Difficult Challenges within the Roadmap time frame. The acceleration of this investment and the efficient coordination of development among these groups will be necessary to achieve the scheduled Roadmap milestones for assembly and packaging. One of the major objectives of this chapter is to encourage and facilitate the coordination and focus of these efforts on the Difficult Challenges.

# **TECHNOLOGY REQUIREMENTS**

Assembly and packaging technology requirements are being driven as much by the rapidly changing market requirements as by the advancing silicon technology generations. New package types are evolving in response to the demand for smaller, thinner and lighter electronic products for the rapidly expanding consumer market. Wafer Level Packaging (WLP) and System in Package (SiP) are two new packaging categories requiring implementation of new complex manufacturing technologies and significant infrastructure investments. Wafer Level Packaging, where the packaging functions are achieved through wafer level processing, holds the promise of lower cost and improved performance for single die packages. System in package, where system integration is achieved in die packaging, enables the smaller size, lower cost, higher performance and shorter time to market demanded for consumer electronics. These two package types represent paradigm shifts whose further advancements will in turn deliver technology to meet both the demands of future market applications and advancing semiconductor technology generations.

Optoelectronics, RF and Mixed Signal, MEMS devices and medical and biotechnology devices will require specialized packaging to serve new market applications. Their advancements will demand continued innovation in packaging technology.

Continuously decreasing cost per function remains key to growth of the electronics market. Packaging cost has not been scaling with IC manufacturing cost and even the limited cost-per-pin decreases have been flattening out. At the same time, new devices require increased package pin count. New technologies will be required to deliver increasing performance and higher pin count at lower cost. In addition, technical innovation is required to enable trade-offs among form, function, performance and time to market in today's consumer driven market. Wafer level packaging and System in package are two examples of the paradigm shifts that ultimately will achieve the low cost/high performance objectives of the industry.

New package reliability issues arise in the assembly and package of Cu low  $\kappa$  dielectric devices and other new materials and structures. With the introduction of these and other new package and device types there is much research needed in the reliability physics, related materials science and the physical environments where these products are being used. These technologies will be required if we are to meet the demand for increased reliability.

# SINGLE CHIP PACKAGES

Moore's law scaling in IC manufacture has enabled rapid increase in performance and decrease in cost. This poses extreme challenges for assembly and packaging processes which do not have the same scaling advantages to reduce cost and improve performance. Incremental improvements in traditional assembly technologies will not be sufficient to meet market requirements. The technical requirements for single chip packages are summarized in Tables 94a and b.

| Table 9-                                                                   | Table 94a Single-chip Packages Technology Requirements—Near-term Years |                |           |             |             |             |             |             |             |

|----------------------------------------------------------------------------|------------------------------------------------------------------------|----------------|-----------|-------------|-------------|-------------|-------------|-------------|-------------|

| Year of Production                                                         | 2005                                                                   | 2006           | 2007      | 2008        | 2009        | 2010        | 2011        | 2012        | 2013        |

| DRAM 1/2 Pitch (nm) (contacted)                                            | 80                                                                     | 70             | 65        | 57          | 50          | 45          | 40          | 36          | 32          |

| MPU/ASIC Metal 1 (M1) <sup>1</sup> / <sub>2</sub><br>Pitch (nm)(contacted) | 90                                                                     | 78             | 68        | 59          | 52          | 45          | 40          | 36          | 32          |

| MPU Physical Gate Length (nm)                                              | 32                                                                     | 28             | 25        | 22          | 20          | 18          | 16          | 14          | 13          |

| Cost per Pin Minimum for Contra                                            | ct Assembly [                                                          | 1,2] (Cents/Pi | n)        | •           |             |             |             |             |             |

| Low-cost, hand held and memory                                             | .27–.50                                                                | .26–.49        | .25–.48   | .24–.47     | .23–.46     | .22–.45     | .21–.43     | .20–.42     | .20–.41     |

| Cost-performance                                                           | .68–1.17                                                               | 66–1.11        | .64–1.05  | .63–1.00    | .62–.96     | 0.61–.94    | .60–.92     | 0.58–.90    | 0.57–.89    |

| High-performance                                                           | 1.78                                                                   | 1.74           | 1.71      | 1.68        | 1.64        | 1.61        | 1.58        | 1.55        | 1.51        |

| Harsh                                                                      | 0.29-2.61                                                              | 0.26-2.34      | 0.25-2.11 | 0.23-2.00   | 0.22-1.90   | 0.22-1.54   | .21-1.46    | 0.20-1.38   | 0.20-1.31   |

| Chip Size (mm <sup>2</sup> ) [3] JISSO an                                  | d ITRS not all                                                         | igned          |           |             |             |             |             |             |             |

| Low-cost                                                                   | 100                                                                    | 100            | 100       | 100         | 100         | 100         | 100         | 100         | 100         |

| Cost-performance                                                           | 140                                                                    | 140            | 140       | 140         | 140         | 140         | 140         | 140         | 140         |

| High-performance                                                           | 600                                                                    | 630            | 662       | 695         | 729         | 766         | 804         | 750         | 750         |

| Harsh                                                                      | 100                                                                    | 100            | 100       | 100         | 100         | 100         | 100         | 100         | 100         |

| Maximum Power (Watts/mm <sup>2</sup> ) [4]                                 | T                                                                      |                |           |             |             |             |             |             |             |

| Low-cost (Watts) [1]                                                       | 2.80                                                                   | 3.00           | 3.00      | 3.00        | 3.00        | 3.00        | 3.00        | 3.00        | 3.00        |

| Cost-performance                                                           | 0.65                                                                   | 0.70           | 0.74      | 0.79        | 0.83        | 0.85        | 0.85        | 0.89        | 0.98        |

| High-performance                                                           | 0.54                                                                   | 0.58           | 0.61      | 0.64        | 0.64        | 0.64        | 0.64        | 0.64        | 0.64        |

| Harsh                                                                      | 0.16                                                                   | 0.18           | 0.18      | 0.20        | 0.20        | 0.22        | 0.22        | 0.24        | 0.25        |

| Core Voltage (Volts)                                                       | T                                                                      |                |           |             |             |             |             |             |             |

| Low-cost                                                                   | 1                                                                      | 0.9            | 0.9       | 0.8         | 0.8         | 0.6         | 0.6         | 0.6         | 0.5         |

| Hand-held                                                                  | 0.9                                                                    | 0.8            | 0.7       | 0.6         | 0.6         | 0.5         | 0.5         | 0.5         | 0.4         |

| Cost-performance                                                           | 1                                                                      | 0.9            | 0.9       | 0.8         | 0.8         | 0.6         | 0.6         | 0.6         | 0.6         |

| High-performance                                                           | 1                                                                      | 0.9            | 0.9       | 0.8         | 0.8         | 0.6         | 0.6         | 0.6         | 0.6         |

| Harsh                                                                      | 1.2                                                                    | 1.2            | 1.2       | 1.2         | 1.2         | 1.2         | 1           | 1           | 0.9         |

| Package Pincount Maximum [5][6]                                            | Not align                                                              | ed with JISSO  | )         |             |             |             |             |             |             |

| Low-cost                                                                   | 134–550                                                                | 140–578        | 148-606   | 150-636     | 160-668     | 170–700     | 180–738     | 188–774     | 198-812     |

| Cost-performance                                                           | 550-900                                                                | 550-990        | 600–1088  | 600–1198    | 660–1318    | 660–1450    | 720–1596    | 720–1754    | 800–1930    |

| High performance                                                           | 3000                                                                   | 3180           | 3371      | 3573        | 3787        | 4015        | 4256        | 4511        | 4736        |

| Harsh                                                                      | 350                                                                    | 368            | 386       | 405         | 425         | 447         | 469         | 492         | 517         |

| Minimum Overall Package Profile                                            |                                                                        |                |           |             |             |             |             |             |             |

| Low-cost                                                                   | 0.4                                                                    | 0.4            | 0.4       | 0.3         | 0.3         | 0.3         | 0.3         | 0.3         | 0.3         |

| Cost-performance                                                           | 0.80                                                                   | 0.80           | 0.80      | 0.65        | 0.65        | 0.65        | 0.65        | 0.50        | 0.50        |

| High-performance                                                           | 1.4                                                                    | 1.4            | 1.4       | 1.4         | 1.4         | 1.2         | 1.2         | 1           | 1           |

| Harsh                                                                      | 0.80                                                                   | 0.80           | 0.80      | 0.80        | 0.80        | 0.80        | 0.80        | 0.70        | 0.70        |

| Performance: Chip-to-Board for I                                           |                                                                        |                |           |             |             |             |             |             |             |

|                                                                            | 100/400                                                                | 100/533        | 100/667   | 100/800     | 100/800     | 125/800     | 125/800     | 125/1000    | 125/1000    |

| Cost-performance (for multi-<br>drop nets)                                 | 533                                                                    | 667            | 733       | 800         | 800         | 800         | 800         | 1000        | 1000        |

| High-performance (for<br>differential-pair point-to-point<br>nets)         | 3125                                                                   | 3906           | 4883      | 6103        | 7629        | 9536        | 11920       | 14900       | 18625       |

| Harsh                                                                      | 88                                                                     | 96             | 106       | 106         | 115         | 125         | 125         | 125         | 125         |

| Maximum Junction Temperature                                               |                                                                        |                |           |             |             |             |             |             |             |

| Low-cost                                                                   | 125                                                                    | 125            | 125       | 125         | 125         | 125         | 125         | 125         | 125         |

| Cost-performance                                                           | 100                                                                    | 100            | 95        | 95          | 90          | 90          | 90          | 90          | 90          |

| High-performance                                                           | 100                                                                    | 100            | 95        | 95          | 90          | 90          | 90          | 90          | 90          |

| Harsh                                                                      | 175                                                                    | 175            | 175       | 175         | 200         | 220         | 220         | 220         | 220         |

| Operating Temperature Extreme: Ambient (°C)                                |                                                                        |                |           |             |             |             |             |             |             |

|                                                                            |                                                                        | 55/85          | 55/85     | 55/85       | 55/85       | 55/85       | 55/85       | 55/85       | 55/85       |

| Low-cost (use case/purchase specification)                                 | 55/85                                                                  | 00,00          |           |             |             |             |             |             |             |

|                                                                            | 55/85<br>45/70                                                         | 45/70          | 45/70     | 45/70       | 45/70       | 45/70       | 45/70       | 45/70       | 45/70       |

| specification)<br>Cost-performance                                         |                                                                        |                |           | 45/70<br>55 | 45/70<br>55 | 45/70<br>55 | 45/70<br>55 | 45/70<br>55 | 45/70<br>55 |

Table 94a Single-chip Packages Technology Requirements—Near-term Years

Table 94b

Single-chip Packages Technology Requirements—Long-term Years

| Table 94b Single-ci                                         | hip Package | s Technolo          | gy Require | ments—Lon | ig-term Yea | ars       |           |

|-------------------------------------------------------------|-------------|---------------------|------------|-----------|-------------|-----------|-----------|

| Year of Production                                          | 2014        | 2015                | 2016       | 2017      | 2018        | 2019      | 2020      |

| DRAM <sup>1</sup> / <sub>2</sub> Pitch (nm) (contacted)     | 28          | 25                  | 22         | 20        | 18          | 16        | 14        |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)(contacted)               | 28          | 25                  | 22         | 20        | 18          | 16        | 14        |

| MPU Physical Gate Length (nm)                               | 11          | 10                  | 9          | 8         | 7           | 6         | 6         |

| Cost per Pin Minimum for Contract Assembly [1,2] (Ce        | nts/Pin)    |                     |            |           |             |           |           |

| Low-cost, hand held and memory                              | .20–.39     | .19–.38             | .19–.37    | .18–.36   | .18–.35     | .18–.34   | .17–.34   |

| Cost-performance                                            | 0.5687      | 0.55–.85            | 0.54–.83   | 0.53–.81  | 0.5280      | 0.51–.79  | 0.50–.79  |

| High-performance                                            | 1.48        | 1.45                | 1.43       | 1.40      | 1.37        | 1.35      | 1.32      |

| Harsh                                                       | .20-1.24    | .19–1.17            | .19–1.12   | .18–1.06  | 0.18-1.00   | .18–.94   | .17–.89   |

| Chip Size (mm <sup>2</sup> ) [3] JISSO and ITRS not aligned |             | •                   |            | •         | •           | •         | •         |

| Low-cost                                                    | 100         | 100                 | 100        | 100       | 100         | 100       | 100       |

| Cost-performance                                            | 140         | 140                 | 140        | 140       | 140         | 140       | 140       |

| High-performance                                            | 750         | 750                 | 750        | 750       | 750         | 750       | 750       |

| Harsh                                                       | 100         | 100                 | 100        | 100       | 100         | 100       | 100       |

| Maximum Power (Watts/mm <sup>2</sup> ) [4]                  |             |                     |            |           |             |           |           |

| Low-cost (Watts) [1]                                        | 3.00        | 3.00                | 3.00       | 3.00      | 3.00        | 3.00      | 3.00      |

| Cost-performance                                            | 0.98        | 0.98                | 1.08       | 1.08      | 1.08        | 1.12      | 1.12      |

| High-performance                                            | 0.64        | 0.64                | 0.64       | 0.64      | 0.64        | 0.64      | 0.64      |

| Harsh                                                       | 0.25        | 0.27                | 0.28       | 0.28      | 0.29        | 0.29      | 0.3       |

| Core Voltage (Volts)                                        | 0.20        | 0.27                | 0.20       | 0.20      | 0.20        | 0.20      | 0.0       |

| Low-cost                                                    | 0.5         | 0.4                 | 0.4        | 0.4       | 0.4         | 0.40      | 0.4       |

| Hand-held                                                   | 0.3         | 0.4                 | 0.4        | 0.4       | 0.4         | 0.40      | 0.4       |

|                                                             | 0.4         | 0.4                 | 0.4        | 0.4       | 0.4         | 0.4       | 0.4       |

| Cost-performance<br>High-performance                        | 0.5         | 0.5                 | 0.5        | 0.5       | 0.5         | 0.5       | 0.5       |

|                                                             |             |                     |            |           |             |           |           |

| Harsh                                                       | <b>8.0</b>  | 0.7                 | 0.7        | 0.7       | 0.7         | 0.7       | 0.7       |

| Package Pincount Maximum [5][6] Not aligned wi              |             | 040.000             | 000 040    | 0.40,000  | 050 4000    | 000 4000  | 070 4440  |

| Low-cost                                                    | 208-850     | 218-896<br>880-2336 | 230-940    | 240-988   | 250-1036    | 266-1088  | 278-1142  |

| Cost-performance                                            | 800-2124    |                     | 880-2568   | 960-2824  | 960-3108    | 1050-3418 | 1050-3760 |

| High performance                                            | 4973        | 5222                | 5483       | 5757      | 6045        | 6347      | 6665      |

| Harsh                                                       | 543         | 570                 | 599        | 629       | 660         | 693       | 728       |

| Minimum Overall Package Profile (mm)                        |             |                     |            |           |             |           |           |

| Low-cost                                                    | 0.2         | 0.2                 | 0.2        | 0.2       | 0.2         | 0.2       | 0.2       |

| Cost-performance                                            | 0.50        | 0.50                | 0.50       | 0.50      | 0.50        | 0.50      | 0.50      |

| High-performance                                            | 1           | 1                   | 1          | 1         | 1           | 1         | 1         |

| Harsh                                                       | 0.60        | 0.60                | 0.50       | 0.50      | 0.50        | 0.40      | 0.4       |

| Performance: Chip-to-Board for Peripheral Buses (MH         |             | 1                   | 1          | 1         | n           | 1         | 1         |

| Logic/memory                                                | 125/1000    | 125/1000            | 150/1200   | 150/1200  | 150/1200    | 150/1200  | 150/1200  |

| Cost-performance (for multi-drop nets)                      | 1000        | 1000                | 1200       | 1200      | 1200        | 1200      | 1200      |

| High-performance (for differential-pair point-to-point      | 23282       | 29102               | 36378      | 45472     | 56840       | 71051     | 88813     |

| nets)                                                       |             |                     |            |           |             |           |           |

| Harsh                                                       | 125         | 150                 | 150        | 150       | 150         | 150       | 150       |

| Maximum Junction Temperature                                |             | 1                   | 1          | 1         | 1           | 1         | 1         |

| Low-cost                                                    | 125         | 125                 | 125        | 125       | 125         | 125       | 125       |

| Cost-performance                                            | 90          | 90                  | 90         | 90        | 90          | 90        | 90        |

| High-performance                                            | 90          | 90                  | 90         | 90        | 90          | 90        | 90        |

| Harsh                                                       | 220         | 220                 | 220        | 220       | 220         | 220       | 220       |

| Operating Temperature Extreme: Ambient (°C)                 |             |                     |            |           |             |           |           |

| Low-cost (use case/purchase specification)                  | 55/85       | 55/85               | 55/85      | 55/85     | 55/85       | 55/85     | 55/85     |

| Cost-performance (MPU/Commercial)                           | 45/70       | 45/70               | 45/70      | 45/70     | 45/70       | 45/70     | 45/70     |

| High-performance                                            | 55          | 55                  | 55         | 55        | 55          | 55        | 55        |

|                                                             |             |                     |            |           |             |           |           |

Notes for Table 94a and b: Several entries are not aligned with JISSO Chip size is below actual devices shipping today Maximum chip power density will not occur in the largest die Power density numbers are average per die. Within the die there may be hot spots with substantially higher local power density Range in pin count for low cost and cost performance is due to different device types and package technologies employed The chip size for cost performance is driven by microprocessors and high performance is driven by FPGA and ASIC devices

> Manufacturable solutions exist, and are being optimized Manufacturable solutions are known Interim solutions are known Manufacturable solutions are NOT known

Today wire bonding on 65 nm technology and 45 nm low  $\kappa$  devices is under development. In addition the impact of the mold compounds on silicon technologies using Cu/low  $\kappa$  material is not yet well understood. New approaches are required which are described in the materials section of this chapter.

The largest die today is  $26 \text{ mm} \times 23 \text{ mm}$  and current approaches cannot achieve this for 32 nm. The die size limit is the largest that can be manufactured with sustainable yields. This places practical limitations on die size that are less than maximum exposure equipment capability in most cases. Multi-die package technologies may be a more economical alternative to ever larger die with increasing numbers of transistors. The average die sizes, however, are likely to increase slowly as the process yields improve making larger devices economically advantageous. The likelihood of any drastic increase in die size in the near term is remote for reasons of economics due to yield considerations and time required to develop new technologies.

Packages to accommodate those larger die face challenges of increasing I/O and power requirements. The substrate dominates the cost of single chip packaging and the routing complexity of high I/O channel count with required power and ground support may further increase the cost. The substrate technology to accommodate finer lines and spaces, finer via pad geometries, finer via sizes and increasing layer counts will inevitably drive cost higher. Higher frequencies require improved signal integrity to minimize noise further increasing pressure on substrate wireability and therefore on cost.

# HIGH PIN-COUNT PACKAGES

Since the introduction of the BGA in the early '90s, area array packages have enabled system designers to take advantage (cost effectively) of denser I/O interconnect schemes and package technology supporting thousands of I/O. The increase in I/O count continues with no end in sight.

There has been a dramatic increase in the need for high I/O count. Package pin count has grown even more rapidly as the higher frequency and higher power density demand more power and ground pins to meet signal integrity requirements. To meet the interconnect challenge, package substrate technology has introduced micro-via's, blind and buried via's, stacked via's and tighter lines and spacing. Although substrate design rules have advanced to enable high density, several barriers had to be overcome. These include significant cost increases for design and test and a reduced supplier base.

Another issue with increasing I/O count packages is the routing complexity of the host PCB. As I/O speeds go deeper into the GHz spectrum, routing schemes for serial and parallel busses become very complex. This in itself has created, prolonged design cycles with verification times increasing and system de-bug even more arduous. The introduction of SerDes technology is a step the industry is taking to reduce buss parallelism, thus reducing the number of interconnects between IC's. Even single-ended parallel bussing to memory die is moving towards SerDes design with the introduction of Fully Buffered DIMM.

Design for signal integrity has lead to the requirement of improving the power sub-system in the package to the board. This has resulted in increasing the number of Vdd and Vss per signal I/O. Tightening I/O:Vdd:Vss ratios have resulted in increasing package pin counts and continue to increase with higher performance I/O technologies.

System-in-Package will become increasingly important to reduce the need for high density interconnects in the package substrate and PCB.

### WAFER LEVEL PACKAGING

Wafer Level Packaging (WLP) is a technology in which all of the IC packaging is performed at the wafer level. A WLP technology requires all package interconnects to be continuously located within the chip outline (fan-in design) producing a true chip size package. From a systems perspective, the limitation on WLP is how many I/O can be placed under the chip and still have a board design that can be routed. Although the basic infrastructure has been available for several years the technology was not adopted since existing packaging solutions met market requirements.

WLP can provide a solution when requirements for continued decrease in size, increase in IC operating frequency and demand for cost reduction are not met by traditional packaging. The advantages of WLP technologies include lower cost, improved performance, decreased power, shorter time to market and smaller size. WLP technologies are discussed in more detail in the potential solutions section.

# SYSTEM IN A PACKAGE (MULTI-CHIP PACKAGES, 3D PACKAGING)

The reduction in size, weight, cost and power demanded by the consumer electronics market cannot be met without technical innovation. System in a package enables significant improvement in all these parameters.

Today the market is demanding shorter product life cycles while product complexity is increasing. System on a chip (SoC) solutions can address the size weight and power requirements but at the expense of increased cost per function and time to market as illustrated in Figure 90. The integration of highly complex systems must be carried out cost efficiently, with a high degree of miniaturization and flexibility. New integration techniques such as 3D integration packaging are become more important for SiP solutions. The SiP technology also allows incorporation of other circuit elements such as MEMS, optoelectronics and bio-electronics into the package reducing system cost and improving performance.

Figure 90 SoC and SiP Comparison for Cost per Function and Time to Market vs. Complexity

The key elements of SiP technology are:

- system partitioning/modularization

- chip-package co-design (on-chip, off-chip)

- integration of different functions in one package

- application of "add on" technologies to increase system functionality

- high dense component integration

- Known Good Die

- Test and reliability

- short time to market cycles

- low cost

#### FLEXIBLE SUBSTRATES AND INTERCONNECT

In many emerging applications electronic products must be flexible. An electronic product may be folded and twisted so it can fit into a very limited confined space or through its normal use such as for thin "smart cards". Flexibility is also important for some medical applications. For example, a hearing aid should be almost invisible and conform to the shape of each individual's ear. Telemedicine or patient monitoring applications can be enabled with transponders placed either

on or embedded in clothing. As cost continues to decrease, consumers will want electronic products integrated into their garments requiring compatibility with washing cycles in hot water with detergent, hot-air dryers and the heat and pressure of ironing.

ICs and passives devices may be surface-mounted on a flexible interconnecting substrate or integrated as thin film structures into flexible wiring layers. In some applications, these wiring layers must be stretchable. Die thinned to below 20 microns and embedded inside the wiring layers may use compliant bumping techniques for interconnect and thin molding for protection from the environment. Metal-coated polymer fibers may be deployed as conductive wires using a garment as the supporting substrate. A relatively large and flexible antenna could also be embroidered in a garment for patient monitoring or other RFID applications.

Flexibility of interconnect components such as microsprings and compliant bump structures will also be necessary to meet the requirements of future multi-chip packages. SiP with die and other components of varying thickness integrated into a dense package will require compliant structures to compensate for thickness variation and lack of coplanarity

#### **OPTOELECTRONIC PACKAGING**

For optoelectronic communication applications, a package is to provide the housing for components to implement the required functions and the interfacing ports to other functions in the overall system. The components are the light emitting device, the photo-detector, optical amplifier, the modulator, the driver IC, optical lenses, beam deflector ... etc. The interfacing ports could be an optical window, an optical fiber, or an RF connector. For high data rate lasers, a thermoelectric cooler may also be needed in the housing.

In general, hermetic sealing is often necessary to protect the optical devices. TO header and butterfly packaging serve these needs. Alternative protection techniques for the less expensive, non-hermetically sealed organic packaging are required, especially for the extremely cost sensitive access network applications.

For high data rate communications using single mode fiber, the less than 0.5  $\mu$ m tight alignment between single mode fiber and the optical device is an expensive requirement. For the cost sensitive access network applications, it is necessary to relax the alignment requirement, using the relative large diameter polymer optical fiber (POF) and automatic assembly to achieve 5 to 10  $\mu$ m alignment accuracy. Note that adhesive is needed to assure the above alignment be maintained throughout the succeeding high temperature processes and product usage life. POF material improvement in attenuation reduction and data rate increase is required. Material development for poly-clad-silica (PCS) fiber must also be pursued.

For further cost reduction and performance improvement, vertical integration to include more functionality in a package is needed. For example, one may use wafer-level-packaging (WLP) process to integrate lenses or other micro-optical-electro-mechanical system (MOEMS) devices, and to provide environmental protection for a VCSEL wafer.

Some micro-optical components, e.g. polymer waveguides and beam reflectors, may be embedded in the SiP substrate. A BGA based SiP may house optical connectors, laser diodes, photodetectors, CMOS IC containing receivers/drivers and multiplexer/demultiplexer, plus RF connectors, and decoupling capacitors.

Digital Image sensors are being introduced in a wide range of consumer and industrial products including optical mouse, mobile phone, digital camera, PC, camcorder, scanners, security camera, etc. The high end applications are served by CCD image sensor devices, while the medium and low end applications are served by CMOS image sensor devices. Most image sensor dies are packaged in cavity packages with glass lids. For the high end applications, ceramic packages with hermetic sealing are preferred. For medium and low end packages plastic packages are preferred for lower cost. Optically clear molding compound or clear glob tops may be used for optical windows to save cost for the low end image sensors and communications components. Wafer level packaging approaches are becoming more prevalent due to its small form factor, low height, and low cost manufacturing potential. In this wafer level process the silicon wafer is sandwiched between two glass panels. The requirements are for combining image sensor device with other devices in the form of system in packages as subsystem module components.

# **RF PACKAGING**

Many of the technology challenges for RF packaging arise from the fact that the IC packaging engineering practice, technology knowledge base, and manufacturing infrastructures have been based upon digital IC packaging developed in the last forty odd years. In RF packaging, the package is part of the RF circuit, and the packaging requirements for RF devices and for digital devices are not the same. The circuit performance is strongly influenced by the interaction of the

electromagnetic field with all the adjacent conductors and insulators. While they all require passive components, their characteristic parameters lie in different ranges. With the market demand for cell phones and other consumer oriented wireless portable products, the drive towards RF package integration with passive components, and for system in package with ASICs, memory devices and RF devices in the same package, further add to the breadth and complexity in RF packaging technology requirements.

RF technologies encompasses a broad range of market applications such as cellular phones, GPS, 3G cellular phones, WLAN, UWB, Direct Broadcast Satellite, mm Wave communications, vehicle anti-collision system, ranging from just below 1 GHz to approaching 100 GHz.

Plastic wirebond-leadframe molded packages are the low cost workhorse for low pin count devices in the industry. At the same time inductance characteristics associated with bonding wires and leaded packages, and effect of molding compound materials limit the RF performance. With the shorter interconnection paths in array packages with flip chip interconnect and WLP some of these problems can be reduced. It is important to provide RF package modeling tools and well as materials properties database for package design and device-package co-design for the broad spectrum of RF market applications. Corresponding improvements in materials properties—molding compounds, underfills, substrates—would be required.

Materials and process advancements such as in low temperature co-fired ceramic (LTCC), originally developed for military applications, have exhibited relatively low loss and shrinkage have a potential to further improve built embedded passive components. Progress in process science understanding, cost and manufacturability would be required for implementation in the higher frequency range market applications. To meet the low cost challenges, embedded inductance and capacitance components and networks in organic packaging for RF applications must be diligently pursued. One particularly challenging RF product family is RFID applications which require extremely low package cost, integration of antenna functions and the ability to protect the device in harsh environments.

SiP advancements provide great opportunities for placing RF and digital devices in a common package platform. The rich and diverse SIP technologies and manufacturing infrastructure—die and package stacking approaches such as PiP and POP as well as various embedded passive integration, will be applicable for RF applications. Particularly important will be the direction for reduction in size and weight of the SIP packages while increasing package complexity. It will be critical that RF physical design and modeling and simulations capabilities, and materials advances, mentioned previously for single chip package, be fully extended into the SIP arena where both RF and digital components share the common package platform. Tools to enable device package co-design in SIP packages will be very important.

In a SiP, RF ICs are modeled as multi-port S-parameter networks, which integrate well with the 2D and 3D frequency domain modeling for the SiP substrate having embedded passives. However, the digital ICs are represented as IBIS models, requiring time-domain signals in their inputs, and generating time-domain signals in their outputs. Time-consuming manual conversions between frequency- and time-domain signals by highly skilled designers are required. Automated modeling and physical design tools are needed to improve the SiP design turn-around time and overall cost.

# MEMS

Micro-Electro-Mechanical Systems (MEMS) is the integration of mechanical elements, sensors, actuators, and electronics on a common silicon substrate through microfabrication technology. While the electronics are fabricated using integrated circuit (IC) process sequences (e.g., CMOS, Bipolar, or BICMOS processes), the micromechanical components are fabricated using compatible "micromachining" processes that selectively etch away parts of the silicon wafer or add new structural layers to form the mechanical and electromechanical devices.

MEMS encompasses a wide variety of devices. MEMS may be classified into four categories based upon their generic functional applications: (1) RF MEMS, (2) Bio MEMS, (3) Inertial MEMS, and (4) Optical MEMS. For each category their functions and operational environments will dictate the packaging requirements. For example MEMS based accelerometers and gyroscopes are three dimensional structures with moving parts within the structure. The package must provide appropriate closed cavity space for the device functional operation. On the other hand packaging for some bio sensors must provide controlled open fluid access for specimen sampling with specifically defined surface absorption properties. Tabulated below are the functional and packaging requirements for these four MEMS categories.

| $\stackrel{MEMS\ Packaging}{\downarrow} \rightarrow$ | RF MEMS                                                                                                                                                                                                                                                                                                     | BioMEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Inertial MEMS                                                                                                                                                                                                                                          | Optical MEMS                                                                                                                                                                                                                                                                               |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Requirements                                         | Electrical - low insertion loss - low back reflection - low contact resistance - frequency - signal isolation - package resonance - low parasitics Structural - low stress - small form factor Package - wafer level package - small form factor - hermeticity - low loss packaging material - light weight | Fluidic         -       low dead volume         -       sensitivity in detection         -       low back pressure         -       fluidic channel size         -       fluidic channel size         -       flow rate         -       heating/cooling rate         Electrical       -         -       interface with electronic circuits         Thermal       -         -       fast heating and cooling         Optical       -         -       low optical loss         Structural       -         -       low stress at fluidic joints         Package       -         -       modular package         -       disposable | Structural<br>– low stress<br>– meet reliability<br>requirements<br>Thermal<br>– temperature<br>stabilization<br>Electrical<br>– sensitivity<br>– switching time<br>– frequency<br>– Q factor<br>Package<br>– plastic package<br>– wafer level package | Optical<br>– low coupling loss<br>– mirror rotation/angle<br>Structural<br>– low stress package<br>– low shrinkage of UV<br>epoxy<br>– low warpage<br>Thermal<br>– thermal stabilization<br>Electrical<br>– switching speed and<br>time<br>Package<br>– ceramic package<br>– metal package |

| Difficult Challenges                                 | Optimization of electrical<br>and structural<br>parameters<br>Low cost materials to<br>reduce insertion loss<br>Form factor reduction<br>Passive device integration                                                                                                                                         | Co-design of fluidic,<br>electrical thermal,<br>optical and structural<br>design<br>Dead vacuum reduction<br>Channel size reduction<br>Zero back pressure<br>Flow in nano channels<br>Bubble elimination<br>Bio compatibility of<br>material                                                                                                                                                                                                                                                                                                                                                                                   | Structural design<br>Reliability of package<br>Vacuum/hermeticity<br>Low cost<br>Small form factor<br>Integration into other<br>systems                                                                                                                | Optical, structural design<br>to meet low coupling<br>loss/reliability<br>Low cost<br>Integration into other<br>systems                                                                                                                                                                    |

| Potential Directions                                 | RF system in package<br>Bio-RF integration                                                                                                                                                                                                                                                                  | 3D microfluidic package<br>Bio system in package<br>Plastic based fluidic<br>systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MEMS system in package<br>– mobile application<br>– bio application<br>– information<br>technology                                                                                                                                                     | Wafer level package                                                                                                                                                                                                                                                                        |

# MEDICAL AND BIO CHIP PACKAGING