# INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS

2005 EDITION

FRONT END PROCESSES

THE ITRS IS DEVISED AND INTENDED FOR TECHNOLOGY ASSESSMENT ONLY AND IS WITHOUT REGARD TO ANY COMMERCIAL CONSIDERATIONS PERTAINING TO INDIVIDUAL PRODUCTS OR EQUIPMENT.

# **TABLE OF CONTENTS**

| Scope                                                          |    |

|----------------------------------------------------------------|----|

| Difficult Challenges                                           |    |

| The Front End Processes Grand Challenge—                       | 2  |

| The FEP Response to the Era of Material-Limited Device Scaling | 2  |

| Technology Requirements and Potential Solutions                | 5  |

| Starting Materials                                             | 5  |

| Front End Surface Preparation                                  | 16 |

| Thermal/Thin Films, Doping, and Etching Thermal/Thin-Films     |    |

| Doping Technology                                              | 36 |

| Front End Etch Processing                                      | 41 |

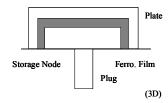

| DRAM Stacked Capacitor                                         | 44 |

| DRAM Trench Capacitor                                          | 48 |

| Non-Volatile Memory (Flash)                                    | 50 |

| Phase Change Memory                                            | 53 |

| Ferroelectric Random Access Memory (FeRAM)                     |    |

| Cross-Cut Issues                                               |    |

| FEP Metrology Cross-Cut Issues                                 |    |

| FEP Modeling and Simulation Cross-Cut Issues                   | 58 |

| FEP Environment, Safety, and Health Cross-Cut Issues           |    |

| Inter-Focus ITWG Discussion                                    |    |

| Impact of Future Emerging Research Devices                     |    |

| Conclusion                                                     |    |

| References                                                     |    |

| Starting Materials                                             |    |

| Surface Preparation                                            |    |

| Thermal, Thin Film, Doping and Etching                         |    |

| DRAM Stacked Capacitor                                         |    |

| Phase Change Memory                                            |    |

| Ferroelectric Random Access Memory (FeRAM)                     | 61 |

# **LIST OF FIGURES**

| Figure 55          | Front End Process Chapter Scope                                             | 1    |

|--------------------|-----------------------------------------------------------------------------|------|

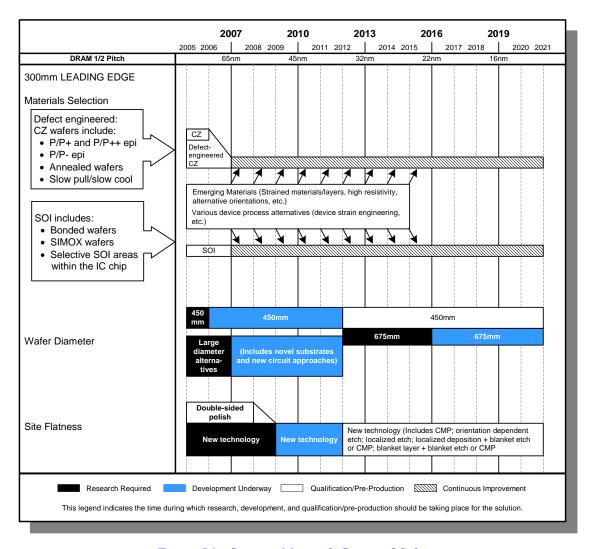

| Figure 56          | Starting Materials Potential Solutions                                      | . 15 |

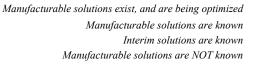

| Figure 57          | Surface Preparation Potential Solutions                                     | .21  |

| Figure 58          | Thermal/Thin Films Potential Solutions                                      | . 35 |

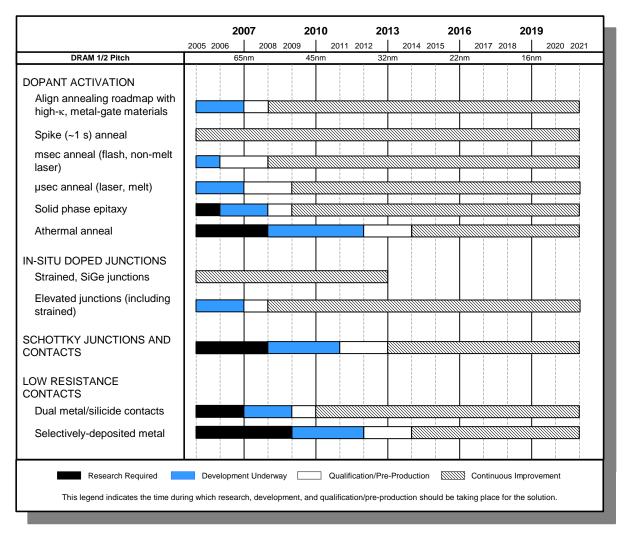

| Figure 59          | Doping Potential Solutions                                                  | . 40 |

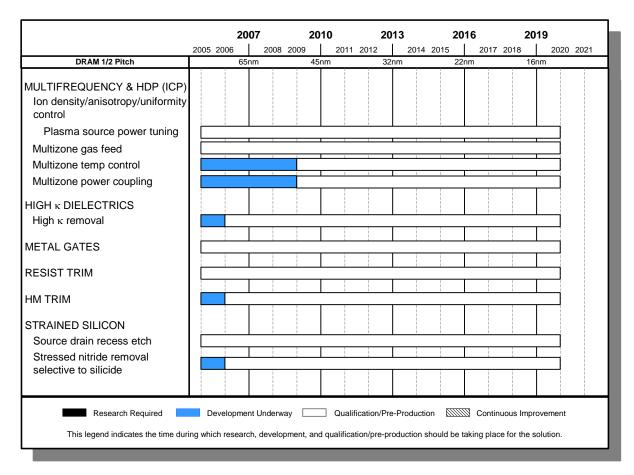

| Figure 60          | Front End Processes Etching Potential Solutions                             | . 44 |

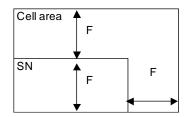

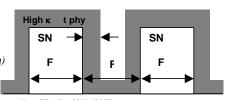

| Figure 61          | DRAM Stacked Capacitor Potential Solutions                                  | .48  |

| Figure 62          | Minimum Feature Size of NAND Flash Memory                                   | .50  |

| Figure 63          | Minimum Feature Size of NOR Flash Memory                                    | .51  |

| Figure 64          | Flash Memory Interpoly Dielectric Thickness Scaling at 45 nm                |      |

| Figure 65          | FeRAM Potential Solutions                                                   |      |

| LIST OF TA         | BLES                                                                        |      |

| Table 66a          | Front End Processes Difficult Challenges—Near-term Years                    | 3    |

| Table 66b          | Front End Processes Difficult Challenges—Long-term Years                    |      |

| Table 67a          | Starting Materials Technology Requirements—Near-term Years                  |      |

| Table 67b          | Starting Materials Technology Requirements—Long-term Years                  | .11  |

| Table 68a          | Surface Preparation Technology Requirements—Near-term Years                 | . 17 |

| Table 68b          | Surface Preparation Technology Requirements—Long-term Years)                |      |

| Table 69a<br>Years | Thermal and Thin Film, Doping and Etching Technology Requirements—Near-tern |      |

| Table 69b          | Thermal and Thin Film, Doping and Etching Technology Requirements—Long-terr | n    |

| Table 70a          | DRAM Stacked Capacitor Films Technology Requirements—Near-term Years        | . 46 |

| Table 70b          | DRAM Stacked Capacitor Films Technology Requirements—Long-term Years        | . 47 |

| Table 71a          | DRAM Trench Capacitor Technology Requirements—Near-term Years               |      |

| Table 71b          | DRAM Trench Capacitor Technology Requirements—Long-term Years               | .49  |

| Table 72a          | FLASH Non-volatile Memory Technology Requirements—Near-term Years           | .52  |

| Table 72b          | FLASH Non-volatile Memory Technology Requirements—Long-term Years           | .53  |

| Table 73a          | FeRAM Technology Requirements—Near-term Years                               | .56  |

| Table 73b          | FeRAM Technology Requirements—Long-term Years                               | .57  |

|                    |                                                                             |      |

# FRONT END PROCESSES

# SCOPE

The Front End Processes (FEP) Roadmap focuses on future process requirements and potential solutions related to scaled field effect transistors (MOSFETs), DRAM storage capacitors, as well as Flash and ferroelectric RAM (FeRAM) devices. The purpose of this chapter is to define comprehensive future requirements and potential solutions for the key front end wafer fabrication process technologies and materials associated with these devices. Hence, this Roadmap encompasses the tools, and materials, as well as the unit and integrated processes starting with the silicon wafer substrate and extending through the contact silicidation processes. The following specific technology areas are covered: *starting materials*, *surface preparation, thermal/thin films, doping*, and *front end plasma etch* for MOSFETs, as well as processes and materials for *DRAM stack* and *trench capacitors, Flash memory gate structures*, *Phase-change memory*, and *FeRAM storage devices*.

A forecast of scaling-driven technology requirements and potential solutions is provided for each technology area. The forecasted requirements tables are model-based unless otherwise noted. The potential solutions identified serve to benchmark known examples of possible solutions, and are intended for other researchers and interested parties. They are not to be considered the only approaches. Indeed, innovative, *novel solutions* are sought, and are identified by red colored regions of the requirements tables.

Some FEP-related topics are presented in other sections of this Roadmap. The scaled device performance and structures' forecasts that drive FEP requirements are covered in the *Process Integration, Devices, and Structures (PIDS)* chapter. Issues for copper/low-κ dielectrics cleaning and surface preparation, plasma etch, and chemical mechanical polish (CMP) for trench isolation are found in the *Interconnect* chapter because of overlap with interconnect tool issues. The crosscut needs of FEP are covered in the following chapters: *Yield Enhancement, Metrology, Environment, Safety, & Health*, and *Modeling & Simulation*. FEP factory requirements are covered in the *Factory Integration* chapter.

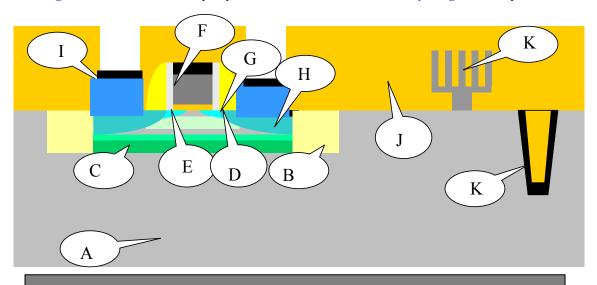

- A: Starting Material

- C: Well Doping

- E: Channel Doping and Channel Strain

- G: Extension Junction and Halo

- I: Elevated Junction and Contacts

- K: DRAM Stack/Trench Capacitor & FeRAM Storage

- B: Isolation

- D: Channel Surface (Preparation)

- F: Gate Stack (Including Flash) and Spacer

- H: Contacting Source/Drain Junction

- J: Premetal Dielectric

Figure 55 Front End Process Chapter Scope

# **DIFFICULT CHALLENGES**

# THE FRONT END PROCESSES GRAND CHALLENGE—

## THE FEP RESPONSE TO THE ERA OF MATERIAL-LIMITED DEVICE SCALING

MOSFET scaling has been the primary means by which the semiconductor industry has achieved the historically unprecedented gains in productivity and performance quantified by Moore's Law. These gains have traditionally been paced by the development of new lithography tools, masks, photoresist materials, and critical dimension etch processes. In the past several years it has become clear that despite advances in these crucial process technologies and the resultant ability to produce ever-smaller feature sizes, front end process technologies have not kept pace, and scaled device performance has been compromised. The crux of this problem comes from the fact that the traditional transistor and capacitor formation materials, silicon, silicon dioxide, and polysilicon have been pushed to fundamental material limits and continued scaling has required the introduction of new materials. The current situation can be defined as "material-limited device scaling."

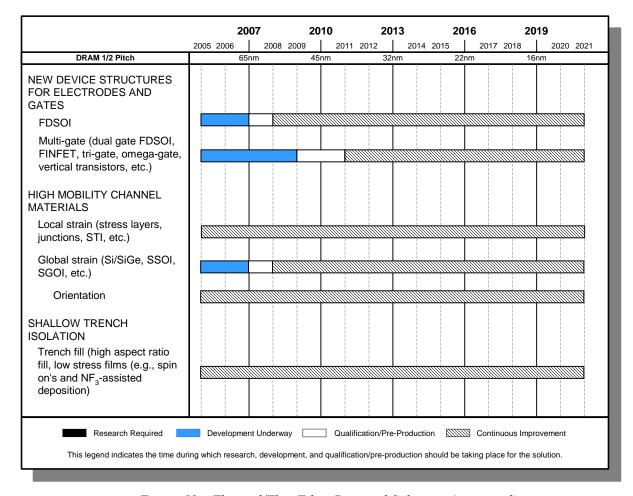

Material-limited device scaling has placed new demands on virtually every front end material and unit process, starting with the silicon wafer substrate and encompassing the fundamental planar CMOS building blocks and memory storage structures. In addition, the end of planar bulk CMOS is becoming visible within the next several years. As a consequence we must be prepared for the emergence of CMOS technology that uses non-conventional MOSFETs or alternatives such as planar fully depleted SOI devices and dual- or multi-gate devices either in a planar of vertical geometry. An overview of the device alternatives is presented in the *Emerging Research Devices chapter*. Many believe these may be needed as early as the year 2008. The challenges associated with these diverse new materials and the control of the physical interfaces associated with these materials constitutes the central theme of the FEP difficult challenges summarized in Table 66.

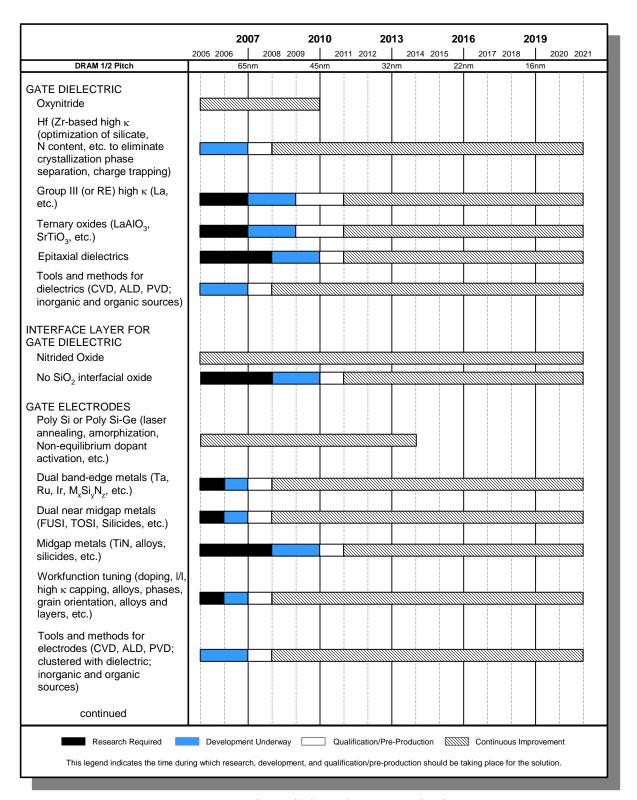

In no area is this issue more clear or urgent than in the MOSFET gate stack. Here, a new gate dielectric material having a higher dielectric constant is needed. This need was identified in the 1999 ITRS where it was linked to MOSFETs having gate lengths smaller than 65 nm, which were at that time expected to emerge in the year 2005. In the interim, the patterning technology for producing 65 nm gates has accelerated and these have been achieved in 2001. Combined with the extension of silicon oxynitride gate dielectric materials and the introduction of strain-enhanced-mobility channels, the need for high-κ has been delayed. Although promising high-κ candidate materials have been identified, fundamental performance and reliability issues, as well as issues with CMOS integration are still under investigation. It is doubtful that these materials will enter production before the year 2007. In the interim, oxynitride gate dielectric materials have nearly reached their leakage limits as dictated by power consumption; accordingly, only mobility enhancement and channellength scaling, which requires accelerated scaling of junctions to control short channel effects, are providing enhanced device performance. A re-optimization of the basic device design, done by the PIDS Technology Working Group (TWG), has capitalized on enhanced mobility channels to delay the need for high-κ dielectrics until the year 2008, at which time they will be needed by both low power and by high performance applications if off-state power consumption expectations are to be met. Looking beyond the gate dielectric, the depletion layers that exist in the doped polysilicon gate material become increasingly onerous as planar devices are scaled into the deep submicron region with the result that dual metal gates, having appropriate work functions, are also needed in 2008 to replace the dual doped polysilicon gates, currently the mainstay of CMOS technology.

Table 66a Front End Processes Difficult Challenges—Near-term Years

| Difficult Challenges ≥ 32 nm                                              | Summary of Issues                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| New gate stack processes and materials                                    | Extension of oxynitride gate dielectric materials to < 1.0 nm EOT for high-performance MOSFETs, consistent with device reliability requirements                                                                                          |

|                                                                           | Control of boron penetration from doped polysilicon gate electrodes while minimizing depletion of dual-doped polysilicon electrodes                                                                                                      |

|                                                                           | Introduction and process integration of high-κ gate stack materials and processes for high-performance, low operating and low standby power MOSFETs                                                                                      |

|                                                                           | CMOS integration of enhanced channel mobility in both NMOS and PMOS devices, using local and global strained layers                                                                                                                      |

|                                                                           | Introduction of dual metal gate electrodes with appropriate work function                                                                                                                                                                |

|                                                                           | Control of silicon loss at spacer etch and gate etch needs to be much tighter on thin SOI and SiGe wafers, where the total silicon thickness is 20–50 nm                                                                                 |

|                                                                           | Removal of high-κ dielectric without loss of the underlying silicon, especially in the case of SOI or non planar devices                                                                                                                 |

|                                                                           | Metrology issues associated with gate dielectric film thickness and gate stack electrical and materials characterization                                                                                                                 |

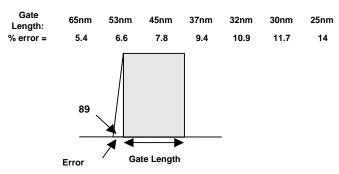

| Critical dimension and effective channel length ( $L_{eff}$ ) control     | Control of gate etch processes that yield a physical gate length that is considerably smaller than the feature size printed in the resist, while maintaining <12% overall 3-sigma control of the combined lithography and etch processes |

|                                                                           | Control of profile shape, edge roughness, line and space width for isolated as well as closely-spaced fine line patterns                                                                                                                 |

|                                                                           | Control of self-aligned doping processes and thermal activation budgets to achieve L <sub>eff</sub> control                                                                                                                              |

|                                                                           | Maintenance of CD and profile control throughout the transition to new gate stack materials and processes                                                                                                                                |

|                                                                           | CD and etch metrology                                                                                                                                                                                                                    |

|                                                                           | Site flatness to ensure effective lithographic printing                                                                                                                                                                                  |

| Introduction and CMOS integration of                                      | Development and introduction of very high-κ DRAM capacitor dielectric layers                                                                                                                                                             |

| new memory materials and processes                                        | Migration of DRAM capacitor structures from silicon-insulator-metal to metal-insulator-metal                                                                                                                                             |

|                                                                           | Integration and scaling of FeRAM ferroelectric materials                                                                                                                                                                                 |

|                                                                           | Scaling of Flash interpoly and tunnel dielectric layers may require high-κ                                                                                                                                                               |

|                                                                           | Limited temperature stability of high-κ and ferroelectric materials challenges                                                                                                                                                           |

|                                                                           | CMOS Integration                                                                                                                                                                                                                         |

| Surfaces and interfaces—structure, composition, and contamination control | Contamination, composition, and structure control of channel/gate dielectric interface as well as gate dielectric/gate electrode interface                                                                                               |

|                                                                           | Interface control for DRAM capacitor structures                                                                                                                                                                                          |

|                                                                           | Maintenance of surface and interface integrity through full-flow CMOS processing                                                                                                                                                         |

|                                                                           | Statistically significant characterization of surfaces having extremely low defect concentrations for starting materials and pre-gate clean surfaces                                                                                     |

|                                                                           | Measurement of back surface particles at/near edge wafer edge (including bevel) has no solution                                                                                                                                          |

|                                                                           | Measurement and understanding of clustering of particles needs significant data to define future specification                                                                                                                           |

|                                                                           | Little information associating back surface particles and the effect on yield                                                                                                                                                            |

| Scaled MOSFET dopant introduction and control                             | Doping and activation processes to achieve shallow source/drain regions having parasitic resistance that is less than $\sim$ 17–33% of ideal channel resistance (= $V_{dd}/I_{on}$ )                                                     |

|                                                                           | Control of parasitic capacitance to achieve less than ~23–29% of gate capacitance, consistent with acceptable Ion and minimum short channel effect                                                                                       |

|                                                                           | Achievement of activated dopant concentration greater than solid solubility in dual-doped polysilicon gate electrodes                                                                                                                    |

|                                                                           | Formation of continuous self-aligned silicide contacts over shallow source and drain regions. Formation of elevated junctions and silicides on FDSOI wafers                                                                              |

|                                                                           | Metrology issues associated with 2D dopant profiling                                                                                                                                                                                     |

Table 66b Front End Processes Difficult Challenges—Long-term Years

| Difficult Challenges < 32 nm                                                                   | Summary of Issues                                                                                                                                                                                              |  |  |  |  |  |

|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Continued scaling of planar CMOS devices                                                       | Higher κ gate dielectric materials including temperature constraints                                                                                                                                           |  |  |  |  |  |

|                                                                                                | Metal gate electrodes with appropriate work function                                                                                                                                                           |  |  |  |  |  |

|                                                                                                | Sheet resistance of clad junctions                                                                                                                                                                             |  |  |  |  |  |

|                                                                                                | CD and L <sub>eff</sub> control                                                                                                                                                                                |  |  |  |  |  |

|                                                                                                | Chemical, electrical, and structural characterization                                                                                                                                                          |  |  |  |  |  |

| Introduction and CMOS integration of non-<br>standard, double gate MOSFET devices              | Devices are needed starting from 2011 and may be needed as early as 2007 (this is a backup for high- κ materials and metal gates on standard CMOS)                                                             |  |  |  |  |  |

|                                                                                                | Selection and characterization of optimum device types                                                                                                                                                         |  |  |  |  |  |

|                                                                                                | CMOS integration with other devices, including planar MOSFETs                                                                                                                                                  |  |  |  |  |  |

|                                                                                                | Introduction, characterization, and production hardening of new FEP unit processes                                                                                                                             |  |  |  |  |  |

|                                                                                                | Device and FEP process metrology                                                                                                                                                                               |  |  |  |  |  |

|                                                                                                | Increased funding of long term research                                                                                                                                                                        |  |  |  |  |  |

|                                                                                                | Introduction of strained silicon in the structural configuration for advanced non-classical CMOS                                                                                                               |  |  |  |  |  |

| Starting silicon material alternatives greater than 300 mm diameter require the start of wafer | Need for future productivity enhancement dictates the requirement for a next generation, large silicon substrate material                                                                                      |  |  |  |  |  |

| manufacturing development in year 2005                                                         | Historical trends suggest that the new starting material have nominally twice the area of present generation substrates, e.g., 450 mm                                                                          |  |  |  |  |  |

|                                                                                                | Economies of the incumbent Czochralski crystal pulling, wafer slicing, and polishing processes are questionable beyond 300 mm; research is required for a cost-effective substrate alternative to bulk silicon |  |  |  |  |  |

|                                                                                                | If 450 mm wafers are to become available for production in 2012 as currently forecasted, wafer manufacturing is already behind schedule and must be implemented in 2005–2006                                   |  |  |  |  |  |

|                                                                                                | Enhanced coordination is required amongst Starting Materials, Factory Integration, Yield Enhancement and the IRC to more effectively assess the anticipated onset of 450 mm use                                |  |  |  |  |  |

| New memory storage cells, storage devices, and                                                 | Scaling of DRAM storage capacitor beyond 6F <sup>2</sup>                                                                                                                                                       |  |  |  |  |  |

| memory architectures                                                                           | Further scaling of Flash memory interpoly and tunnel oxide thickness                                                                                                                                           |  |  |  |  |  |

|                                                                                                | FeRAM storage cell scaling                                                                                                                                                                                     |  |  |  |  |  |

|                                                                                                | Introduction of new memory types and storage concepts (Candidates—MRAM, phase-change memory for 2010, and single electron, molecular, nano-floating products beyond 2010)                                      |  |  |  |  |  |

| Surface and interface structural, contamination, and compositional control                     | Achievement and maintenance of structural, chemical, and contamination control of surfaces and interfaces that may be horizontally or vertically oriented relative to the chip surface                         |  |  |  |  |  |

|                                                                                                | Metrology and characterization of surfaces that may be horizontally or vertically oriented relative to the chip surface                                                                                        |  |  |  |  |  |

|                                                                                                | Achievement of statistically significant characterization of surfaces and interfaces that may be horizontally or vertically oriented relative to the chip surface                                              |  |  |  |  |  |

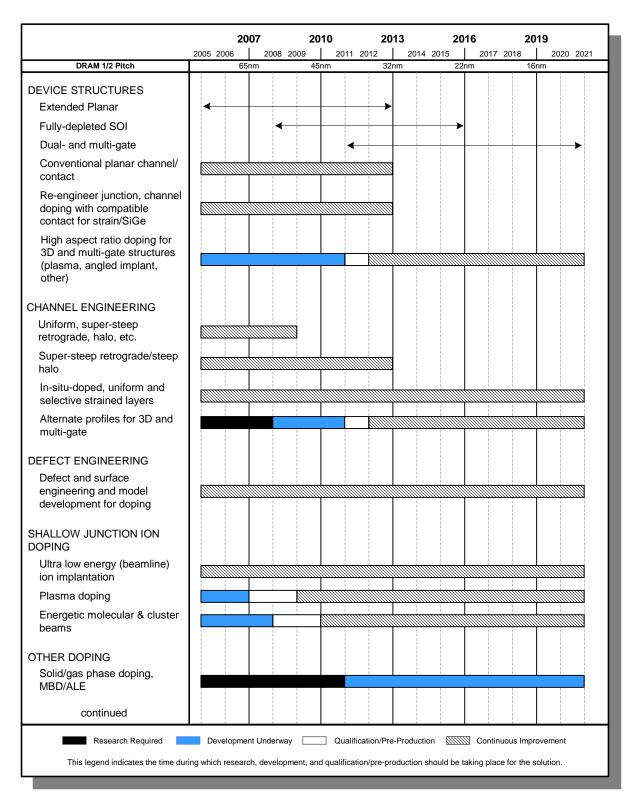

Near-term measures such as the use of strained silicon channels are expected to provide needed boosts to device speed, but ultimately, scaling is expected to require the replacement of planar CMOS devices with non-standard dual gate devices including fully depleted planar devices. The introduction of these devices will require the replacement of bulk silicon substrates with ultra-thin, silicon-on-insulator (SOI) substrates and double- or multi-gate devices. The transition from extended bulk CMOS to non-classical device structures is not expected to take place at the same time for all applications and all chip manufacturers. Instead, a scenario is envisioned where a greater diversity of technologies are competitively used at the same point in time—some manufacturers choosing to make the transition to non-classical devices earlier, while others emphasize extensions of bulk technology.

High-κ materials are now in use for both stacked and trench DRAM capacitors. DRAM stacked capacitors will soon require new metal-insulator-metal structures with trench capacitors following by a few years. It is expected that high-κ materials will be required for the Flash memory interpoly and tunnel dielectric layers. In the memory area it is also expected that FeRAM and MRAM will make a significant commercial appearance where ferroelectric and ferromagnetic storage materials would be used. The introduction of these diverse materials into the manufacturing mainstream is viewed as important, difficult challenges. In addition, phase-change memory (PCM) devices are also making a commercial appearance.

In the starting wafer area, it is expected that alternatives to bulk silicon such as various strained silicon alternatives on bulk, as well as silicon-on-insulator substrates will proliferate. These all imply FEP process architecture changes. An important difficult challenge expected to emerge within the Roadmap horizon is the need for the next generation 450 mm silicon substrate. Here, it is questionable whether the incumbent techniques for wafer preparation can be cost-effectively scaled to the next generation. It is also questionable whether this substrate will be bulk silicon or SOI and whether strained silicon will be the required active layer material. The search for potential substrate alternatives presents an important research need that must commence immediately, if this new substrate material is to be ready for device manufacture in the year 2012.

Front end cleaning processes will continue to be impacted by the introduction of new front end materials. In addition, scaled devices are expected to become increasingly shallow, requiring that cleaning processes become completely benign in terms of substrate material removal and surface roughening. Also, the scaled and new device structures that will be introduced will become increasingly fragile, limiting the physical aggressiveness of the cleaning processes that may be employed. DRAM stacked and trench storage capacitor structures will show increasing aspect ratios making sidewall contamination removal increasingly difficult.

The etching processes used to form the critical dimension features such as MOSFET gates, and DRAM word and bit lines continue to pose difficult challenges in terms of CD and line profile shape control. These problems are expected to become more difficult as etch techniques are increasingly employed to produce feature sizes that are smaller than those printed in the photoresist. As noted in the section on etching, close collaboration between the FEP, Lithography, PIDS, and Design TWGs have resulted in a larger printed gate and increased etch bias to achieve the same physical gate length. In addition, physical gate length variation was increased to 12% and reallocated between etch and lithography to push out this "red brick wall" for a few years. The introduction of new materials in the gate stack is expected to change the nature of these challenges.

The introduction of new materials is also expected to impose added challenges to the methods used to dope and activate silicon. In addition to the scaling imposed need for producing very shallow highly activated junctions, the limited thermal stability of most high-κ materials is expected to place new boundaries on thermal budgets associated with dopant activation. In a worst-case scenario, the introduction of these materials could have a significant impact on the overall CMOS process architecture.

# **TECHNOLOGY REQUIREMENTS AND POTENTIAL SOLUTIONS**

## STARTING MATERIALS

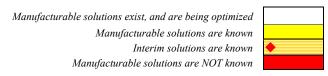

Technology Requirements—Tables 67a and b forecast trends for starting wafers produced by silicon wafer manufacturers that are intended for use in the manufacture of both high density memories such as DRAMs and high-performance MPUs and ASICs. These requirements include parameters common to all wafers plus parameters specific to polished, epitaxial, and SOI wafers. Fundamental barriers presently limit the rate of cost-effective improvement in wafer characteristics such as localized light scatterers (LLS) defect densities, site flatness values, and edge exclusion dimensions. These barriers include the capability and throughput limitations of metrology tools, as well as wafer manufacturing cost and yield issues fundamental to the crystal-pulling process and subsequent wafer finishing operations. Accordingly, a methodology has been introduced to display not only the ability of the wafer supplier to meet the parameter trends in Tables 67a and 67b, but to also display the metrology tool readiness. For this reason, the wafer parameter trend table cells have been annotated with the silicon supplier criticality color code on the left-hand side of each cell and the metrology tool readiness color code depicted on the right-hand side. The marking system and meanings are shown in the Tables for both DRAM and high-performance MPUs.

Wafer Types—For the device types included in the scope of the ITRS, starting materials selection historically involved the choice of either polished Czochralski (CZ) or epitaxial silicon wafers. Recently, silicon-on-insulator (SOI) wafers have become more than a niche technology, although the total number of SOI wafers shipped is still small compared to polished and epi wafers. The opportunity for SOI wafers to be used in mainstream high-volume applications is being driven by improved high-frequency logic performance and reduced power consumption, as well as enhanced device performance via unique device configurations such as multiple-gate structures. In some cases process flow simplification is also achieved. The selection of wafer type is based strongly on performance versus cost.

Commodity devices such as DRAM are commonly manufactured on lower cost CZ polished wafers. The elimination of "crystal originated pits" (COP) in CZ polished wafers is increasingly required to avoid interference with inline inspections used for defect reduction. High-performance logic ICs are generally manufactured on more costly epitaxial

wafers (compared to polished CZ wafers) because their use has facilitated the achievement of greater-robustness (e.g., soft error immunity and latch-up suppression capability). This latter capability may no longer be as critical due to the implementation of shallow trench isolation (STI) and the development of alternate doping means for achieving latch-up suppression. Historically, most wafers used for MPU and ASIC production were p/p+ wafers (lightly doped epi on a heavily doped substrate). Recently, p/p- epi wafers have been used for many applications. Annealed wafers were introduced in the early 1990s as an alternative means to provide a silicon wafer with a COP free surface and are now used for many leading edge device applications. Annealing occurs in either hydrogen or argon ambients at high temperatures. COPs can also be controlled by appropriately engineered CZ growth methodologies. For the purpose of the Starting Materials tables presented here, annealed wafers and "defect engineered CZ" are both considered forms of polished CZ wafers. This wide variety of starting materials will likely continue into the foreseeable future and is the reason for inclusion of polished, epitaxial, and SOI wafers in Tables 67a and b. Emerging materials that may further augment the variety of starting materials are discussed later in this document.

Parameter Values—The wafer requirements have been selected to ensure that in any given year each parameter value contributes no more than 1% to leading-edge chip yield loss. The values in the tables are generally, but not exclusively, derived from probabilistic yield-defect models. These models take into account leading-edge technology parameters such as critical dimension (CD)—taken as the DRAM half-pitch (that is, the technology generation)—bit density, transistor density, and chip size. The validity of these derived values is limited by the sometimes questionable accuracy and predictability of the underlying models. With the onset of nanometer device dimensions for both the gate dielectric equivalent oxide thickness (EOT) and the device physical channel length, compliance with these model-based values can be very costly and, in some cases, requires re-examination. For this reason, detailed re-assessment of the costs incurred versus the value derived from achieving compliance often suggests limiting the scope of these models via appropriate truncation.

Table 67a Starting Materials Technology Requirements—Near-term Years

| Year of Production                                                                               | 2005       |      | 2006     |    | 2007      |     | 2008       | 2009        | )        | 2010    | )   | 2011       |        | 2012        |             | 2013       |

|--------------------------------------------------------------------------------------------------|------------|------|----------|----|-----------|-----|------------|-------------|----------|---------|-----|------------|--------|-------------|-------------|------------|

| DRAM ½ Pitch (nm) (contacted)                                                                    | 80         |      | 70       |    | 65        |     | 57         | 50          |          | 45      |     | 40         |        | 36          |             | 32         |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)(contacted)                                                    | 90         |      | 78       |    | 68        |     | 59         | 52          |          | 45      |     | 40         |        | 36          |             | 32         |

| MPU Physical Gate Length (nm)                                                                    | 32         |      | 28       |    | 25        |     | 23         | 20          |          | 18      |     | 16         |        | 14          |             | 13         |

| DRAM Total Chip Area (mm²)                                                                       | 88         |      | 139      |    | 110       |     | 74         | 117         |          | 93      |     | 74         |        | 117         |             | 93         |

| DRAM Active Transistor Area (mm²)                                                                | 23.1       |      | 36.2     |    | 29.5      |     | 23.1       | 36.4        |          | 29.1    |     | 23.1       |        | 36.0        |             | 29.1       |

| MPU High-Performance Total Chip Area (mm²)                                                       | 246        |      | 195      |    | 310       |     | 246        | 195         |          | 310     |     | 246        |        | 195         |             | 310        |

| MPU High-Performance<br>Active Transistor Area (mm2)                                             | 25.1       |      | 20.0     |    | 31.7      |     | 25.1       | 20.0        |          | 31.7    |     | 25.1       |        | 20.0        |             | 31.7       |

| General Characteristics * (99% Chip Yield) [A, B, G                                              | C]         |      |          |    |           |     |            |             |          |         |     |            |        |             |             |            |

| Maximum Substrate Diameter (mm)—High-volume<br>Production (>20K wafer starts per month)**        | 300        |      | 300      |    | 300       |     | 300        | 300         |          | 300     |     | 300        |        | 450         |             | 450        |

| Edge exclusion (mm)                                                                              | 2          |      | 2        |    | 1.5       |     | 1.5        | 1.5         |          | 1.5     |     | 1.5        | 1      | 1 <u>.5</u> |             | <u>1.5</u> |

| Front surface particle size (nm), latex sphere equivalent [D] [E]                                | ≥90        |      | ≥90      |    | ≥90       |     | ≥90        | ≥65         |          | ≥65     |     | ≥65        | ≥      | 45          |             | ≥45        |

| Particles (cm <sup>-2</sup> )                                                                    | ≤0.35      |      | ≤0.17    |    | ≤0.18     |     | ≤0.17      | ≤0.16       | ≤        | 0.17    |     | ≤0.17      | ≤(     | 0.17        | :           | ≤0.17      |

| Particles (#/wafer)                                                                              | ≤238       |      | ≤116     |    | ≤123      |     | ≤120       | ≤113        |          | ≤115    |     | ≤115       | ≤:     | 265         |             | ≤271       |

| Site flatness (nm), SFQR 26 mm × 8 mm site size [F, R]                                           | ≤80        |      | ≤70      |    | ≤65       |     | ≤57        | ≤50         |          | ≤45     |     | ≤40        | <      | 35          |             | ≤32        |

| Nanotopography, p-v, 2 mm diameter analysis area [Q]                                             | ≤20        |      | ≤18      |    | ≤16       |     | ≤14        | ≤13         |          | ≤11     |     | ≤10        | :      | ≤9          |             | ≤8         |

| Polished Wafer * (99% Chip Yield)                                                                |            |      |          |    |           |     |            |             |          |         |     |            |        |             |             |            |

| The LLS requirement is specified for particles only;                                             | discrimin  | atio | on betwe | en | particles | s a | nd COPs    | is required | d (see   | e Gene  | rai | l Characte | eristi | cs) [D      | , <i>Ej</i> | '          |

| Oxidation stacking faults (OSF) (DRAM) (cm <sup>-2</sup> ) [G]                                   | ≤1.39      |      | ≤1.15    |    | ≤1.03     |     | ≤0.85      | ≤0.71       | ≤        | 0.81    |     | ≤0.52      | ≤(     | 0.43        |             | ≤0.37      |

| Oxidation stacking faults (OSF) (MPU) (cm <sup>-2</sup> ) [G]                                    | ≤0.37      |      | ≤0.32    |    | ≤0.27     |     | ≤0.23      | ≤0.19       | ≤        | 0.16    |     | ≤0.14      | ≤(     | 0.12        | :           | ≤0.10      |

| Epitaxial Wafer * (99% Chip Yield)                                                               |            |      |          |    |           |     |            |             |          |         |     |            |        |             |             |            |

| Total Allowable Front Surface Defect Density is The<br>Characteristics) [H, I]                   | e Sum of E | Epit | axial La | rg | e Structu | ra  | l Defects, | Small Stri  | ucture   | al Defe | ect | s and Pari | ticles | (see (      | Gen         | eral       |

| Large structural epi defects (DRAM) (cm <sup>-2</sup> ) [J]                                      | ≤0.011     |      | ≤0.007   |    | ≤0.009    |     | ≤0.014     | ≤0.009      | ≤        | 0.011   |     | ≤0.014     | ≤0     | .009        | 14          | ≤0.011     |

| Large structural epi defects (MPU) (cm <sup>-2</sup> ) [J]                                       | ≤0.004     |      | ≤0.005   |    | ≤0.003    |     | ≤0.004     | ≤0.005      | ≤        | 0.003   |     | ≤0.004     | ≤0     | .005        | 4           | ≤0.003     |

| Small structural epi defects (DRAM) (cm <sup>-2</sup> ) [K]                                      | ≤0.023     |      | ≤0.014   |    | ≤0.018    |     | ≤0.027     | ≤0.017      | ≤        | 0.022   |     | ≤0.027     | ≤0     | .017        | 1           | ≤0.022     |

| Small structural epi defects (MPU) (cm <sup>-2</sup> ) [K]                                       | ≤0.008     |      | ≤0.010   |    | ≤0.006    |     | ≤0.008     | ≤0.010      | ≤        | 0.006   |     | ≤0.008     | ≤0     | .010        | 4           | ≤0.006     |

| Silicon-On-Insulator Wafer* (99% Chip Yield)[R]                                                  |            |      |          |    |           |     | •          | •           |          |         |     |            |        |             |             | •          |

| Edge exclusion (mm) ***                                                                          | 2          |      | 2        |    | 1.5       |     | 1.5        | 1.5         |          | 1.5     |     | 1.5        | 1      | 1.5         |             | 1.5        |

| Starting silicon layer thickness (Partially Depleted) (tolerance $\pm$ 5%, 3 $\sigma$ ) (nm) [L] | 58–100     |      | 53–91    |    | 48–83     |     | 44–76      | 40–70       | 3        | 7–65    |     | 34–60      | 31     | -45         | :           | 29–42      |

| Starting silicon layer thickness (Fully Depleted) (tolerance ± 5%, 3s) (nm) [M]                  | 20–36      |      | 19–34    |    | 18–33     |     | 16–30      | 15–29       | 1        | 5–28    |     | 14–27      | 13     | -15         | ,           | 13–15      |

| Buried oxide (BOX) thickness<br>(Fully Depleted) (tolerance ± 5%, 3s) (nm) [N]                   | 48-80      |      | 42–70    |    | 38–64     |     | 34–56      | 30–50       | 2        | 6–44    |     | 24–40      | 22     | 2–36        | •           | 18–32      |

| D <sub>LASOI</sub> , Large area SOI wafer defects (DRAM) (cm <sup>-2</sup> ) [O]                 | ≤0.011     |      | ≤0.007   |    | ≤0.009    |     | ≤0.014     | ≤0.009      | ≤        | 0.011   |     | ≤0.014     | ≤0     | .014        | <u> </u>    | ≤0.012     |

| D <sub>LASOI</sub> , Large area SOI wafer defects (MPU) (cm <sup>-2</sup> ) [O]                  | ≤0.004     |      | ≤0.005   |    | ≤0.003    |     | ≤0.004     | ≤0.005      | <u> </u> | 0.003   |     | ≤0.004     | ≤0     | .004        |             | ≤0.003     |

| D <sub>SASOI</sub> , Small area SOI wafer defects (DRAM) (cm <sup>-2</sup> ) [P]                 | ≤0.218     |      | ≤0.139   |    | ≤0.170    |     | ≤0.218     | ≤0.138      | <u> </u> | 0.173   |     | ≤0.218     | ≤0     | .139        | 1           | ≤0.173     |

| D <sub>SASOI</sub> , Small area SOI wafer defects (MPU) (cm <sup>-2</sup> ) [P]                  | ≤0.200     |      | ≤0.252   |    | ≤0.159    |     | ≤0.200     | ≤0.252      | <b>S</b> | 0.159   |     | ≤0.200     | ≤0     | .252        | 2           | ≤0.159     |

- \* Parameters define limit values, independent predictors of yield, mathematically or empirically modeled at 99%. limit values rarely coincide for more than one parameter. A given wafer will generally not exhibit more than one limit value "at a time"; other parameter values are most likely near median value, thereby insuring total yield for all parameters is at least 99%.

- \*\* Values expressed in a per wafer format are calculated assuming the maximum stated wafer diameter, although that diameter likely may not be the predominant one for the corresponding technology generation. Although 450 mm is colored yellow indicating manufacturable solutions are know, it could have easily been colored red, because there has been no acceptable economic solution for funding identified by the industry.

- \*\*\* Edge exclusion is repeated in the Silicon on Insulator Wafer section because of inherent limitations associated with certain SOI wafer production techniques that differ from polished and epitaxial wafer edge exclusion capabilities.

| Meaning and Color Coding of Left Box                                            | Meaning and Color Coding of Right Box                   |

|---------------------------------------------------------------------------------|---------------------------------------------------------|

| Technology Requirements Value and Supplier<br>Manufacturing Capability by Color | Metrology Readiness Capability by Color                 |

| Manufacturable solutions exist, and are being optimized                         | Manufacturable solutions exist, and are being optimized |

| Manufacturable solutions are known                                              | Manufacturable solutions are known                      |

| Manufacturable solutions are NOT known                                          | Manufacturable solutions are NOT known                  |

Notes for Table 67a and b

- [A] Surface metals are empirically grouped into three classes <sup>1, 2</sup>(a) Mobile metals that may be easily cleaned such as Na and K and may be modeled by taking the flat-band shift of a capacitance-voltage (CV) test approximately 50 mV for a representative 1 nm EOT; (b) metals that dissolve in silicon or form silicides such as Fe, Ni, Cu, Cr, Co, Al, Zn; and (c) major gate-oxide-integrity (GOI) killers such as Ca. Each of these metals is taken at a maximum value of  $1 \times 10^{10}$ /cm<sup>2</sup> for all subsequent technology generations. The surface concentration of carbon atoms after cleaning is based on the assumption that a 10% (7.3  $\times$  10<sup>13</sup> atoms/cm<sup>2</sup>) carbon atom coverage on a bare silicon (100) surface can be tolerated during device fabrication. Organics/polymers are therefore modeled approximately 0.1 of a monolayer,  $\le 1 \times 10^{14}$ C atoms/cm<sup>2</sup>. Surface organic levels are highly dependent on wafer packaging, on hydrophobic or hydrophilic wafer surface conditions, and on wafer storage conditions such as temperature, time and ambient. Total bulk Fe consistent with recombination lifetime, T<sub>r</sub>, as measured by the SPV technique (for lightly doped p-type material) at low injection level is held at  $1 \times 10^{10}$ /cm<sup>3</sup> for all subsequent technology generations. Note that the bulk Fe concentration (at/cm<sub>3</sub>) cannot be converted to surface concentration (at/cm<sup>2</sup>) via wafer thickness. Recombination lifetime  $\tau_r = (L^2)/D_n$ , where L = minority-carrier diffusion length and  $D_n =$  minority-carrier diffusion coefficient at  $27^{\circ}$ C. The diffusion length is taken equal to the wafer thickness, resulting in a  $\tau_r$  value of 350 µsec. The allowable lifetime is doubled to ensure a sufficient safety factor, resulting in a final value of 700 usec. Appropriate technique(s) to control, stabilize and passivate surface effects is required, depending on the technique (SPV, PCD, etc.), especially for a bulk lifetime greater than 20 µsec. For any technique other than SPV, the injection level must be noted. No oxygen precipitation in sample, no back-side mechanical damage, and resistivity of 5–20 Ohm-cm recommended. [B] Instrumentation choice, target values, and spatial frequency range (scan size) for front-surface microroughness are selected based on application. Power spectral density analysis is recommended to utilize full accessible range of instruments. A typical value for polished wafers is  $\leq 0.1$  nm (RMS) for all CD generations. Epitaxial, annealed and SOI wafers have values that are typically higher than polished wafers while still meeting the user's

- [ $\dot{C}$ ] The oxygen concentration may be specified depending on the particulars of the IC user based on IC process requirements and is generally in the range of 18–31 ppma (SEMI M44-0702, refer to ASTM F121-79). With advanced crystal growth technologies, bulk micro defects (BMDs) can be achieved independent of the interstitial oxygen concentration. The importance of BMDs for gettering has recently again been emphasized and may be especially important in those IC fabrication cases with low thermal budgets. Co-doping techniques (such as nitrogen and carbon) can be used to enhance oxygen precipitation so may be particularly well suited for low thermal budget device processes. Additionally, certain growth methods coupled with heat treatments can also enhance the precipitation of oxygen. Not all device processes, however, require the presence of BMDs. BMDs for internally gettered polished wafers may be generically taken as greater than approximately  $1 \times 10^8/\text{cm}^3$  after IC processing. BMD density is measured using ASTM F-1239.

- [D] Critical front surface particle size =  $K_1F$ ,  $[K_1=1]$  where F is the DRAM half-pitch and is used to calculate required particle densities at the given technology generation. Particle sizes reported in Tables 67a and F are held constant for several generations before being reduced, due to metrology capability. Particle densities are extracted from the conventional Maly Yield Equation  $F(Y) = \exp\left[-(D_PR_P)A_{eff}\right]$ , where  $F(Y) = \exp\left[-(D$

- [E] Detailed back-surface particle information is not included in Table 67, since, in practice, lithography concerns are being met by identifying these defects visually. This perhaps suggests that only large defects are of impact. If desired, the calculations may be made using the following model for back-surface particle size and density. The front-surface height elevation, H, due to a back-surface particle of size, D, under a back-surface film of thickness, T, and a wafer thickness, W, may be expressed as [(xD+xT+W)-(T+W)], which may be reduced to [(xD)-(1-x)T], where x=0.6 is the compression of the particle and back-surface film due to the pressure of the chuck on the wafer. Assuming a front-surface elevation of 2(CD) results in a 100% lithographic printing failure, the back-surface particle size is expressed as: D = [(2/0.6) (F) + (0.4/0.6) (T)], where F and T are expressed in nm. In this model, T may be set equal to 100 nm, for example. Back-surface particles modeled for 99% yield:  $Y = \exp(-D_P R_P A_{eff})$  [7].  $R_P = 1.0$ ,  $A_{eff} = A_{chip}$ × 0.03 × 0.8, where 0.03 corresponds to 3% of the chip area touching the chuck and 0.8 corresponds to 80% of the effective chip area that is degraded by effects of the back-surface particle on the front-surface de-focus effect. Dp, then, represents the density of defects allowable in visible inspection for backside particles. The equation for the "killer" backside particle diameter strongly depends on two assumptions that are process dependent. The first is that a focal plane excursion of 2 CD is required for a 100% assured printing failure. Although a process window this wide may exist in many cases, some tightly specified exposures maybe less tolerant to focal plane deviations. This would lead to a smaller particle becoming a backside killer. The second assumption is that the particles and film are both compressed to 60% of their original dimension. This assumption might not be true if the particle were made of a material much harder than the film or the particle was similar in hardness to silicon and there was no backside film (T=0). Either of these circumstances allows a smaller particle to become a possible backside killer. The backside yield equation assumes that the entire chip is killed by a back-surface particle generating a front-surface focal plane deviation during lithography (the critical particle diameter is that value accordingly used in the equation, or larger). This occurs because a particle with diameter much smaller than the thickness of the wafer may create a bulge on the front surface up to 10 mm in diameter, so a significant portion of the field is out of focus, and the chip does not yield. A mitigating circumstance occurs if the particle is near the die edge, however, since the bulge at the die edge will tend to create only an apparent local tilt in the field that can be accommodated by a scanning stepper leveling system. This gives rise to the 80% effective degraded area.

- [F] The metric for site flatness should be matched to the type of exposure equipment used in leading edge applications, which implies scanning steppers for critical levels. While SFSR may be the most appropriate metric, it has failed to gain appreciable support in the industry. Historical reference to SFQR remains strong and it appears inevitable that this metric will continue to be used in the future. To more closely emulate practical experience of the scanning stepper, the effective site size for local site flatness is being modified to 26 mm × 8 mm accordingly. Full-field steppers with square fields (nominally 22 × 22 mm) may still be utilized for non-critical levels although these are increasingly being phased out. In either case, the metric value is approximately equal to F for dense lines (DRAM half pitch). Partial sites should be included. Also note that flatness metrology requires sufficient spatial resolution to capture topographical features relevant for each technology generation.

- spatial resolution to capture topographical features relevant for each technology generation. [G] OSF density empirically modeled by  $K_3$  (F)  $^{1.42}$ ; F in nm;  $K_3 = 2.75 \times 10^{-3}$ . The utilization of the OSF density relation by extension into technology generation regimes, not envisioned in the original experimental analysis, will require re-assessment. Test at 1100°C, 1 hour wet oxidation, strip oxide/etch;OSF is more difficult to control in n-type material.

- [H] Other epitaxial defects such as hillocks and mounds should also be accounted for, but an appropriate yield model is not available. Accurate segregation based upon defect morphology is also not generally available with today's metrology.

- [I] Desired epitaxial layer thickness tolerance is  $\pm$  4% for a 2 to 10 mm center-point epitaxial layer thickness target value but may be affected on  $p/p^+$  structures due to lack of autodoping suppression via backside film deposition, resulting from incompatibility with 300 mm wafers. In the case of  $p/p^-$  epi, the minimum epi layer thickness is designed to avoid the possible influence of bulk grown-in defects such as COPs; this consideration is less critical for  $p/p^+$  where the COPs are significantly reduced in the  $p^+$  substrate compared to  $p^-$ .

- [J] Large structural epi defects (large area defects > 1  $\mu$ m LSE signal) modeled at 99% yield where  $Y = \exp(-D_{LAD} R_{LAD} A_{chip})$ , where  $R_{LAD} = 1$  and  $A_{chip}$  applies to DRAM and high-performance MPU as appropriate. METROLOGY NOTE: Many current generation scanning surface inspection systems (SSIS) cannot reliably size surface features with LSE signals greater than about 0.5  $\mu$ m due to the light scattering characteristics of these large structural epi defects and the optical design of the tool. Further, a metrology gap clearly exists since production worthy tools are not available that can separate large structural epi defects from other features like large particles as well as identify and count epitaxial stacking faults.

- [K] Small structural epi defects ( $\leq 1 \mu m$  LSE signal) modeled at 99% yield where  $Y = exp(-D_{SF} R_{SF} A_{chip})^6$  where  $R_{SF} = 0.5$  and  $A_{chip}$  applies to DRAM and high-performance MPU as appropriate. Starting Materials uses the DRAM at production and the MPU high-performance MPU areas. METROLOGY NOTE: A metrology gap clearly exists since production worthy tools are not available that can identify and count small structural epi defects.

- [L] The silicon final device layer thickness (partially depleted) is obtained by  $2 \times MPU$  physical gate length (with a range in nominal values of  $\pm$  25%). Range of target value refers to the center point measurement with uniformity to indicate within-wafer maximum positive or negative % deviation from the center value. The final device silicon is less than incoming material due to Si consumption during device fabrication. In the table, the starting material layer thickness is shown. For years 2003 to 2009 it is obtained by adding 10 nm to the lower value in the range and 20 nm to the higher value in the range. After 2009, 10 nm is added to both values in the range in order to translate the device thickness into the starting material thickness. Si loss depends on processing conditions used—it is assumed here that processing parameters are controlled more tightly after 2009. It should be noted that partially depleted silicon on insulator solutions are shown for all years but may generally not be compatible with more aggressively scaled technology generations.

- [M] The silicon final device thickness (fully depleted) is obtained by  $0.4 \times MPU$  physical gate length prior to 2008,  $0.35 \times MPU$  physical gate length 2008 to 2011,  $0.3 \times MPU$  physical gate length at 2012 and thereafter (with a range in nominal values of  $\pm 25\%$ ). Range of target value refers to the center point measurement with uniformity to indicate within-wafer maximum positive or negative % deviation from the center value. The final device silicon is less than incoming material due to consumption during device fabrication. In the table the starting material layer thickness is shown. For years 2003 to 2009 it is obtained by adding 10 nm to the lower value in the range and 20 nm to the higher value in the range. After 2009, 10 nm is added to both values in the range in order to translate the device thickness into the starting material thickness. Si loss depends on processing conditions used—it is assumed here that processing parameters are controlled more tightly after 2009.

- [N] The BOX thickness for fully depleted devices is taken as the  $2 \times MPU$  physical gate length. BOX scales with gate length to help to control short channel effects and heat dissipation. Range in nominal target value of  $\pm 25\%$  allows for trade-off between the BOX and silicon thickness to control short channel effects in the fully depleted SOI devices. NOTE: For partially depleted SOI devices, the BOX thickness has less of a direct impact on device parameters. Considerations of BOX capacitance, circuit heat dissipation, gettering, BOX electrical integrity, SOI wafer manufacturing capabilities, wafer quality and wafer cost have driven the choice of the BOX thickness values. The BOX thickness is expected to remain between 100-200 nm for the timeframe of partially depleted SOI devices.

- [O] Large area SOI (LASOI) wafer defects with yield of 99%;  $Y = \exp(-D_{LASOI} R_{LASOI} A_{chip})$ ,  $^{6}D_{LASOI} = LASOI$  defect density,  $R_{LASOI} = 1.0$  (best present estimate).

[P] Small area SOI (SASOI) wafer defects with yield of 99%;  $Y = \exp(-D_{SASOI} R_{SASOI} A_{eff})$ ,  $^6D_{SASOI} = SASOI$  defect density,  $R_{SASOI} = 0.2$  (best present estimate). Sources of SASOI can include COPs, metal silicides, or local SiO<sub>2</sub> islands in the top silicon layer. These SASOI defects may also be detected by localized light scattering (LLS) measurements.  $^{9}$ ,  $^{10}$ ,  $^{11}$

[Q] Peak-to-valley threshold, 2 mm diameter analysis area. Maximum p-v reading taken as CD/4, based on extrapolation of wafer supplier process capability for 180–90 nm technology generations, plus published data on linewidth distortion for sub-100 nm critical dimensions.

[R] The magnitude of within-wafer variation of various wafer parameters changes over different length scales, depending on the nature of the mechanisms that produce them. The impact on subsequent device manufacturing caused by these variations, which occur at different spatial wavelengths, also depends on the nature of the fab processes and resulting devices. For instance, parameters governed by gas flow and temperature gradient variations, such as CVD layer thickness, typically vary appreciably only over fairly long distances, of the order of millimeters to centimeters. It is often adequate to measure such slowly varying parameters at only a modest number of locations on the wafer, using a metrology tool with a fairly low spatial resolution, in order to control such processes. Other parameters, such as wafer surface topography, vary on multiple length scales with different impacts in the fab. At very large length scale (tens of centimeters), wafer surface height variations are many microns in magnitude (e.g. bow and warp), and can affect various mechanical properties of the wafer. At length scales on the order of one centimeter, the surface variations are fractions of a micron in height. These variations (i.e. site flatness) generally are not critical to mechanical shape of the wafer, but are vital to depth of focus in lithography. At still smaller length scales of a few millimeters or less, the surface height variations are on the order of tens of nanometers high. They do not cause focus failures in lithography, but can produce line width variations in gate lengths and polishing removal uniformity problems in CMP. On the length scale of microns, surface roughness variations are of the order of Angstroms, but can cause gate oxide integrity problems. As another example, in fully depleted SOI wafers, thickness variations of the top silicon layer can cause transistor threshold voltage variation die-to-die (at centimeter length scale), within-die (at millimeter length scale), and conceivably, even transistor-to-transistor (on a sub-micron scale). To control parameter variations across a large range of spatial wavelengths requires a tool capable of measuring the whole wafer to capture long wavelength components, but with a very high density of data points (with correspondingly small sampled area) to capture small wavelength components. The spatial wavelength requirements thus have a profound effect on metrology capability. Methods that work well at long spatial wavelengths may become unsuitable at small spatial wavelengths due to measurement throughput limitations and/or inadequate spatial resolution. Metrology grades in this table reflect current spatial wavelength requirements. Future process and device developments that demand measurement at shorter spatial wavelengths may alter these capability grades in unforeseen ways.

Table 67b Starting Materials Technology Requirements—Long-term Years

| Year of Production                                                                               | 2014         |     | 2015           | 2016           | 2017         | 7      | 2018          | 2019             | 2020           |              |

|--------------------------------------------------------------------------------------------------|--------------|-----|----------------|----------------|--------------|--------|---------------|------------------|----------------|--------------|

| DRAM ½ Pitch (nm) (contacted)                                                                    | 28           |     | 25             | 22             | 20           |        | 18            | 16               | 14             | D ½          |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)(contacted)                                                    | 28           |     | 25             | 22             | 20           |        | 18            | 16               | 14             | M            |

| MPU Physical Gate Length (nm)                                                                    | 11           |     | 10             | 9              | 8            |        | 7             | 6                | 6              | M            |

| DRAM Total Chip Area (mm²)                                                                       | 74           |     | 117            | 93             | 74           |        | 117           | 93               | 74             | D 1/2        |

| DRAM Active Transistor Area (mm²)                                                                | 23.1         |     | 36.7           | 28.6           | 23.1         |        | 36.7          | 29.1             | 19.6           | D 1/2        |

| MPU High-Performance Total Chip Area (mm²)                                                       | 246          |     | 195            | 310            | 246          | i      | 195           | 310              | 246            | M            |

| MPU High-Performance<br>Active Transistor Area (mm2)                                             | 25.1         |     | 20.0           | 31.7           | 25.1         |        | 20.0          | 31.7             | 25.1           | М            |

| General Characteristics * (99% Chip Yield) [A, B, C]                                             |              |     |                |                |              |        |               |                  |                |              |

| Maximum Substrate Diameter (mm)—High-volume<br>Production (>20K wafer starts per month)**        | 450          |     | 450            | 450            | 450          |        | 450           | 450              | 450            | D ½, M       |

| Edge exclusion (mm)                                                                              | 1.5          |     | 1.5            | 1.5            | 1.5          |        | 1.5           | 1.5              | 1.5            | D ½, M       |

| Front surface particle size (nm), latex sphere equivalent [D][E]                                 | ≥45          |     | ≥32            | ≥32            | ≥32          |        | ≥22           | ≥22              | ≥22            | D ½, M       |

| Particles (cm <sup>-2</sup> )                                                                    | ≤0.17        |     | ≤0.17          | ≤0.17          | ≤0.17        |        | ≤0.18         | ≤0.18            | ≤0.21          | D ½          |

| Particles (#/wafer)                                                                              | ≤271         |     | ≤268           | ≤261           | ≤268         |        | ≤283          | ≤283             | ≤233           | D ½          |

| Site flatness (nm), SFQR 26 mm × 8 mm site size [F, R]                                           | ≤28          |     | ≤25            | <u>≤22</u>     | ≤20          | _      | ≤18           | <u>≤16</u>       | <u>≤14</u>     | D ½, M       |

| Nanotopography, p-v, 2 mm diameter analysis area [Q]                                             | ≤7           |     | ≤6             | ≤6             | ≤5           |        | ≤4            | <u>≤4</u>        | <u>≤4</u>      | M            |

| Polished Wafer * (99% Chip Yield)                                                                |              |     |                |                |              |        |               |                  |                |              |

| The LLS requirement is specified for particles only; discr                                       | rimination b | etv | veen particle  | es and COPs i  | is required  | (see ( | General Cha   | racteristics) [I | D, <i>E]</i>   |              |

| Oxidation stacking faults (OSF) (DRAM) (cm <sup>-2</sup> ) [G]                                   | ≤0.32        |     | ≤0.27          | ≤0.22          | ≤0.19        |        | ≤0.16         | ≤0.14            | ≤0.12          | D ½          |

| Oxidation stacking faults (OSF) (MPU) (cm <sup>-2</sup> ) [G]                                    | ≤0.09        |     | ≤0.07          | ≤0.06          | ≤0.05        |        | ≤0.04         | ≤0.04            | ≤0.03          | М            |

| Epitaxial Wafer * (99% Chip Yield)                                                               |              |     |                |                |              |        |               |                  |                |              |

| Total allowable front surface defect density is the sum of                                       | epitaxial la | rge | e structural d | defects, small | structural d | lefeci | ts and partic | les (see Gener   | al Characteris | tics) [H, I] |

| Large structural epi defects (DRAM) (cm <sup>-2</sup> ) [J]                                      | ≤0.014       |     | ≤0.009         | ≤0.011         | ≤0.014       | Ţ      | ≤0.009        | ≤0.011           | ≤0.014         | D ½          |

| Large structural epi defects (MPU) (cm <sup>-2</sup> ) [J]                                       | ≤0.004       |     | ≤0.005         | ≤0.003         | ≤0.004       | ı      | ≤0.005        | ≤0.003           | ≤0.004         | М            |

| Small structural epi defects (DRAM) (cm <sup>-2</sup> ) [K]                                      | ≤0.027       |     | ≤0.017         | ≤0.022         | ≤0.027       | 7      | ≤0.017        | ≤0.022           | ≤0.027         | D ½          |

| Small structural epi defects (MPU) (cm <sup>-2</sup> ) [K]                                       | ≤0.008       |     | ≤0.010         | ≤0.006         | ≤0.008       | 3      | ≤0.010        | ≤0.006           | ≤0.008         | М            |

| Silicon-On-Insulator Wafer* (99% Chip Yield)[R]                                                  |              |     |                |                |              |        |               |                  |                | •            |

| Edge exclusion (mm) ***                                                                          | 1.5          |     | 1.5            | 1.5            | 1.5          |        | 1.5           | 1.5              | 1.5            | M            |

| Starting silicon layer thickness (Partially Depleted) (tolerance $\pm$ 5%, 3 $\sigma$ ) (nm) [L] | 27–38        |     | 25–35          | 23–32          | 22–30        |        | 21–28         | 19–26            | 18–24          | М            |

| Starting silicon layer thickness (Fully Depleted) (tolerance ± 5%, 3s) (nm) [M]                  | 13–14        |     | 12–14          | 12–13          | 12–13        |        | 12–13         | 11–12            | 11–12          | М            |

| Buried oxide (BOX) thickness (Fully Depleted) (tolerance ± 5%, 3s) (nm) [N]                      | 16–28        |     | 16–26          | 14–22          | 12–20        |        | 10–18         | 10–16            | 8–14           | М            |

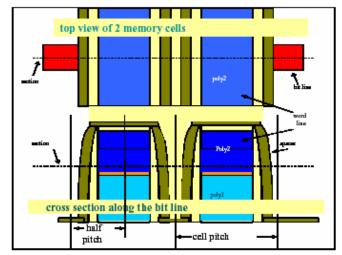

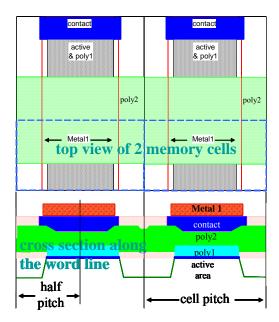

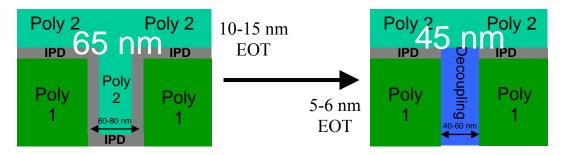

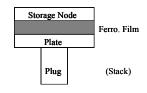

| D <sub>LASOI</sub> , Large area SOI wafer defects (DRAM) (cm <sup>-2</sup> ) [O]                 | ≤0.014       |     | ≤0.012         | ≤0.011         | ≤0.007       | -      | ≤0.009        | ≤0.009           | ≤0.009         | D ½          |