# INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS

# 2005 Edition

# TEST AND TEST EQUIPMENT

THE ITRS IS DEVISED AND INTENDED FOR TECHNOLOGY ASSESSMENT ONLY AND IS WITHOUT REGARD TO ANY COMMERCIAL CONSIDERATIONS PERTAINING TO INDIVIDUAL PRODUCTS OR EQUIPMENT.

## TABLE OF CONTENTS

| Introduction and Scope of the 2005 edition<br>Key Drivers, Difficult Challenges, and Future Opportunities |    |

|-----------------------------------------------------------------------------------------------------------|----|

| Key Drivers                                                                                               | 3  |

| Device Trends                                                                                             |    |

| Increasing Test Process Complexities                                                                      |    |

| Continued Economic Scaling of Test                                                                        | 4  |

| Difficult Challenges (in priority order)                                                                  | 5  |

| (1) Test For Yield Learning (summary)                                                                     |    |

| (2) Screening For Reliability                                                                             |    |

| (3) Increasing Systemic Defects                                                                           |    |

| (4) Potential Yield Losses                                                                                | 7  |

| Future Opportunities                                                                                      | 8  |

| Test Program Automation (not ATPG)                                                                        |    |

| Simulation and Modeling                                                                                   |    |

| Convergence of Test and System Reliability Solutions                                                      |    |

| Test For Yield Learning Focus Topic                                                                       |    |

| Physical Failure Analysis (PFA)                                                                           |    |

| Software-Based Diagnosis and Signature Analysis                                                           |    |

|                                                                                                           |    |

| Manufacturing Test Cost Focus Topic<br>Base Cost Trend                                                    | 10 |

| Channel Cost Trend                                                                                        |    |

| Power Cost Trend                                                                                          |    |

| Interface Cost Trend                                                                                      |    |

| Multi-site Trend                                                                                          |    |

| Other Cost Trends                                                                                         |    |

| Important Areas of Concern                                                                                |    |

| Test Technology Requirements                                                                              |    |

| Introduction                                                                                              |    |

| System Integration—SOC and SIP Test Challenges and Implications                                           | 18 |

| System on a Chip                                                                                          |    |

| System in a Package                                                                                       |    |

| Logic                                                                                                     |    |

| High Volume Microprocessor Trends Drivers                                                                 |    |

| System Trends Drivers                                                                                     |    |

| DFT Trends Drivers                                                                                        |    |

| High Volume Microprocessor Test Requirements                                                              |    |

| Important Areas of Concern                                                                                |    |

| High Speed Input/Output Interface                                                                         |    |

| Important Areas of Concern                                                                                |    |

|                                                                                                           |    |

| Memory<br>Commodity Dram Testing                                                                          | 31 |

| Commodity Flash Testing                                                                                   |    |

| Embedded Dram and Flash Testing                                                                           |    |

|                                                                                                           |    |

| Analog and Mixed-signal                                                                                   | 36 |

| Important Areas of Concern                      | 37 |

|-------------------------------------------------|----|

| Radio Frequency                                 | 40 |

| Important Areas of Concern                      | 40 |

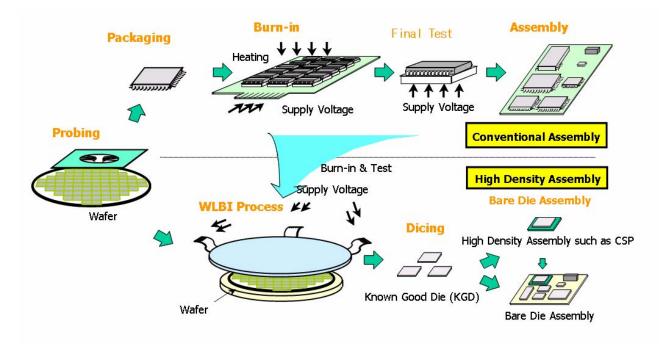

| Reliability Technology Requirements             | 40 |

| Burn-In Requirements                            | 42 |

| Wafer Level Burn-in                             | 42 |

| Test Handler and Prober Technology Requirements | 47 |

| Device Interface Technology Requirements        | 52 |

| Probe Cards                                     | 52 |

| Trends Affecting Probe Card Technologies        | 52 |

| Probe Card Technology Requirements              | 53 |

| Pitch and Interconnect Deformation              | 54 |

| Multi-DUT                                       | 55 |

| Electrical Performance                          | 55 |

| Thermal Performance                             | 55 |

| Unit Cost and Cost of Ownership                 | 55 |

| Lead-Time                                       |    |

| Cleaning                                        | 56 |

| Test Sockets                                    | 60 |

| Electrical Requirements                         | 60 |

| Mechanical Requirements                         | 61 |

## LIST OF FIGURES

| Figure 28 | Test Cost Drivers                                                                            | .11 |

|-----------|----------------------------------------------------------------------------------------------|-----|

| Figure 30 | Channel Cost Range Trends for Product Segments                                               | .12 |

| Figure 31 | Test Cell Cost / Unit vs. Interface Cost Trend                                               | .13 |

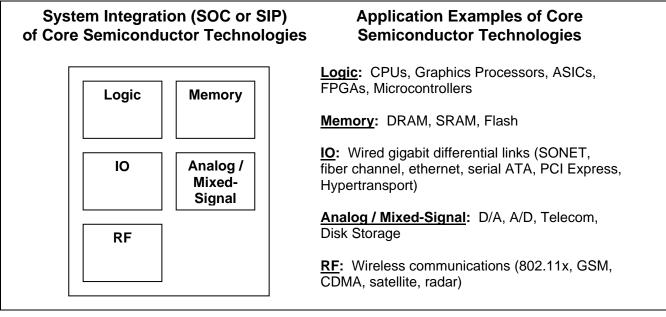

| <b>U</b>  | Organization of Core Semiconductor Technologies from System Integration and s Points of View | .18 |

| Figure 33 | The Production Process with WLBI Compared with Package Burn-in                               | .43 |

## LIST OF TABLES

| Table 22  | Summary of Key Test Drivers, Challenges, and Opportunities2                 |

|-----------|-----------------------------------------------------------------------------|

| Table 23a | Multi-site Wafer Test (Package Test) for Product Segments—Near-term Years15 |

| Table 23b | Multi-site Wafer Test (Package Test) for Product Segments—Long-term Years16 |

| Table 24  | SOC Model19                                                                 |

| Table 25a | System on Chip Test Requirements—Near-term Years                            |

| Table 25b | System on Chip Test Requirements—Long-term Years22                          |

| Table 26a | Logic Test Requirements—Near-term Years27                                   |

| Table 26b | Logic Test Requirements—Long-term Years28                                   |

| Table 27a | Commodity DRAM Test Requirements—Near-term Years                            |

| Table 27b | Commodity DRAM Test Requirements—Long-term Years                            |

| Table 28a | Commodity Flash Memory Test Requirements—Near-term Years                    |

| Table 28b | Commodity Flash Memory Test Requirements—Long-term Years                    |

| Table 29a | Embedded Memory (DRAM and Flash) Test Requirements—Near-term Years35        |

| Table 29b | Embedded Memory (DRAM and Flash) Test Requirements—Long-term Years36        |

| Table 30a | Mixed-signal Test Requirements—Near-term Years                              |

| Table 30b | Mixed-signal Test Requirements—Long-term Years                              |

| Table 31a | Burn-in Requirements—Near-term Years45                                      |

| Table 31b | Burn-in Requirements—Long-term Years46                                      |

| Table 32a | Handler (Memory—Pick and Place) Requirements—Near-term Years47              |

| Table 32b | Handler (Memory—Pick and Place) Requirements—Long-term Years48              |

| Table 33a | Handler (Logic—Pick and Place) Requirements—Near-term Years49               |

| Table 33b | Handler (Logic—Pick and Place) Requirements—Long-term Years                 |

| Table 34a | Handler (Network and Communications—Pick and Place)—Near-term Years50       |

| Table 34b | Handler (Network and Communications—Pick and Place)—Long-term Years50       |

| Table 35a | Prober (Logic MPU—Pick and Place) Requirements—Near-term Years51            |

| Table 35b | Prober (Logic MPU—Pick and Place) Requirements—Long-term Years51            |

| Table 36  | Test Handler and Prober Difficult Challenges                                |

| Table 37  | Probe Card Difficult Challenges—Near-term Years54                           |

| Table 38a | Wafer Probe Technology Requirements—Near-term Years57                       |

| Table 38b | Wafer Probe Technology Requirements—Long-term Years                         |

# **TEST AND TEST EQUIPMENT**

## INTRODUCTION AND SCOPE OF THE 2005 EDITION

The 2005 Test Roadmap has undergone substantial evolution since the 2003 edition. Most significant is the reorganization of the Test Technology Requirements section to better reflect the reality of increasing integration of previously disparate chip designs. Looking forward over the ITRS horizon, each device under test (DUT) could be considered a system-on-a-chip (SOC) or system-in-package (SIP) containing one or more of the following "cores": logic, I/O, memory, analog, RF, etc., each with unique test requirements. The revamped Test Technology Requirements section opens with an overview of these SOC/SIP test challenges including the introduction of a generic SOC model and continues with sections dedicated to the test requirements and challenges for each type of core.

There have also been some notable additions, deletions, and consolidations from previous years. The microprocessor, ASIC and microcontroller test requirements sections have been consolidated into a single logic test requirements section. New sections this year are radio frequency (RF) Testing and Test Sockets. Also, the design for test (DFT) Tester Requirements section has been removed from this year's edition. This is not to imply any diminished importance for DFT or low-cost test solutions for devices that depend heavily on DFT to meet high volume manufacturing test requirements. On the contrary, DFT advancements and low-cost test solutions will be essential to hold the line on test costs. The dilemma is these test solutions must be more flexible than ever to accommodate the aforementioned integration trends and the emergence of new cores such as RF that are driving new test capabilities. For this reason, the DFT implications and test challenges will be addressed throughout the chapter and on a core technology basis

The previous revision in 2003 noted the beginning of a significant shift from traditional test equipment architectures to "universal slot" architectures with high levels of test instrument encapsulation and modularity. This trend continues to unfold in various forms. Most major test equipment suppliers are looking to leverage design modularity wherever possible, with implementations ranging from modular architectures that span multiple test equipment architectures within a single test equipment supplier to open architectures that aim to enable the ability to mix and match test instruments from multiple suppliers into a single tester hardware and software environment. Given this generic trend, semiconductor manufacturers will have more options and greater flexibility than ever before to tailor their test equipment solutions to their testing needs and this provides even more impetus for reorganizing the test requirements in this year's roadmap revision around different semiconductor technology cores that can be integrated together in a myriad of different ways as opposed to a handful of market segments.

This document represents significant contributions from a wide cross-section of the industry as noted in the acknowledgements; however, the Test Technology Working Group is always looking for additional participation—please contact the working group chair if you have interest in participating!

## KEY DRIVERS, DIFFICULT CHALLENGES, AND FUTURE OPPORTUNITIES

Beginning with this 2005 edition of the ITRS Test Chapter, the working group members re-organized this important section of the test chapter. The key change is to split the previous Difficult Challenges section into Key Drivers and Difficult Challenges, as well as add a Future Opportunities section. This split will distinguish the drivers, that is, primary boundary conditions that define the scope of solutions for upcoming manufacturing test for semiconductor components, from key technical and business challenges. At a high level, these boundary conditions actually represent expectations or even requirements of the test process, while the challenges represent current and upcoming key roadblocks, strategic inflection points, and opportunities for the future

For many years, the mission of semiconductor manufacturing test has been described as "screening defects" and to a lesser extent or within certain business segments "speed binning" or "speed classification." It is interesting to note that some of the most important test challenges are now actually centered on some of the more subtle historical missions of manufacturing test—reliability and yield learning. It is also important to note that the impact of these challenges affect not only on the manufacturing test process itself, but are essential to entire semiconductor business, both in terms of enabling the cadence or timely delivery of future processes and cost effective products, but also in terms of meeting customer expectations for reliability.

Within the Difficult Challenges section, the challenges are listed in order of perceived importance or priority, for example, test for yield learning followed by screening for reliability followed by increasing systemic defects. In contrast, there is no specific intent in the ordering of the Key Drivers, whereas they are all boundary conditions or requirements that the semiconductor test solutions must meet. Table 22 summarizes all of the key test drivers, challenges and opportunities.

| KEY DRIVERS (NOT IN ANY PARTICU                      | LAR ORDER)                                                                                                                                    |  |  |  |  |  |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                                      | Increasing device interface bandwidth (both number of signals and signal data rates)                                                          |  |  |  |  |  |

|                                                      | <ul> <li>Increasing device integration (SOC, SIP, MCP, 3D packaging)</li> </ul>                                                               |  |  |  |  |  |

| Device trends                                        | <ul> <li>Integration of emerging and non-digital CMOS technologies (RF, Analog, Optical, MEMs)</li> </ul>                                     |  |  |  |  |  |

| Device trends                                        | <ul> <li>Package form factor and electrical / mechanical characteristics</li> </ul>                                                           |  |  |  |  |  |

|                                                      | <ul> <li>Device characteristics beyond one sided deterministic stimulus/response model</li> </ul>                                             |  |  |  |  |  |

|                                                      |                                                                                                                                               |  |  |  |  |  |

|                                                      |                                                                                                                                               |  |  |  |  |  |

| Increasing test process complexity                   |                                                                                                                                               |  |  |  |  |  |

| increasing test process complexity                   | Increased data feedback for tuning manufacturing                                                                                              |  |  |  |  |  |

|                                                      | • Higher order dimensionality of test conditions (e.g., adding multi-power, multi-voltage, multi-freq topologies to single valued T, V, freq) |  |  |  |  |  |

|                                                      | Physical limits of further test parallelism                                                                                                   |  |  |  |  |  |

|                                                      | Managing (logic) test data volume                                                                                                             |  |  |  |  |  |

| Continued economic scaling of test                   | Effective limit for speed difference of HVM ATE versus DUT                                                                                    |  |  |  |  |  |

|                                                      | Acceptable increases for interface hardware and (test) socket costs                                                                           |  |  |  |  |  |

|                                                      | • Trade-off between the cost of test and the cost of quality                                                                                  |  |  |  |  |  |

| DIFFICULT CHALLENGES (IN ORDER                       | R OF PRIORITY)                                                                                                                                |  |  |  |  |  |

| Test for yield learning                              | Critically essential for fab process and device learning below optical device dimensions                                                      |  |  |  |  |  |

|                                                      | Increasing implementation challenges and efficacies of burn-in, IDDQ, and Vstress                                                             |  |  |  |  |  |

| Screening for reliability                            | • Erratic, non deterministic, and intermittent device behavior                                                                                |  |  |  |  |  |

|                                                      | Testing for local non-uniformities, not just hard defects                                                                                     |  |  |  |  |  |

| Increasing systemic defects                          | • Detecting symptoms and effects of line width variations, finite dopant distributions, systemic process defects                              |  |  |  |  |  |

|                                                      | • Tester inaccuracies (timing, voltage, current, temperature control, etc)                                                                    |  |  |  |  |  |

|                                                      | • Overtesting (e.g., delay faults on non-functional paths)                                                                                    |  |  |  |  |  |

|                                                      | Mechanical damage during the testing process                                                                                                  |  |  |  |  |  |

| Potential yield losses                               | Defects occurring in test-only circuitry, e.g., BIST                                                                                          |  |  |  |  |  |

|                                                      | Some IDDQ-only failures                                                                                                                       |  |  |  |  |  |

|                                                      | • Faulty repairs of normally repairable circuits                                                                                              |  |  |  |  |  |

|                                                      | Overly aggressive statistical post-processing                                                                                                 |  |  |  |  |  |

| FUTURE OPPORTUNITIES (NOT IN A                       | NY ORDER)                                                                                                                                     |  |  |  |  |  |

| Test program automation (not ATPG)                   | Automation of generation entire test programs for ATEs                                                                                        |  |  |  |  |  |

| Simulation and modeling                              | Simulation and modeling of test interface hardware and instrumentation seamlessly integrated to the device design process                     |  |  |  |  |  |

| Convergence of test and system reliability solutions | Re-use and fungability of solutions between test (DFT), device, and system reliability (error detection, reporting, correction)               |  |  |  |  |  |

| ATE—automatic test equipment AT                      | PG—automatic test pattern generation BIST—built-in self test HVM—high volume manufacturing                                                    |  |  |  |  |  |

Table 22 Summary of Key Test Drivers, Challenges, and Opportunities

ATE—automatic test equipment

ATPG—automatic test pattern generation

MCP—multi-chip packaging

MEMs—micro-electromechanical systems

BIST—built-in self test HVM—high volume manufacturing

## **KEY DRIVERS**

As previously mentioned, the Key Drivers in the Test chapter are considered *boundary conditions* within which the semiconductor test function must operate within and still deliver acceptable component quality and reliability at continued test cost scaling.

#### **DEVICE TRENDS**

- Device Interface Bandwidth—In the 2001 edition of the ITRS Roadmap, a change in direction was denoted to deliver increasing system performance with rapidly increasing (compared to previous trends) component I/O speeds. In the 2003 and 2005 editions, the Test working group noted that while the speeds are not climbing as rapidly as the 2001 predictions, the penetration of Gb/s interfaces is permeating throughout a wider spectrum of the semiconductor component market segments (memories, CPUs, chipsets, etc.). High speed serial and differential I/O protocols will continue to rise in speed and continue to force innovation in the DFT and HVM test processes to maintain continued cost scaling

- Increasing Device Integration—SOC and SIP integration continue to rise in prevalence throughout a number of business segments. Increased device integration forces a re-integration of test solutions to maintain scaling of test costs and product quality. The optimized test solutions for stand-alone RAMs, cores, and other blocks typically do not scale linearly without modification, additional DFT, or new partitioning in the integrated device test solutions. In particular, additional DFT in die or even in-package may be required to provide access to and testing of embedded blocks or cores, or additional distribution or re-integration of the HVM test instrumentation may be required. Techniques for known good die (KGD) that provide high quality dice for multi-die packaging also become very important and an essential part of the test techniques and cost trade-offs.

- Integration of Emerging and Non-Digital CMOS Technologies—In the recent past, mixed signal device circuits have been increasingly delivered on die integrated to digital CMOS, posing key challenges for ATE, instrumentation, and test manufacturing flow integration choices. It also poses new challenges and opportunities for DFT innovation, where it had not been previously prevalent (as it had in digital logic and memories). Integration of RF circuits is already starting to make a similar rise, as are more radically different types of semiconductor devices, e.g., MEMs which are already showing up in integrated forms, and optical, which are just around the corner from integration to larger CMOS digital die. As in previous types of integration, the test mission for these devices revolve around access to potentially embedded blocks and integration of radically different test methods into a cost effect manufacturing process.

- Package Form Factor and Electro-Mechanical and Thermal Characteristics—The envelope of package form factors is pushing both outward and inward, with higher complexity form factors in MCP and SIP for multi-die on the high end, but also chip scale packaging pushing towards the small end for systems targeted for the smallest platform form factors (e.g., handhelds). In addition, multi-functionality of die packaging with inclusion of heat sinks and spreaders, and perhaps even voltage regulation and power management functionalities, appears to be on the increase. With increasing power a major concern, form factor thermal transfer characteristics and uniformities (thermal gradient coefficient-junction to ambient, junction to case [theta-JA, theta-JC], etc.) become even more critical to the test process. These expansions of the form factor technology envelopes necessitate improvements and delivery of key test sub-systems: handling for packaging test, Ohmic contacting technologies, and test sockets (the later described later in the chapter for the first time).

- Device Characteristics Beyond One-Sided Stimulus Response Model—The history of semiconductor testing and ATE architecture and usage is built upon a foundation of deterministic device behavior. In addition, digital CMOS testing has historically been based on simplifying the environmental topologies of V<sub>cc</sub>, temperature, and frequency, so that worst case (one-sided), one iteration tests guaranteed the performance over a wider and continuous range of environment topologies. When these topologies were only two or even three variables, they were manageable, and fairly easy to characterize, and to optimize for HVM test. However, a number of device characteristics threaten the dimensionality of this one-sided test paradigm, threatening a non-linear effect on non-recurring engineering (NRE) development costs for test as well as potentially limiting continued test cost scaling for HVM. Device features such as extended self-repair and correction, and built-in variable, and multi-power management modes all potentially add tremendous complexities to the device test conditions contour. In addition, from the device design, architecture, and behavior front, their looms the increasing future possibility of non-deterministic device behaviors (e.g., asynchronous logic architectures) where correct device behavior (from end user system standpoint) from die to die under similar

conditions is not deterministic (within the time/vector synchronization standpoint). These behaviors, while correct from an end use customer and system standpoint would break the historical HVM test stimulus-response model, where one set of digital logic 1s and 0s delivered on the same synchronization, would not suffice to test such behaviors. While these device architectures and behaviors are not widely prevalent today, they do pose a major paradigm shift, or innovation challenge for the semiconductor test process in the not too distant future.

#### **INCREASING TEST PROCESS COMPLEXITIES**

- Increased Device Customization and Line Item Complexity (during the test process)—Increasingly, the test process is expanding to include not only the metrologies surrounding the question "is this a good die?" but also actual process steps that modify, differentiate, or customize specific die. Examples of these include memory block (and other) redundancy/repair, laser marks, burning of on die fuses or read-only memories (ROMs), or other programming of product features. In addition, some business segments are seeing substantial increases in product line items derived from the same die base, with differentiation and physical segregation as part of the manufacturing test flow increasing. All of this places increasing demand on the manufacturing test process and expands equipment (e.g., handling, fuse blowing, etc.) and factory automation and integration infrastructures.

- Increased "Distributed" Test to Maintain Cost Scaling—Distribution of test content and manufacturing instrumentation and equipment platform requirements enabled by a wider application of DFT techniques will continue to be a widespread industrial test process integration scheme used to optimize test manufacturing capital expenditures, operational test cost, and outgoing product quality. Distribution and differentiation of differentiation will center around the speed, accuracy, number and types of channels on verification versus manufacturing tools. Integration of a wider array of digital CMOS circuits, mixed signal and even optical and or mechanical silicon together in future products will continue to make distributed test solutions attractive rather than to increase the platform complexity of ATEs back towards a "do all" platform, at least for manufacturing test. Hand in hand with this will be increases in the complexity (number of steps and interactions) within the manufacturing test process flow itself.

- Increased Test Data Feedback to Tune Manufacturing—Test data usage for purposes beyond identifying whether a given die is good or defective has become essential for several reasons and drives a need for expanded, revamped, and better integrated test data systems and infrastructure. In one sense the output of the component test process is data, i.e., the results of the various applied metrologies of the test process across the product dice and manufacturing lot populations. The need for better integrated usage of this test output (data) for fab process yield learning, maverick material identification, and feedback within a more distributed manufacturing test are all becoming more critical and even essential applications moving forward, not just nice to haves,

- Higher Order Dimensionality of Test Conditions—Historically, component manufacturing test has used testing at a simple matrix of points or corner conditions of two or three environmental variables (typically Voltage, Temperature, and Frequency) to guarantee the wider multi-dimension contour and interior space of product specifications beyond the contour outlined by the test points. Components in a broad range of markets from battery application platforms to client computing and servers are adding numerous schemes of power management that quickly adds exponential complexity to the worst-case test conditions contour. For example, the complexities of component schemes may include multiple or variable power modes (sleep, hibernation, etc) or even multiple and in situ responsive variable Vcc and frequency control systems to achieve optimized powerperformance in the application. The challenge of determining, characterizing, and optimizing (reducing) the larger set of environmental test points for component manufacturing test is daunting with the additional dimensions of these variables. Keeping pace with this complexity requires additional validation efforts and innovative methods to validate the quality of the more complex environmental test points. This is needed to ensure the lack of holes and predictability of more complex worst case conditions in the product test validation and test development phase. This increased complexity of test environment set points will also challenge the continued economic scaling for manufacturing test for test costs by the product of the applied test content and the number of iterations of its applications at the various set points in the manufacturing flow.

#### **CONTINUED ECONOMIC SCALING OF TEST**

• *Physical Limits of Further Parallelism*—Over recent generations, continued increases in parallelism (in number of DUTs tested in parallel at a test insertion), particularly for commodity memories, but also for digital logic,

THE INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS: 2005

have been a primary means of continuing the economic scaling of test in the context of devices with more transistors, increased functionality, and higher I/O and core speeds. In the current test tool and interface hardware integration paradigms, further increases in DUT test parallelism will be reaching non-linear limits in the next one to two generations. These are driven by the practical limits of how many electrical channels can be squeezed into the physical space between the parallel DUTs and the test instrumentation while yet maintaining acceptable physical and electrical proximities between the two. These approaching physical limits will require alternate means be used or expanded in order to maintain continued economic scaling of test, or alternately, new paradigms of DUT, handling, contacting, and test instrumentation integration be developed that enable further increases in DUT parallelism beyond what is currently envisioned

- Managing (Digital Logic) Test Data Volume—Unconstrained, increased digital logic die complexity and content drives proportional increases on the test data volume (number and width of vectors). Unconstrained, this additional test data volume drives increases in test capital and operational costs by requiring additional vector memory depth per digital channel of the test tools (ATEs) and by increasing test time per DUT. Currently, a number of logic test vector compression schemes are being developed and applied in a variety of ways, e.g., on the test databases themselves (for scan based tests) or via compression hardware (DFT) on the product die itself. Moving forward, compression will become more ubiquitous across component business segments, driven by the increasing product complexities and higher levels of product integration (e.g., SOCs, SIPs) and may ultimately require increases in the rate of compression (i.e. the compression ratio of the test database versus uncompressed).

- Effective Limit for Speed Difference of HVM ATE versus DUT—In recent years, a primary means of achieving economic scaling of test has been an increasing gap between application device speed versus manufacturing test instrumentation and applied test. This is one key aspect of distributed test, or test partitioning, and is enabled by a variety of DFT techniques such as I/O loopback and special test modes on the DUT. Maintaining this delta between application speed and design verification ATEs versus HVM manufacturing ATEs enables a continued economic scaling for test, but there are limits to how much slower or how much less accuracy (e.g., for signal edge placement) is needed in combination with DFT to assure adequate quality of DUT in the end user customer application. As device speeds and I/O edge rates increase, the manufacturing test instrumentation will lag but will also need to slowly increase, but probably in larger step function increments than the DUT families themselves, as opportunities for ATE fleet replacements or expansions offer the most optimal opportunities to keep abreast in cost and quality effectiveness.

- Acceptable Increases for Interface Hardware and (test) Socket Costs—The portion of costs based on test and probe interface hardware and test sockets is an increasing proportion of the overall test cost. There are a number of factors driving this, such as higher speed (GB/s) and more complex DUT I/O protocols, increased DUT parallelism, higher signal and power pin counts, and increased power delivery and signal channel fidelity requirements. While this might be an alarming trend by itself, this trend needs to be considered in the context of the overall test process cost, and whether or not it enables a continued overall economic scaling of manufacturing test. Keeping these proportional increases of interface hardware costs within an acceptable range may also be dependent on technology drivers and boundary conditions, e.g., the continued extension of the use of FR<sub>4</sub> materials within an acceptable numbers of layers as the primary materials platform for such hardware

#### DIFFICULT CHALLENGES (IN PRIORITY ORDER)

#### (1) TEST FOR YIELD LEARNING (SUMMARY)

Test's peripheral role as a feedback loop for understanding underlying defect mechanisms, process marginalities, and as an enabler for rapid fab process yield learning and improvement has traditionally been considered a secondary role to screening hard defects. With the increasing reduction in feature (and defect) sizes well below optical wavelengths, rapidly increasing failure analysis throughput times, reduction in failure analysis efficacy, and approaching practical physical limits to other physical techniques (pica, laser probes), the industry is reaching a strategic inflection point for the semiconductor business where the criticality of DFT and test enabled diagnostics and yield learning becomes paramount. In other words, the yield learning rates of the past per process generations are not sustainable by historical fault isolation and failure analysis methods per se. Rather, they need to be augmented by more universal deployment of enabling on die circuitry (DFT, etc.) across and throughout products, as well as improvements in the on-die instrumentation and diagnostic software tools with respect to fault isolation specificity. Where it may have been sufficient to isolate to failing bit in an array or failing gate in logic in the past, there is a real business need to be able to isolate electrically to at least the failing transistor or interconnect in the future, or suffer the economic consequences of reduced yield improvement

learning rates on new process technologies, perhaps even to the point of lowering the asymptotic maximum achievable yields per die size on future processes. Given the paramount importance of this "mission" for component test, the Test team has not only summarized its relevance here as the top challenge for test, but also included a detailed section on this topic in the early part of the test chapter.

### (2) SCREENING FOR RELIABILITY

A lesser-publicized mission for semiconductor test beyond the primary "screening defects" or telling a good part from a bad one, has been to screen out infant mortality reliability of the product population to acceptable levels. Another way of describing it more aligned to the "defect" mission of Test is to call this essential function "screening t > 0 defects" where "0" on the timeline represents the date product moves to the customer from the component provider. Historically, different semiconductor business segments have used a variety of techniques from burn-in to IDDQ, to voltage stressing during the manufacturing process to identify and screen sufficient numbers of the less reliable sub-populations or product dice to meet customer quality expectations. From a similar set of causes, notably increasing background leakage currents, and reduced product operationally margin (collapsing  $V_{dd}/V_{cc}$  with process scaling), all of these techniques are becoming both less effective and more expensive to varying degrees. Where burn-in equipment and techniques had remained essentially unchanged and re-used over many process generations from the early 80s to the mid 90s, beginning in the late 90s burn-in production systems (in product segments that leverage this technique) have been one of the areas of the largest increases in test capital and interface hardware costs. At the burn-in elevated voltage and temperatures (needed to accelerate latest defects) leakage levels are much higher than under normal application conditions. In addition, reducing product V<sub>cc</sub> and temperature margins limit the range these conditions can be used to accelerate the latent defect populations. IDDQ, which has been widely used in product segments from ASICs to SOCs to commodity memories, has been greatly challenged by the very same trend in proportional increases in background leakage, with greatly reduces the signal to noise ratio of "normal" static current levels versus DUTs that contain latent defects. In fact, this has been a challenge at least since the 250 nm DRAM half pitch, where many companies, began using more advanced techniques, for example, IDDQ "delta" and other Boolean static  $I_{cc}/I_{dd}$  combinations and comparisons about results of multiple tests to maintain efficacy against latest defects and reduce invalid yield "overkill" cost effects. Commodity memories, which have tended to have somewhat lower intrinsic leakage levels per technology generation, have managed to extend and depend on the various IDDQ techniques a little farther than have other product families, but even they are now reporting a real drop off in effectiveness is expected in the next one to two technology generations for IDDQ. Similarly, voltage stress, or applying  $V_{cc}/V_{dd}$  and patterns well above nominal range to accelerate latent defects, also has been losing effectiveness, notably as the differential between  $V_{stress}$  and  $V_{nominal}$  has continued to get smaller at each generation. In the long run, new techniques for providing this reliability screening function will likely be needed, at least in some business segments and product types, sometime in the next few generations. Some of the newer concepts under exploration are improved Boolean and distribution algorithms among various test results both intra-die test (results from the same die) as well as inter-die (wafer neighborhood analysis, analyses within lots, adaptive test limits, analyses across lots, etc.). Another vector that will likely play a larger role moving forward is correction, whether by self-test and self-correction, which is being implemented on some embedded RAMs today, or by error coding detection and correction (ECC) techniques. The challenge here will not be on memories, but rather how and when similar capabilities or alternate approaches to self-correction might be practically applicable and affordable for logic.

#### (3) INCREASING SYSTEMIC DEFECTS

The industry faces new manufacturing-imperfection-related test and yield-learning challenges that result from changing processing technology, changing circuit sensitivities and modeling limitations.

- 1. Process technology advancements are changing the population of physical defects that affect circuit functionality. For example, smaller or higher aspect-ratio vias are more susceptible to incomplete etch, which may lead to a greater prevalence of resistive vias. Similarly, the change from subtractive aluminum processes to damascene Cu may cause a decrease in particle-related blocked-etch metal shorts in favor of an increase in particle-related blocked-deposition metal opens. In addition, the introduction with Cu interconnects of a liner metal that can remain intact when a line open occurs may increase the occurrence of resistive line opens. The introduction of low-κ dielectrics may lead to an increase in the occurrence of possibly latent, resistive bridges and smaller transistors may increase the importance of degradation mechanisms, such as negative bias temperature instability (NBTI).

- 2. Increasing design-process interactions may increase the prevalence of systematic defects. Such defects may occur only in certain circuit/layout configurations, for example because of such issues as pattern density, pattern proximity

and imperfections in optical proximity correction (OPC) algorithms. Although they are systematic they may appear random because of their rarity and the complexity of the conditions required for their occurrence.

- 3. Changing circuit sensitivities are likely to make defects that were benign in the past become killer defects in the future. For example, shorter clock cycles mean defects that cause 10s or 100s of picoseconds of delay are more likely to cause circuit failures. Furthermore power-optimized and/or synthesized designs will result in fewer paths with significant timing margin, which implies that random delay-causing defects will be more likely to cause failure. Similarly increasing noise effects, such as crosstalk and power/ground (GND) bounce, decrease noise and timing margins and again increase circuit susceptibility to defects.

- 4. Finally, modeling complexity threatens the ability of electronic design automation (EDA)/design to ensure the circuit's functionality under all process conditions. That decreased ability combined with increasing process variability may increasingly result in circuits with parametric failure modes reaching the test floor.

All aspects of the test process, including fault modeling, test generation, test coverage evaluation, DFT solutions, test application and diagnosis, must handle these realistic and changing populations of manufacturing imperfections. New classes of defects may not be detectable using traditional test methods for some products; for example, small delay defects for ASICs. Promising strategies include realistic defect-based fault modeling, out-of-spec testing such as low-V<sub>dd</sub> or temperature, defect-oriented test generation and diagnostics, such as those based on layout-based identification of defect sensitivities, statistical methods, adaptive test, and techniques to allow continued use of IDDQ and very-low-voltage testing. To ensure these and other techniques are accurately targeted and effective, high-fidelity information about the occurrence and properties of the population of manufacturing imperfections will be needed, therefore methods for understanding and characterizing the defects must be developed. Test-structure-based methods alone may not be sufficient. Methods based on product-level test results must continue to be developed as well.

## (4) POTENTIAL YIELD LOSSES

Manufacturing yield loss occurs whenever any test or inspection process rejects as faulty a device that would function correctly in the target system. Causes of yield loss include:

- Tester inaccuracies (timing, voltage, current, temperature control, etc.)

- Overtesting (e.g., delay faults on non-functional paths)

- Mechanical damage during the testing process

- Defects occurring in test-only circuitry, e.g., BIST

- Some IDDQ-only failures

- Faulty repairs of normally repairable circuits

- Overly aggressive statistical post-processing

Tester-inaccuracy related yield losses are being mitigated to some extent by the use of alternative test methods to at-speed functional test. DFT methodologies must mature to provide better coverage of the "collateral" defects currently best identified by at-speed functional test vectors through advanced pattern application methods and novel fault models. Care must be taken to avoid adding to the overtesting burden in this development path. Further work on appropriate fault models is also required.

Tester inaccuracies in parametric measurements (timing, voltage, current, and temperature control) and DUT parametric drift during test require guardbands that can be large enough to affect yield. Increasing DUT parametric variation with advanced lithography is pushing the need for more effective BIST or other alternative test strategies such as on-product parametric measurement circuits.

Similar yield loss issues have recently surfaced with inaccurate launch-capture delay tests. Delay path measurement errors of fifteen picoseconds have been observed in delay path measurements—this is 10% of recently announced internal clock periods, indicating a possibility of either yield loss or test escapes, as there is as yet no known way of adding margin testing to delay path measurement. Delay path measurements also contribute to yield loss if inappropriate delay paths are measured. Tools must be developed to avoid yield loss due to measurement of false paths.

IDDQ failures are known to indicate a variety of interconnection and other defects. If, however, IDDQ-only failures are not severe, experience has shown that only a few percent change with burn-in or otherwise prove to be reliability issues. This can be reckoned as yield loss in non-critical applications.

Statistical post-processing is becoming a significant tool for identifying potential failures. However, since it consists of discarding "good die in bad neighborhoods," for example, it is inherently a potential yield loss mechanism.

In a larger sense, however, the concept of yield loss may be understood to include discarding large numbers of properly fabricated devices or interconnect because a small number of improperly fabricated devices are faulty. Yield loss of this sort is currently mitigated in high-density memories by providing redundant rows and columns; similar strategies have been used successfully at system levels using higher levels of reconfigurability and redundancy. Continued development of reconfigurable circuits for defect avoidance or repair focusing on repair techniques that do not cause collateral damage is needed.

Research and development regarding ways to incorporate on-line testing and repairs has a rich history in systems technology. Migrating the results of these efforts into ICs has the potential of reducing yield loss reckoned in this larger sense. More efforts in pursuit of robust design, online testing, and *in situ* repair technology are required.

## **FUTURE OPPORTUNITIES**

## TEST PROGRAM AUTOMATION (NOT ATPG)

While the EDA industry has been providing a range of capabilities around scan DFT and more recently including scan compression and even some DFT synthesis capabilities, for example, for embedded memories, there is an area where the semiconductor suppliers software NRE costs present a productivity and automation opportunity: generation of actual test programs. Across the industry today, the product or test engineering communities spend much of their time creating new customer software code bases, that is, unique and custom individual production test programs. There are a lot of innovative software products for different pieces of this, provided primarily by ATE suppliers along with the ATEs, as well as a lot of additional software tooling down in house by the semiconductor companies themselves. There are even historical or new test program data structure standards (test data format (tdf) or standard test interface language (STIL)) that provide some common structural opportunities. However, the basic fact remains is there are no widely available turnkey software products that produce and validate whole main code test programs and yet most of the 1000s of these in use across the industry today do basically the same kinds of things on similar tools across companies.

#### SIMULATION AND MODELING

Extending the design phase simulation systems and modeling to cover not only die packaging, but also test interface hardware and perhaps even the ATE instrumentation circuits themselves (both parametric and logical) will enable shorter product and manufacturing test validation cycles. This extention will also enable higher reliability pre-silicon verification of the DUT DFT scheme integrated to the manufacturing test instrumentation. Providing such a seamlessly integrated simulation and modeling environment in the pre-silicon design phase would better enable not only accuracy of product performance, but also help tune the test process, and reduce design turns due to minor discrepancies in DFT and test interface modes and hardware.

#### **CONVERGENCE OF TEST AND SYSTEM RELIABILITY SOLUTIONS**

Some of the most widely proliferated DFT techniques (such as scan) were actually originally motivated by the need to provide better system reliability for high-end enterprise computing systems. The same scan hardware was re-usable for manufacturing test screening purposes and has proliferated throughout the industry. In the future, there are a number of physical and circuit phenomena that are challenging lower level intra-die reliability such as alpha particle and cosmic ray induced soft errors, erratic circuit behaviors, and other increasingly intermittent non-predictable lower level behaviors. In response, there is likely to be further extensions of device functionalities to provide additional detection and correction. Like scan, the development and deployment of lower level intrinsic mitigation schemes designed to provide improved system reliability, such as error correction used on RAMs today, and other capabilities of the future, are likely re-usable for test purposes as well (detecting, correcting defects, even systemic ones, on top of the more infrequent or non-predictable intermittent behaviors they would be originally designed to provide protection against). At the very least there will be integration issues with the test process (for example, for redundancy/repair for memories) but more optimistically they could likely be aligned to provide more effective, more efficient, or reduced overhead to future semiconductor test processes.

## **TEST FOR YIELD LEARNING FOCUS TOPIC**

In addition to the normal sorting function, test provides an essential feedback loop for understanding the failure mechanisms inherent in deep submicron fabrication processes. Test is the main source of feedback regarding killer defects, unacceptable parametric variations, and design-process interactions. Complex failures due to design-process interactions, combined with decreasing design margins that push processing technology to its limit, make feedback from test increasingly important to reaching yield-learning goals. Test must increase its ability to support cost-effective defect isolation, process measurements, and failure root cause determination.

## PHYSICAL FAILURE ANALYSIS (PFA)

CMOS technology migration will severely challenge the traditional failure analysis process. The traditional process, comprising the steps of fault localization, deprocessing, and physical characterization/inspection, will increasingly be too slow and difficult for routine analysis. Instead, with development in key areas such as software-based defect localization and signature analysis as described below, destructive failure analysis will move closer to a sampling/verification role. To play this continually important role while keeping pace with technology, improvements and breakthroughs to existing tools/techniques are required—especially better use of tester-based diagnostic and signature analysis tools to direct them. PFA capability gaps are detailed in the following prioritized list.

- 1. Circuit probing—Micro-positioner probing, in-chamber, and atomic-force-microscope-based will be required at each roadmap generation to probe minimum sized transistors (4 probe points) and SRAM cells (5 or more points). This requirement is driven by the need to validate increasingly subtle and/or invisible defects and to characterize individual transistor parameters.

- 2. Localization—There are increasing limitations posed by shrinking dimensions and increasing depth of the metal stack. Failure analysis faces the dilemma that critical defects can be so small that they can only be seen by transmission electron microscopy (TEM) but TEM requires a very thin sample section containing the critical defect that cannot be obtained because the defect cannot be seen or localized with enough precision. As killing defect sizes shrink and the use of inspection tools such as TEM that require significantly better location of the defect increases, it become more critical to be able to identify a failing area to a much smaller volume for analysis.

- 3. Computer-aided design (CAD)/EDA tools—Failure analysis is increasingly reliant on scan methodology to either leads directly to a fault location or to complement another diagnostic tool to improve precision. Significant improvements are required to facilitate the use of both CAD and EDA tools in the failure analysis environment.

- 4. Optical Diagnostic tools, particularly for timing information—The shift in photon energies to longer wavelengths with lower supply voltages will require improvement and/or development in picosecond imaging circuit analysis (PICA)/time resolved photoemission (TRE) detector technology and to solid immersion lens (SIL) optics. Invasive laser-based probes like laser voltage probing (LVP), especially in SOI devices, are also a concern, and the inherent spatial resolution of just under 1 µm is inadequate for distinguishing signals coming from individual transistors. Unless improvements are made in these areas, a radically different technology will be required.

- 5. *Handling new materials*—New materials pose a number of issues for failure analysis. These include sample preparation issues, focused ion beam (FIB) edits and cross sections, electron beam imaging and interactions with the various failure analysis tools. Each new material requires development across a broad spectrum of failure analysis capabilities, including the determination of invasiveness by each physical analysis tool, especially in regards to the fragility of the new process materials.

- 6. *FIB editing*—The ability to perform FIB edits of circuits to support prototypes and reduce the number of design revisions is limited by both required beam placement accuracy and aspect ratio of holes. In addition the ability to perform edits on the new materials in upcoming technologies is unproven.

The development of new capabilities for failure analysis has become increasingly expensive and high-risk, especially as throughput decreases and failure analysis value-proposition goes down. As a result, tool installation is increasingly centralized, reducing total market potential and attractiveness especially for smaller suppliers and start-ups. There is a need for increased and more-cohesive consortium inputs to tool manufacturers to help reduce market-related risk.

#### SOFTWARE-BASED DIAGNOSIS AND SIGNATURE ANALYSIS

As challenges to PFA become more severe, alternatives are needed. A key alternative/supplement to traditional hardwarebased fault localization is software-based fault localization. Software-based fault localization methodologies and tools are needed to handle diagnostics for fails detected by all major test methodologies, including scan-based and BIST-based test;

functional; IDDQ and, especially important, AC (delay) test. Localizing faults in embedded or stand-alone memories, a relatively easy task, is no longer sufficient given the lack of dense upper level metal. The tools must handle all realistic physical defects, including resistive bridges, resistive contacts/vias, and opens. Moreover, scan-based diagnostics must comprehend the fact that a relatively large fraction of yield is lost in scan integrity tests. Defects can also affect clock and other infrastructure nets, and these are difficult to diagnose with today's methods. Methods to diagnose problems related to parametric (non-defect) and reliability failures must also be developed. These methods may be based on both test structures and product-level tests. DFT techniques such as BIST must be designed with special consideration to support the necessary data gathering. IDDQ measurement devices need to support the accuracy levels required by diagnostics. Tester response data capture capabilities and data management systems must meet the demands of these methodologies. Specifically, ATE should allow for unlimited collecting of scan data. Diagnostic data collection allowing localization to a single or few failing net candidates should not add significantly to overall test time.

The tools and methodologies should support several levels of software-based diagnosis:

- 1. Production-worthy data collection, trading off resolution against test cost overhead. Concerns may include test data compression and BIST approaches. An absolute minimum requirement is failing core identification. Average test time overhead should be less than 1%.

- 2. Extensive data gathering on selected engineering or monitor wafers or lots. Granularity must be sufficient to build accurate fault type Paretos and support tool commonality analysis. Throughput time must be short enough to provide timely feedback to the fabrication process on sufficient volume and must support both time-zero and reliability failures. Tools should identify not just failing nets, but failing layers. Such analysis may involve integrating layout information and/or in-line test results into fault localization. Typical test time should be on the order of seconds. During early production, a more significant part of the material may be exposed to such extensive logging.

- 3. Individual die analysis that identifies defects to a single transistor or section of conductor no longer than 10 μm and identifies the failing layer. Such analysis may involve special-purpose diagnostic-resolution-enhancing ATPG and fail data collection and/or analog re-simulation and may be followed-up by failure analysis. Analysis time may be considerably longer than in the previous two cases.

Factory integration issues must be addressed to support these diagnostic needs. Data capture and management capabilities must support increasing reliance on statistical analysis and data mining of volume production data for yield learning. Mechanisms for yield data flow for distributed design and manufacture, including fabless/foundry and third party IP, must also be developed. For example, data management strategies are required to collect consistent data across multiple products containing the same design cores.

Hardware-based fault localization tools may be used to complement and supplement those above as appropriate. The spatial resolution of these techniques is predominantly fixed at about 0.5  $\mu$ m by the near infrared light used for imaging and overlay (e.g., timing-resolved emission, emission microscopy, laser probing and thermally-induced voltage alteration (TIVA), etc.). Unless some other method is developed for backside imaging, this constraint must be dealt with by integrating hardware based fault isolation tools with improved computer aided design capability for overlay and signal tracing. CAD navigation must be both spatial and time-based, that is, linked to simulation waveforms.

Finally, signature analysis techniques must be developed to significantly reduce or eliminate the need for physical failure analysis. Statistical methods are needed to select failing die of a particular class to accurately pre-sort and prioritize input to physical failure analysis. In the longer term, methods must be developed to identify root cause based on test information without resorting to physical failure analysis. A key enabling technology is characterization test methods that are capable of distinguishing individual defect types. DFT support, such as used by the demonstrated MUX-based technique to make SRAM bit lines accessible for parametric analysis, may be required. Integration of electrical characterization with layout data and test-structure/in-line test results are also key capabilities.

## **MANUFACTURING TEST COST FOCUS TOPIC**

Significant progress continues in the reduction of manufacturing test cost, however much work remains ahead. Semiconductor test technology continues the trend towards higher channel integration and higher degrees of multi-site testing, enabled by advanced probe card technologies, new handling technologies, and design for testability techniques. Evidence of this trend is clear in the low performance logic test equipment that is available today. However, significant work remains to translate similar improvements to the broad market of analog and RF. The continuing focus on cost of test will result in a better understanding of cost trade-offs between test methodologies, ATE architectures, and distributed test across multiple insertions among other considerations, resulting in overall test cost reduction.

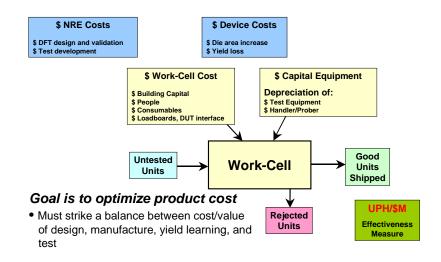

Figure 28 Test Cost Drivers

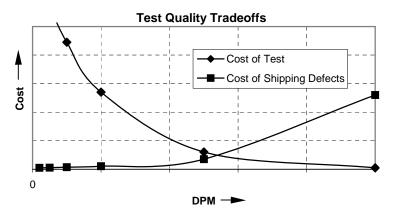

The cost of semiconductor test to the organization has many drivers. See Figure 28. The importance of these drivers varies substantially from device to device. Test development costs are more important for products with a lower volume. The cost of DFT area depends on whether the product is pad limited or core limited. The acceptable cost of test is very market specific and must be determined by balancing the value of test with its cost. Figure 29 presents the test quality trade-offs for an arbitrary chip.

Figure 29 Test Quality Trade-offs: An Arbitrary Example to Illustrate the Trade-offs

Typically, the cost of test increases exponentially with an improvement in DPM. Many semiconductor manufacturers observe an increase in extreme "0 DPM" quality requirements. Despite the indicated trends, many manufacturers are able to achieve the low DPM target while controlling cost. In such cases, a significant part of the cost of test will likely be spent on the tail of the distribution. As technology progresses we expect that defect tolerance techniques will become more pervasive. For certain segments it may become economical to lower the cost of test by accepting increased DPM in tolerant circuits. However, test is not just screening, but a significant value of test is realized in reducing time-to-volume by improving yield learning curves. Test cost should not be minimized independently, but in the context of achieving the lowest overall manufacturing cost over a period of time.

ATE capital cost has traditionally been measured using a simple cost-per-digital pin approach. Although this is a convenient metric, it is misleading because it ignores base system costs associated with equipment infrastructure and central instruments as well as the scaling that occurs with reducing pin-counts and number of sites. Moreover, it is not aligned with the current trend in ATE platforms, where the same base infrastructure can be used for very diverse sets of test channels. The following equation expresses test cell capital cost in terms of the relevant cost drivers of future test technology:

$$C_{CELL} = C_{BASE} + C_{INTERFACE} + C_{POWER-SUPPLIES} + C_{TEST-CHANNELS} + C_{OTHER}$$

In this equation,  $C_{BASE}$  equals the base cost of a test system with zero pins/channels (e.g., it includes the cost of the mechanical infrastructure, back-plane, tester operating system software, and central instruments).  $C_{INTERFACE}$  includes all costs required for interfacing with the device, e.g., the cost of interface electronics, sockets, and probe-cards (including spare probe-cards).  $C_{POWER}$  equals the cost of the power supplies.  $C_{TEST-CHANNELS}$  equals the cost of the instruments (such as digital, analog, RF, memory test instruments).  $C_{OTHER}$  includes the remaining costs (e.g., floor-space). Practical considerations may limit the overall performance breadth that can be cost-effectively achieved by a given  $C_{BASE}$  infrastructure and should be taken into consideration in the overall test cell planning. For example, a low-end system may have an air-cooled infrastructure, whereas the high-end system will use liquid cooling. Test scenarios are evaluated by dividing the capital cost and performance metrics. For example, an important figure of merit is the *Units per Hour per Cost (UPH/\$M)*, that is, the number of shipped devices per hour (*throughput*) over the total cost.

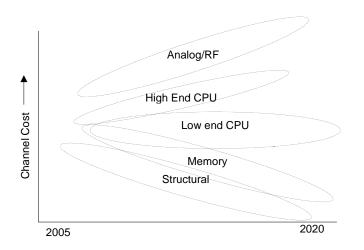

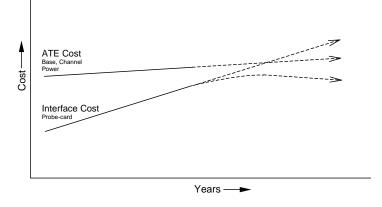

Figures 30 and 31 show trends in channel and interface costs for 2005 to 2020 for devices in each product segment.

Figure 30 Channel Cost Range Trends for Product Segments

Figure 31, particularly, indicates the rapidly rising interface cost—which must be contained over time to avoid dominating the overall test cell cost. The next sections will describe these cost trends in more detail.

Figure 31 Test Cell Cost / Unit vs. Interface Cost Trend

## BASE COST TREND

The total base is expected to decrease slightly over time. Platform strategies will extend the lifetime of the base infrastructure. Moreover, cost may move from the base infrastructure to the instruments. Multi-site test increases throughput and distributes the base cost across multiple dies, thereby reducing the base cost per site (and making the base cost less of a concern). For successful cost scaling using multi-site test it is important that the ATE infrastructure allows dedicated resources because shared resources may limit throughput. The trend of massive parallel test in memory will continue. Moreover, new probe card technologies and handler technologies, will enable massive parallel test in other segments (for both wafer and package test).

## CHANNEL COST TREND

Continuing reduction in channel cost is essential for successful cost scaling using multi-site test: A dominating channel cost per site reduces the advantage of distributing the base-cost among many sites, whereas sharing expensive channels across multiple sites limits throughput. The channel cost is expected to decrease through continued integration within the tester electronics, and also by increased DFT adoption that reduces the ATE pin's performance requirements. Additionally, reduced pin-count test strategies utilizing small test ports can reduce the channel cost per site.

The relatively high cost of analog and RF test instruments, and the long test times associated with testing of these circuits, remain key challenges. DFT methodologies for analog and mixed-signal test are required.

The cost of testing high-speed I/Os is becoming significant. In telecom applications, SONET is going from 2.5 Gbps to 10 Gbps/40 Gbps. In computing applications, serial ATA is going from 1.5 Gbps to 6 Gbps in 2008, and PCIExpress is going from 2.5 Gbps to 5 Gbps around 2006. Moreover, techniques likes simultaneous bi-directional signaling may become significant, adding to the test cost. Looking forward, high-speed I/O DFT techniques and new test methodologies will become a more important part of the solution to control the cost of test.

## Power Cost Trend

With increasing degrees of multi-site, the cost of power supplies will increase. Especially if reduced pin-count techniques are deployed, the power cost per site may dominate the channel cost per site. The cost increase in power supplies may be contained by innovations in power supply and power delivery technology. Note that some DFT techniques increase demand on power supplies to achieve shorter test times.

## INTERFACE COST TREND

Controlling the interface cost is essential for successful cost scaling using multi-site test: A dominating interface cost that increases exponential with the number of sites may defeat the purpose of increasing the number of sites. The interface cost becomes very challenging with high bandwidth (2 Gbit/s) and/or high multi-sites (128 sites). There is a need to develop consistent cost models that cover the wide range of probe card technologies in the market place. Long probe card lead times cause significant cost problems, especially for the advanced technologies. Probe card lead times will be

reduced by a factor of 2 within this roadmap's horizon. For certain products, it may become economical to skip wafer test or only do a simple low performance test. Looking forward, high-speed I/O DFT techniques will become a more pervasive part of the solution to control interface cost.

#### MULTI-SITE TREND

As discussed in the previous sections, the most important way to reduce cost of test is increasing the number of sites. The effectiveness of increasing the number of sites is limited by (1) a high interface cost, see Figure 31, (2) a high channel and/or power cost, and (3) a low multi-site efficiency M:

$$M = 1 - \frac{(T_N - T_1)}{(N - 1)T_1}$$

where *N* is the number of devices tested in parallel (N>1),  $T_I$  is the test-time for testing one device, and  $T_N$  is the test time for testing *N* devices in parallel. For example, a device with a test time  $T_I$  of 10 seconds tested using *N*=32 sites in  $T_N$ =16 seconds has a multi-site efficiency of 98.06%. Hence, for each additional device tested in parallel there is an overhead of (1-M)=1.94%.

Shared ATE resources that reduce the channel cost, may cause a low multi-site efficiency (for example, this is apparent in mixed-signal / RF test). Moreover, as one continues to increase the number of sites, a low multi-site efficiency has a larger impact on the cost of test. For example, a 98% efficiency is adequate for testing two and four sites. However, much higher efficiency is needed for testing 32 sites. At 98% efficiency going from testing a single site to testing four sites will increase a 10s test time to 10.8s. However, going from testing a single site to testing 32 sites at 10s test time to 16.4s, that is, significantly reducing the potential advantage of multi-site test.

Tables 23a and 23b present the expected trend in the number of sites for an arbitrary device in each segment as well as the minimum multi-site efficiency targets. A custom economic model should be deployed to identify the optimized roadmap to scale test cost of a custom device. Note that there are multiple trajectories/approaches that achieve the test cost targets.

| Year of Product  | tion                      | 2005  | 2006  | 2007         | 2008             | 2009                    | 2010                    | 2011                    | 2012                    | 2013                    |

|------------------|---------------------------|-------|-------|--------------|------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| DRAM 1/2 Pitch   | ( <i>nm</i> )             | 80    | 70    | 65           | 57               | 50                      | 45                      | 40                      | 36                      | 32                      |

| MPU/ASIC 1/2 P   | Pitch (nm)                | 90    | 78    | 68           | 59               | 52                      | 45                      | 40                      | 36                      | 32                      |

| High Performa    | nce ASIC/MPU              |       |       |              |                  |                         |                         |                         |                         |                         |

| Wafer test       | Number of sites           | 8     | 8     | 8            | 16               | 16                      | 16                      | 16                      | 32                      | 32                      |

| waler test       | Multi-site efficiency [%] | 95%   | 95%   | 95%          | <mark>98%</mark> | 98%                     | <mark>98%</mark>        | 98%                     | <mark>98%</mark>        | <mark>98%</mark>        |

| Package test     | Number of sites           | 4     | 4     | 4            | 8                | 8                       | 8                       | 8                       | 16                      | 16                      |

| Package test     | Multi-site efficiency [%] | 92%   | 92%   | 92%          | 95%              | 95%                     | 95%                     | 95%                     | <mark>95%</mark>        | 95%                     |

| Low Performan    | ce Microcontroller        |       |       |              |                  |                         |                         |                         |                         |                         |

| Wafer test       | Number of sites           | 64    | 96    | 128          | 256              | 512 /<br>Full<br>wafer  | 512 /<br>Full<br>wafer  | 512 /<br>Full<br>wafer  | 512 / Full<br>wafer     | 512 / Full<br>wafer     |

|                  | Multi-site efficiency [%] | 99.7% | 99.8% | <b>99.9%</b> | 99.9%            | 100%                    | 100%                    | 100%                    | 100%                    | 100%                    |

| Dealrage test    | Number of sites           | 128   | 256   | 256          | 512              | 512                     | 512                     | 512                     | 512                     | 512                     |

| Package test     | Multi-site efficiency [%] | 99.9% | 99.9% | 99.9%        | 100%             | 100%                    | 100%                    | 100%                    | 100%                    | 100%                    |