# INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS 2.0

# 2015 Edition

# SYSTEM INTEGRATION

THE ITRS IS DEVISED AND INTENDED FOR TECHNOLOGY ASSESSMENT ONLY AND IS WITHOUT REGARD TO ANY COMMERCIAL CONSIDERATIONS PERTAINING TO INDIVIDUAL PRODUCTS OR EQUIPMENT.

# **ITRS 2.0 SYSTEM INTEGRATION CHAPTER**

# 1. MISSION

The mission of the System Integration (SI) chapter in ITRS2.0 is to establish a top-down, system-driven roadmapping framework for key market drivers of the semiconductor industry in the 2015-2030 period. The SI focus team is currently developing and constructing roadmaps of relevant system metrics for mobile, datacenter and Internet of Things (IoT) drivers. The mobile driver, embodied by the smartphone product, has redefined the existing ITRS SOC-CP (consumer portable system-on-chip) driver with richer feature requirements. As a fast-growing aspect of the datacenter, microservers have been separated out from the conventional server market segment [16]. IoT, as one of the fastest-growing market segments of electronic devices [15], imposes significantly different design considerations from conventional electronics designs due to low-power and ubiquitous deployment requirements. For these new drivers, the SI focus team seeks to describe new indicators (e.g., power management, bandwidth and integration) as functionalities expand, architectures evolve, and heterogeneous integration soars.

# 2. SCOPE AND TERMINOLOGY

**Changes in the semiconductor industry supply chain.** The 1980s and 1990s saw a semiconductor industry dominated by integrated device manufacturers (IDMs). During this period, the architecture of the main driver in the ITRS, the microprocessor unit (MPU), was not application-driven. Standard components in PC and server systems, e.g., memories and microprocessors, scaled their densities and operating frequencies continuously to meet aggressive performance and cost requirements. Applications had to be designed based on these components. However, in the past ten years, fabless design houses have changed the industry landscape. Design teams have been building customized system-on-chip (SOC) and system-in-package (SIP) products, rather than building standard components, to address specific application requirements. As applications evolve, they drive further requirements for heterogeneous integration, outside system connectivity, etc. A key goal of the SI focus team is to extract the technology requirements hidden behind the evolution of end products such as mobility, datacenter/microservers and IoT. In Table SYSINT1, both the near-term and long-term challenges to system integration are summarized.

| Near term (within 5 years)  | Sub-challenges                                                                                                                                                                                                   | Relation between drivers                                                                                                                                               |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design productivity         | System integration, AMS/MEMS co-design and<br>design automation<br>SIP and 3D (TSV-based) planning and<br>implementation flows<br>Heterogeneous integration (optical, mechanical,<br>chemical, biomedical, etc.) | Mobile/IoT: Beneficial for system dimension<br>scaling, performance improvement, and cost.<br>Datacenter: Beneficial for system-wide<br>bandwidth and power efficiency |

| Power management            | Dynamic and static, system- and circuit-level power optimization                                                                                                                                                 | Mobile/ IoT: Beneficial for battery life<br>Datacenter: Beneficial for cooling cost and<br>energy fee                                                                  |

| Manufacturability           | Performance/power variability, device<br>parameter variability, lithography limitations<br>impact on design, mask cost, quality of<br>(process) models                                                           | Mobile/datacenter/IoT: Beneficial for cost<br>reduction and reliability improvement                                                                                    |

| Bandwidth / service latency | High performance memory / NVM interfaces,<br>memory / processor stacking                                                                                                                                         | Mobile: Beneficial for improving display<br>capacity and developing more sophisticated<br>services<br>Datacenter: Beneficial for faster responses                      |

| Cooling                     | Temperature-constrained physical implementation, 3D integration/packaging                                                                                                                                        | Mobile/datacenter: Avoiding heating issues                                                                                                                             |

| Table SYSINT1: | Summary | of system | integration | challenges. |

|----------------|---------|-----------|-------------|-------------|

|                |         |           |             |             |

| Long term (> 5 years)       | Sub-challenges                                  | Relation between drivers                      |

|-----------------------------|-------------------------------------------------|-----------------------------------------------|

| Design productivity         | System-Level Design Automation (SDA)            | Mobile/datacenter/IoT: Beneficial for faster  |

|                             | Executable Specification                        | design turnaround-time and less design effort |

| Power management            | On-die power sensors, silicon photonics, novel  | Mobile/ IoT: Beneficial for battery life      |

|                             | transistors and memory                          | Datacenter: Beneficial for cooling cost and   |

|                             |                                                 | energy fee                                    |

| Manufacturability           | Sequential 3D integration                       | Mobile/datacenter/IoT: Beneficial for cost    |

|                             | 3D transistors (LGAA, VGAA, CNT)                | reduction and reliability improvement         |

|                             | Novel memory technologies                       |                                               |

| Bandwidth / service latency | High radix networks, interfaces with novel      | Mobile: Beneficial for improving display      |

|                             | memory devices                                  | capacity and developing more sophisticated    |

|                             |                                                 | services                                      |

|                             |                                                 | Datacenter: Beneficial for faster responses   |

| Cooling                     | Microfluidic cooling (single-phase / two-phase) | Mobile/datacenter: Avoiding heating issues    |

| AMS—analog/mixed signal     | MEMS—micro-electro-mechanical systems           | TSV—through silicon via                       |

| NVM—non-volatile memory     | LGAA/VGAA-lateral/vertical gate-all-around      | nd CNT—carbon nanotube                        |

Motivations and distinctions between ITRS 2.0 system drivers and ITRS 1.0 "system drivers". Historically, in its 1998-2013 editions, the ITRS has used metrics such as transistor density, number of cores, power, etc., to roadmap technology evolution of integrated circuits (ICs). These metrics are essentially driven by the physical-dimension scaling as predicted by Moore's Law. The current (2013 edition) ITRS System Drivers Chapter roadmaps key IC products that drive process and design technologies. However, new requirements from applications such as mobile devices, datacenters/microservers, etc. require a new, system-level roadmapping approach, as these applications imply roadmaps for system-level metrics (e.g., the number of sensors, memory bandwidth, etc.). The ITRS roadmapping process as previously seen in the System Drivers Chapter has not explicitly incorporated these system-level product requirements. Therefore, a crucial goal of "ITRS 2.0" is to connect emerging system product drivers, along with corresponding metrics, into the ITRS's semiconductor roadmapping methodology.

#### Terminology and definitions of drivers.

A mobile device is a computing device of which the form factor could be carried by users in daily life and has the capacity to connect to other devices, display information, and execute software.

A datacenter is a facility that centralizes an organization's IT operations and equipment, and where it stores, manages, and disseminates its data. Data centers house a network's most critical systems and are vital to the continuity of daily operations. Consequentially, the service latency, power management, scalability, dependability, and security of data centers and their information are top priorities for organizations [41] [65] [58].

An IoT device (a.k.a. smart object (SO) in other literature) is an autonomous, physical digital object augmented with sensing/actuating, processing, storing, and networking capabilities. It is able to sense/actuate, store, and interpret information created within itself and around the neighboring external world where it is situated, acts on its own, cooperates with other IoT devices, and exchanges information with other kinds of electronic devices (e.g., mobile device and datacenter) and human users [40].

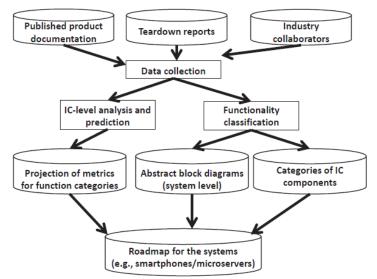

**Driver roadmapping methodology used by system integration.** The roadmap process in ITRS2.0 is summarized in Figure SYSINT1. (i) Calibration data comes from sources such as published data from web searches, specification documents, datasheets and whitepapers from IC companies, teardown reports, and high-level comments from industry collaborators. (ii) Function categories are obtained by clustering the analysis of IC components. Based on the categorization, we create abstract block diagrams as system models. We also analyze the components and predict how metrics such as maximum operating frequency, die area, number of antennas, number of sensors, etc. evolve over the roadmap's 15-year horizon. Finally, we produce a roadmap for system-level metrics based on the projected metrics and the abstract block diagrams.

Figure SYSINT1: Flow of data collection, analysis, and metric projection in the ITRS 2.0 roadmapping methodology.

# **3. MOBILE DRIVER**

In this section, we describe the mobile driver. We describe main features driven by future applications, along with projections of key system metrics. We then describe key technology challenges and potential solutions to which we map the projected system metrics.

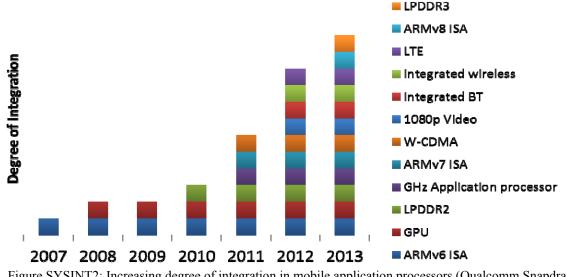

### 3.1 Key metrics to of Mobile Driver

In recent years, mobile devices, notably smartphones, have shown significant expansion of computing capabilities. Since smartphone systems are built with multiple heterogeneous ICs (e.g., logic, memory, microelectromechanical systems (MEMS), and radio-frequency (RF)), we must understand tradeoffs at the system level. Beyond the current ITRS SOC-CP roadmap, ITRS 2.0 introduces a new mobile driver to comprehend and roadmap metrics at a higher, system level for mobility applications. Figure SYSINT2, based on the Qualcomm Snapdragon family of SOCs [1], illustrates the growth of features and degree of integration in recent application processors (APs). Each new technology generation (aka "node"), which enables reduced computation power (e.g., new instruction set architecture (ISA), new devices, new low-power techniques) or the introduction of new features (e.g., graphic processing unit (GPU) or 1080p video), brings an increased number of vertically-stacked bars in the plot. Figure SYSINT2 shows that the degree of integration after 2008 keeps increasing to meet the demands of (i) higher computation performance, (ii) faster wireless connections, and (iii) richer multimedia capabilities. The increasing number of heterogeneous components (RF, logic, memory and MEMS) complicates the system design and blocks form factor reductions, while increasing the smartphone design cost and power budget.

Figure SYSINT2: Increasing degree of integration in mobile application processors (Qualcomm Snapdragon<sup>TM</sup> family) [1].

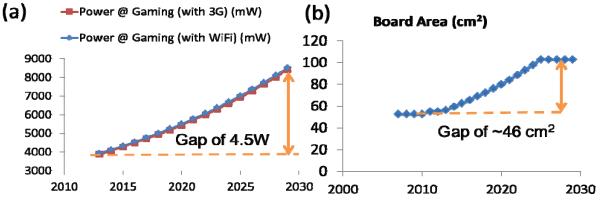

Table SYSINT2 projects key system-level metrics of the mobile driver. Input Metrics in the table correspond to system metrics that are projected into the future. Output Metrics are implied by the trajectories of the Input Metrics. Baseline power growth for each IC component in the mobile driver is the same 7% per year that is specified for IC-level power in the 2013 ITRS roadmap of the SOC-CP product. A system (board-level) power projection (5% growth in power per year) is shown in Figure SYSINT3(a).<sup>1</sup> A 4.5W power management gap, relative to a system maximum power requirement of 4W, is projected to exist at the 15-year horizon. The power management gap for board-level power leads to a number of design challenges (heat and thermal/thermomechanical design, battery life, etc.). We expect that extremely aggressive low-power design techniques will need to be applied to IC components in the mobile driver to address power management challenges. Figure SYSINT3(b) shows a projection for another output metric in Table SYSINT2, namely, board area. An area gap of up to  $46\text{cm}^2$  (relative to a  $60\text{cm}^2$  limit)<sup>2</sup> is seen by the end of the roadmap.

Figure SYSINT3: Implied requirements for mobile driver board area and system power.

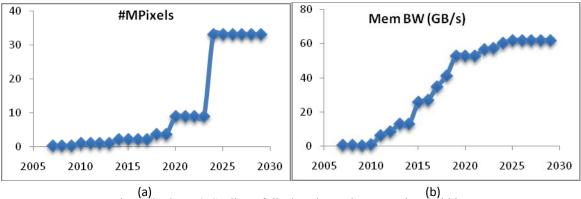

Figure SYSINT4(a) shows the scaling of the number of pixels in the mobile driver displays. Display pixels of this driver are driven by high definition standards (e.g., 720p, 1080p, 4K, etc.). Increase in the display size as well as scaling of GPU cores increase the memory bandwidth requirement as shown in Figure SYSINT4(b). By 2029, ultra HD resolutions of  $7680 \times 4320$  and large number of GPU cores could potentially increase memory BW requirements to 61.9GB/s. The rapid growth of bandwidth demands for system level interconnects and off-device interconnects is considered to be a challenge for the mobile driver design.

<sup>&</sup>lt;sup>1</sup> The annual power growth rate of each component is assumed to be fixed. The SI focus team assumes the power of communication modules (*RF*, modem, WiFi, etc.) does not increase rapidly after new communication standard is introduced since new low power technologies should control the power under budget.

<sup>&</sup>lt;sup>2</sup> Board area limit is calibrated with Apple iPhone 5.

Figure SYSINT4: Scaling of display size and memory bandwidth.

The SI focus team has selected the metrics listed in Table SYSINT2 to develop a technology roadmap for the mobile driver. Through the projection in Table SYSINT2, the SI focus team is able to discover the major technology challenges that must be overcome to address the diverse feature requirement of this mobile driver.

|                   | Tuble 51 511(12: Summar                   |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

|-------------------|-------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|                   | Year                                      | 2007  | 2010  | 2013  | 2014  | 2015  | 2016  | 2017  | 2018  | 2019  | 2020  | 2021  | 2022  | 2023  | 2024  | 2025  | 2026  | 2027  | 2028  | 2029  |

|                   | #AP cores                                 | 1     | 2     | 4     | 4     | 4     | 6     | 9     | 12    | 18    | 18    | 18    | 25    | 28    | 32    | 36    | 33    | 30    | 27    | 25    |

|                   | #GPU cores                                | -     | -     | -     | -     | 6     | 12    | 19    | 30    | 49    | 58    | 69    | 110   | 141   | 189   | 247   | 259   | 273   | 290   | 303   |

|                   | Max freq.<br>(GHz) <sup>3</sup>           | 0.6   | 1.5   | 2.5   | 2.6   | 2.7   | 2.8   | 2.9   | 3     | 3.2   | 3.3   | 3.4   | 3.6   | 3.7   | 3.8   | 4     | 4.2   | 4.3   | 4.5   | 4.7   |

|                   | #MPixels <sup>4</sup>                     | 0.307 | 0.922 | 0.922 | 2.1   | 2.1   | 2.1   | 2.1   | 3.7   | 3.7   | 8.8   | 8.8   | 8.8   | 8.8   | 33.2  | 33.2  | 33.2  | 33.2  | 33.2  | 33.2  |

| Input             | Mem BW<br>(GB/s) <sup>5</sup>             | -     | -     | 12.8  | 12.8  | 25.6  | 26.9  | 34.8  | 41.3  | 52.6  | 52.6  | 52.6  | 56.7  | 57.3  | 60.2  | 61.9  | 61.9  | 61.9  | 61.9  | 61.9  |

| Metrics           | #Sensors                                  | 4     | 8     | 10    | 12    | 14    | 14    | 16    | 16    | 20    | 20    | 20    | 20    | 21    | 21    | 21    | 21    | 22    | 22    | 22    |

|                   | #Antennas                                 | 6     | 8     | 10    | 11    | 11    | 11    | 13    | 13    | 13    | 13    | 14    | 14    | 15    | 15    | 15    | 15    | 15    | 15    | 15    |

|                   | #ICs                                      | 8     | 12    | 9     | 7     | 7-10  | 7-10  | 7-10  | 7-10  | 7-10  | 7-10  | 7-10  | 7-10  | 7-10  | 7-10  | 7-10  | 7-10  | 7-10  | 7-10  | 7-10  |

|                   | Cellular data<br>rate (MB/s) <sup>6</sup> | 0.048 | 1.70  | 12.50 | 12.50 | 12.50 | 12.50 | 12.50 | 21.63 | 21.63 | 40.75 | 40.75 | 40.75 | 40.75 | 40.75 | 40.75 | 40.75 | 40.75 | 40.75 | 40.75 |

|                   | WiFi data<br>rate (Mb/s) <sup>7, 8</sup>  | 6.75  | 75    | 75    | 867   | 867   | 867   | 867   | 867   | 867   | 867   | 7000  | 7000  | 7000  | 28000 | 28000 | 28000 | 28000 | 28000 | 28000 |

|                   | Power (w/ 3G)<br>(W)                      | 3.52  | 3.67  | 3.82  | 4.00  | 4.2   | 4.42  | 4.64  | 4.87  | 5.12  | 5.37  | 5.64  | 5.92  | 6.22  | 6.53  | 6.86  | 7.20  | 7.56  | 7.94  | 8.48  |

| Output<br>Metrics |                                           | 53    | 53    | 57    | 59    | 62    | 66    | 69    | 73    | 76    | 80    | 84    | 89    | 93    | 98    | 103   | 103   | 103   | 103   | 103   |

#### **3.2 Key Challenges and Promising Solutions**

Several challenges exist in the development of the mobile driver, based on the projection of system metrics. In Table SYSINT3, the mapping between these challenges and potential solutions are summarized. In addition, the corresponding quantitative metrics are noted in Column 2 of the same table. Table SYSINT4 shows the timeline for the potential solutions. We note that timeline of potential solutions are not very clear beyond 2020.

<sup>&</sup>lt;sup>3</sup> Max. frequency is defined as the highest operation frequency of components in the system.

<sup>&</sup>lt;sup>4</sup> The #MPixel is defined as the pixel number (in million) of display. It is modeled based on the following speculative timeline on display formats [24] [25]: VGA in 2007, HD720 in 2010, HD1080 in 2014, WQHD in 2018, 4K in 2020, 8K in 2024.

<sup>&</sup>lt;sup>5</sup> The memory bandwidth is defined as the bandwidth between APs and the main memory system. It will be driven by bandwidthhungry applications, such as 3D display with double (120Hz) refresh rate, high-resolution imaging, GPU GFLOPS (follows from the projections from the SOC-CP model) and display, and multimedia features. The steps of memory bandwidth scaling are synchronous with #MPixel scaling due to the correlation.

<sup>&</sup>lt;sup>6</sup> The cellular standard is modeled based on a speculative timeline on communication standards: 3G in 2007 [20], HSPA in 2010 [20], LTE in 2013 [21], LTE with 2x2 MIMO in 2018 [20], and 4x4 MIMO in 2020 [20]. The average growth rate is ~1.3× per year.

<sup>&</sup>lt;sup>7</sup> The WiFi data rate is modeled based on the following speculative timeline on industrial standards: 802.11*a/b/g* in 2007, 802.11*n* in 2010, 802.11*ac* in 2014 [20], 802.11*ad* in 2021 [20], and WirelessHD 1.1 in 2024 [20]. The average growth rate is ~1.4× per year.

<sup>&</sup>lt;sup>8</sup> The increasing bandwidth of cellular WiFi connections is a new challenge to power management since the transmission power is expected to increase. Multiple-input and multiple-output (MIMO) technology is expected to address this power challenge by improving the transmission power efficiency.

<sup>&</sup>lt;sup>9</sup> Board area is defined as the total area of the PCB boards where major components are mounted.

(i) <u>The form factor challenge</u>. As the size of the mobile driver shrinks, especially in thickness, adding new functionalities within a compact form factor becomes very challenging. To address this challenge, the SI focus team has identified two roadblocks in technology development.

- a. The PCB footprint occupied by connectors and components should keep shrinking even though the memory bandwidth requirement and #ICs predicted in Table SYSINT2 increase.

- b. The degree of integration of heterogeneous components, such as logic, memories, non-volatile memories (NVMs), MEMs, RF/analog/mixed-signal (RF/AMS), should keep increasing to reduce the required footprint.

(ii) <u>The system-level power management challenge</u>. Since the predicted board power of the mobile driver will be beyond its 4W target limitation in 2018, system-level power management is an emerging challenge. The roadblocks to address this challenge are as follows.

- a. The increasing memory bandwidth requirement shown in Table SYSINT2 relies on faster signaling and wider system buses, which will increase the board-level power consumption.

- b. Increasing the number of sensors and other IC components require more PCB traces. Shrinking mobile driver form factors are expected to worsen this problem since routing traces will be more complicated, causing interference and higher power.

(iii) <u>The system-wide bandwidth challenge</u>. System-wide bandwidth refers to the bandwidth between application processors and other peripherals. As the requirements of higher compute performance, #functionalities, and display bandwidth keep growing (as indicated by the scaling of #APs, #GPUs, #sensors, #pixels, and the communication bandwidth), delivering proportionate system-wide bandwidth will become challenging. Another aspect of this challenge will be the tradeoffs between power management and bandwidth.

(iv) <u>Communication bandwidth scaling</u>. This challenge refers to the gaps between required cellular data rate or WiFi data rate and achievable data rates. As the required communication standards supported by a single RF module keep increasing, improvement in transistor scaling should provide the technological capability for the mobile driver to integrate more bands and communication standards within a limited PCB footprint budget.

| Challenges                         | Metrics (Description)                                                                         | Roadblocks                                                                                    | Potential solutions                                                                                                     |

|------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Form Factor                        | #Sensors, #ICs, #Antennas,                                                                    | Increasing PCB footprint occupied by                                                          | 1. Package-level integration                                                                                            |

| Challenge                          | (#Components ↑)<br>Memory bandwidth (PCB routing                                              | connectors and components                                                                     | <ol> <li>Through-silicon via (TSV)-<br/>based 3D integration</li> <li>Sequential 3D integration<sup>10</sup></li> </ol> |

|                                    | complexity $\uparrow$ , #connectors $\uparrow$ )                                              | Integration of heterogeneous components                                                       | 1.         TSV-based 3D integration <sup>11</sup> 2.         Unified logic/RF technology                                |

|                                    |                                                                                               | Die area explosion due to more<br>functionalities                                             | <ol> <li>Technology scaling</li> <li>Sequential 3D integration</li> </ol>                                               |

| System-Level<br>Power Management   | Max freq., #AP cores, #GPU cores,<br>Memory bandwidth<br>(Power consumption ↑)                | High-speed off-processor memory buses                                                         | <ol> <li>TSV-based 3D integration</li> <li>Advanced DRAM (HBM,<br/>HMC)<sup>12</sup></li> </ol>                         |

|                                    |                                                                                               | Increasing #sensors and #IC components                                                        | <ol> <li>TSV-based 3D integration</li> <li>Sensor/MEMS/logic<br/>integration</li> </ol>                                 |

| System- wide<br>Bandwidth Scaling  | Memory bandwidth, #MPixel,<br>Cellular data rate, WiFi data rate<br>(Bandwidth requirement ↑) | High-speed off-processor memory buses                                                         | <ol> <li>TSV-based 3D</li> <li>Advanced DRAM (HBM,<br/>HMC)</li> </ol>                                                  |

|                                    |                                                                                               | Increasing inter-component bandwidth requirement                                              | 1. TSV-based and sequential 3D integration                                                                              |

|                                    |                                                                                               |                                                                                               | 2. Integrated multi-standard comm. circuits                                                                             |

| Communication<br>Bandwidth Scaling | Cellular data rate, WiFi data rate<br>(Bandwidth requirement ↑)                               | Increasing communication<br>modes/bandwidth requirement (2015)<br>for cellular phone and WiFi | <ol> <li>Unified logic/RF technology</li> <li>Integrated multi-standard<br/>communication circuits</li> </ol>           |

| Sensor Pixel<br>Scaling            | #MPixel (Pixel density ↑, Optical design complexity ↑)                                        | Pixel dimension scaling limited by optical performance                                        | 1. Sensor/MEMS/logic<br>integration (e.g., back-side<br>illumination [12])                                              |

Table SYSINT3: Key challenges and potential solutions of the mobile driver.

<sup>&</sup>lt;sup>10</sup> Sequential 3D integration refers to 3D integration with fine-pitch TSV (that is close to the gate pitch) while TSV-based integration refers to 3D integration with coarse-pitch TSV's at function block level.

<sup>&</sup>lt;sup>11</sup> 3D integration refers to the superset of sequential 3D, TSV-based 3D, memory/logic stacking, sensor/logic stacking, etc.

<sup>&</sup>lt;sup>12</sup> HBM denotes high bandwidth memory; HMC denotes hybrid memory cube.

|                                                                    | 2016 | 2017 | 2018 | 2019 | 2020 | 2021 | 2022 | 2023 | 2024 | 2025 | 2026 | 2027 | 2028 | 2029 | 2030 |

|--------------------------------------------------------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| Package-level integration                                          |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Stack thickness < 1mm (0.45mm in 2013) [87]                        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| TSV-based 3D integration                                           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Qualification: 3D contact > 100K/mm <sup>2</sup> [88]              |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Sequential 3D integration                                          |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Qualification: 3D contact $> 5M/mm^2$ [88]                         |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Unified logic/RF technology                                        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Qualification: Integration of multiband CMOS RF with APs [90] [91] |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Technology scaling                                                 |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 16/14nm foundry node in 2016                                       |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Advanced DRAM (HBM, HMC)                                           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Qualification: 100GB/sec [92] [93]                                 |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Integrated multi-standard comm. circuits                           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Qualification: Single-chip RF/TX/RX (> 40 bands) [94]              |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Sensor/MEMS/logic integration                                      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

|                                                                    |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

### Table SYSINT4: Timeline for potential solutions for the mobile driver

This legend indicates the time during research, development, and qualification pre-production should be taking place for the solution.

Qualification: the criteria to reach pre-production

Qualification: Multi-MEMS integrated with processing logic [12] [89]

Research Required Development Underway

Qualification/Pre-production

Continuous Improvement

The solution timeline is explained as follows.

**Package-level integration** is a near-term solution for form factor scaling. The thickness of logic/memory package was 0.45mm in 2013 [87] and improvement will continue.

**TSV-based integration** is expected to research 100K/mm<sup>2</sup> 3D contact density by 2020. It will provide higher integration capacity for memory, logic, AMS, etc. [81]

**Sequential 3D** Beyond 2021, sequential 3D integration is expected to continue the Moore's Law scaling by enabling finegrained interconnection (>5M/mm<sup>2</sup>) between stacked dies [84].

**Unified logic/RF circuits** [51]. This is a long-term trend to tightly integrate multi-standard RF circuits and application processors beyond 2023.

**Technology scaling.** 2016 onwards, technology scaling will continue as the main thrust for the semiconductor industry throughout the roadmap, along with the new device development predicted in the More Moore Chapter.

Advanced DRAM will provide more bandwidth than conventional LPDDRx interfaces. We expected to see its deployment in the mobile driver if bandwidth demand increases due to gaming and other visual applications. The bandwidth target is 100GB/sec by 2020 [92] [93].

**Sensor/MEMS/logic integration** will continue to be merged with each other through package-level integration, 3D, or single-chip solutions [89]. Since this involves several technologies to be developed (integration and devices), it is expected around 2020.

**Integrated multi-standard communication circuits**. Due to the increasing cellular bandwidth and multi-standard support, we expect the **integrated multi-standard communication circuits** in 2018 (this does not include application processors, but only modem logics).

## 4. DATACENTER AND MICROSERVER DRIVERS

In this section, we describe the main features, key metrics, key challenges, and potential solutions for the challenges of datacenter and microserver drivers.

### 4.1 Key Metrics of Datacenter and Microserver Drivers

Recent studies of datacenters (e.g., by Doller et al. [2]) suggest that high-performance MPU (MPU-HP) and networking SOC (SOC-NW) products are the main components in datacenters. These products may be implemented either in a single chip or in a multichip module (MCM). Optimized datacenter architecture cannot be achieved with a single chip as its key building block; rather, a co-optimization of storage, interconnects and software is required. Since the raw data stored in datacenters is usually sparse, pre-processing that is typically executed in traditional server cores are precluded, due to energy budget. Besides integrating power-efficient cores to be within an energy budget, datacenters require high

#### 10 ITRS 2.0 System Integration Chapter

bandwidth and accessibility for local memories (mostly non-volatile memories) to execute data-intensive operations. Datacenters are a driver for functionality scaling, lithography and device scaling, high-density integration and packaging, and advanced interconnect solutions. Due to datacenter-specific optimizations and system-level design requirements such as high rack density and cooling capacity, the metrics of servers in datacenters are different from those of server chips in existing products which are comprehended by ITRS.

Some new design challenges to the microserver driver are introduced by their deployments in datacenters. Big data computing requires a drastic reduction in communication latencies to meet an under-100ms requirement, meaning data must be increasingly localized. The collected data suggests that the microserver driver addresses the cost issue by limiting the number of cores per rack unit and the latency issue by localizing user-specific search data. The volume of information in datacenters is anticipated to grow at a very high rate (e.g., double every two years, or even faster). When users search for specific information, latencies can be on the order of tens of milliseconds because datacenters typically store information in a highly distributed manner. As datacenters grow in size, communication latencies increase along with power consumption. To limit power and temperature of datacenters, companies are forced to invest huge amounts of money to establish and maintain power plants adjacent to datacenters, and to construct datacenters in geographies with "natural refrigeration". There is a limit to such investment in power plants and cooling. Cooling costs, which can reach over 35% of electricity costs, continue to rise in server farms and datacenters. This creates a need to reduce the number of cores and operating frequencies to limit this cost.

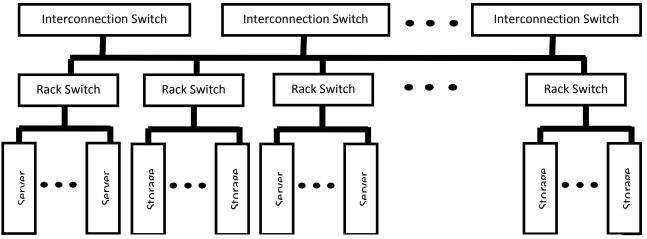

Figure SYSINT5: Datacenter block diagram.

Figure SYSINT5 shows a datacenter block diagram. As discussed above, latency and bandwidth dominate the datacenter metrics roadmap. Electrical networking components will eventually become optical, non-volatile memory will take over storage from mechanical disks, and the storage hierarchy and overall server topology are expected to flatten as the roadmap advances.

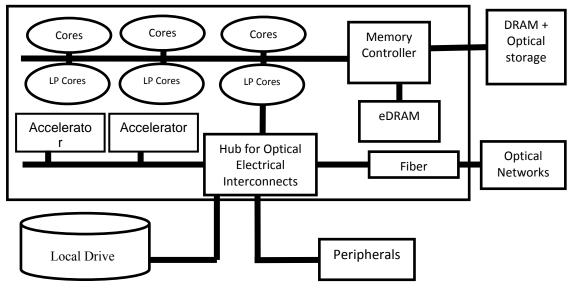

Figure SYSINT6: Microserver block diagram.

Computational power density challenges of microservers may imply SOC/ASIC-like trajectories with more light / lowpower (LP) cores, peripherals, application-specific accelerators, complicated inter-IP communication fabrics, and higher integrated network bandwidth to address system throughput requirements under strict form-factor and power constraints. Figure SYSINT6 shows a block diagram of microservers in 2020 and beyond. The microserver organization integrates optical interconnects and low-power and heterogeneous cores.

To reduce operating costs, datacenters and microservers must maximize the number of cores in a rack unit subject to power and thermal constraints. Form factor, energy-efficiency, and networking throughput are important for these drivers owing to strict latency requirements. The microserver design is further challenged by form factor needs. As a consequence, demand for reduced form factor and system design efforts drive the integration of the MPU and the chipset. Compared to a 1U server (MPU-HP in ITRS), a microserver has a higher degree of integration as it includes on-chip Ethernet and peripheral hubs. Recent MPUs for microservers integrate application-specific accelerators to improve energy efficiency. Hence, high integration of functionalities is also a challenge for both datacenters and microservers. The SI focus team has selected the metrics listed in Tables SYSINT5 and SYSINT6 to develop technology roadmaps of datacenters and microservers, respectively.

| Year                                    | 2010  | 2014  | 2015  | 2017 | 2019   | 2021   | 2023   | 2025   | 2027   | 2029    |

|-----------------------------------------|-------|-------|-------|------|--------|--------|--------|--------|--------|---------|

| # Cores (K)                             | 64    | 300   | 360   | 1044 | 3008   | 4935   | 5825   | 7578   | 8967   | 10602   |

| Storage (PB) <sup>13</sup><br>[68] [26] | 20    | 100   | 300   | 1559 | 4676   | 14029  | 42088  | 126264 | 378792 | 1136377 |

| Area (MSF)<br>[66] <sup>14</sup>        | 0.2   | 0.5   | 0.5   | 0.9  | 1.6    | 2.2    | 2.2    | 2.42   | 2.42   | 2.42    |

| Power [27]<br>(MkWh) <sup>15</sup>      | 777.2 | 770.6 | 779.8 | 839  | 1004.7 | 1137.2 | 1226.1 | 1380.7 | 1635.6 | 2044.3  |

| Switch [28]<br>BW(Tb/s) <sup>16</sup>   | 100   | 631   | 1000  | 2512 | 6309   | 10000  | 15849  | 25119  | 39811  | 63096   |

| GFLOPS/W <sup>17</sup>                  | 0.4   | 1.7   | 2.4   | 4.9  | 10     | 17     | 24     | 33.9   | 47.9   | 67.8    |

| 1U/rack <sup>18</sup>                   | 40    | 40    | 40    | 40   | 40     | 40     | 40     | 40     | 40     | 40      |

| Cores/socket <sup>19</sup>              | 8     | 15    | 18    | 29   | 47     | 59     | 74     | 93     | 117    | 147     |

| Power/1U (W) <sup><math>20</math></sup> | 700   | 700   | 700   | 700  | 700    | 700    | 700    | 700    | 700    | 700     |

Table SYSINT5: Summary of scaling trends of datacenters.

<sup>13</sup> The total data amount hosted in the datacenter.

<sup>14</sup> The area of one server building. A datacenter is composed with multiple server buildings.

<sup>15</sup> Total power consumption of a datacenter.

<sup>16</sup> The total switching capability of a datacenter.

<sup>17</sup> Giga flops per watt, which measures the energy efficiency of a datacenter.

<sup>18</sup> Server unit density of a rack.

<sup>19</sup> #Processor cores installed to a single socket on the server main board.

<sup>20</sup> Power consumed by a single server unit.

| Memory / 1U<br>(GB) <sup>21</sup>          | 8     | 24      | 32     | 45    | 64     | 76     | 91     | 108    | 129    | 154    |

|--------------------------------------------|-------|---------|--------|-------|--------|--------|--------|--------|--------|--------|

| Power/socket [29] <sup>22</sup>            | 180   | 168     | 165    | 159   | 153    | 149    | 145    | 141    | 137    | 133    |

| NW BW/1U<br>(Gb/s) [30] <sup>23</sup>      | 1     | 10      | 40     | 40    | 100    | 100    | 100    | 400    | 400    | 400    |

| NW BW/rack<br>(Gb/s)                       | 40    | 400     | 1600   | 1600  | 4000   | 4000   | 4000   | 16000  | 16000  | 16000  |

| Rack switch BW (Gb/s) [31] <sup>24</sup>   | 10    | 400     | 1200   | 1200  | 3000   | 3000   | 3000   | 12000  | 12000  | 12000  |

| Power<br>efficiency <sup>25</sup>          | 0.5   | 0.54    | 0.55   | 0.57  | 0.59   | 0.61   | 0.63   | 0.65   | 0.67   | 0.69   |

| Communication power (MkWh) <sup>26</sup>   | 2.19  | 13.83   | 21.91  | 55.05 | 138.26 | 87.66  | 138.93 | 220.19 | 348.97 | 553.08 |

| Storage power<br>(MkWh) [32] <sup>27</sup> | 0.001 | 0.00876 | 0.0657 | 0.259 | 0.449  | 0.778  | 1.347  | 2.334  | 4.043  | 7.004  |

| Cooling power<br>(MkWh) <sup>28</sup>      | 18.51 | 34.36   | 38.99  | 55.02 | 86.13  | 237.31 | 264.26 | 307.03 | 374.89 | 482.56 |

| #Users (B) [33] <sup>29</sup>              | 0.44  | 1.32    | 1.74   | 3.01  | 5.21   | 9.03   | 15.63  | 27.07  | 46.89  | 81.21  |

| Data Upload<br>(GB/month/user)             |       |         |        | 12    | 75     | 120    | 224    | 200    | (72)   | 1166   |

| [34] [67] <sup>30</sup>                    | 4     | 6       | 14     | 43    | 75     | 129    | 224    | 389    | 673    | 1166   |

Table SYSINT6: Summary of scaling trends of microservers.<sup>31</sup>

| Year                                     | 2010 | 2013 | 2014 | 2015 | 2016  | 2017  | 2018 | 2019 | 2020  | 2021 | 2022 | 2023  | 2024  | 2025  | 2026  | 2027   | 2028   | 2029   |

|------------------------------------------|------|------|------|------|-------|-------|------|------|-------|------|------|-------|-------|-------|-------|--------|--------|--------|

| #MPU cores/rack<br>unit                  | 8    | 16   | 19   | 23   | 27    | 32    | 38   | 45   | 51    | 57   | 64   | 72    | 81    | 91    | 102   | 114    | 128    | 144    |

| Max freq. (GHz)                          | 2.8  | 3.46 | 3.6  | 3.74 | 3.89  | 4.05  | 4.21 | 4.38 | 4.56  | 4.74 | 4.93 | 5.13  | 5.34  | 5.55  | 5.77  | 6      | 6.24   | 6.49   |

| DRAM cap. (GB)/<br>rack unit             | 32   | 128  | 202  | 319  | 504   | 796   | 1258 | 1988 | 3141  | 4963 | 7842 | 12390 | 19576 | 30930 | 48869 | 77213  | 121997 | 192755 |

| DRAM BW<br>(GB/s) <sup>32</sup>          | 10.6 | 51.2 | 64.8 | 82   | 103.7 | 131.2 | 166  | 210  | 265.6 | 336  | 425  | 537.6 | 680   | 860.1 | 1088  | 1376.2 | 1740.8 | 2202   |

| Off-MPU BW<br>(GB/s) <sup>33</sup>       | 25.6 | 64   | 82   | 105  | 135   | 173   | 222  | 285  | 337   | 399  | 472  | 558   | 660   | 781   | 924   | 1093   | 1293   | 1530   |

| MPU freq. ×<br>#Cores<br>(GHz)/rack unit | 22   | 55   | 68   | 86   | 105   | 130   | 160  | 197  | 233   | 270  | 316  | 369   | 433   | 505   | 589   | 684    | 799    | 935    |

The projections in Tables SYSINT5 and SYSINT6 imply technology challenges to deployment of datacenter and microservers for big data and server-type applications.

### 4.2 Key challenges and promising solutions

A major trend of datacenters is consolidation of distributed smaller datacenters to centralized gigantic datacenters. The first observation is the recent migration of data hosts from local storage to cloud operated by major cloud computing service providers (e.g., Google and Amazon AWS) [52] [53]. Major technology requirements in datacenter applications, such as latency, dependability, and scalability, have been driving the consolidation. Due to these technology requirements, a qualified local datacenter might be too expensive to maintain, which is also accelerating the consolidation and the migration to cloud. As an example, we have observed significant effort toward datacenter consolidation in government

<sup>30</sup> Monthly data amount uploaded by user.

<sup>&</sup>lt;sup>21</sup> Main memory installed to a server unit.

<sup>&</sup>lt;sup>22</sup> Power consumed the cores on a single socket.

<sup>&</sup>lt;sup>23</sup> Network bandwidth connected to a server unit.

<sup>&</sup>lt;sup>24</sup> Switching capacity of within a single rack.

<sup>&</sup>lt;sup>25</sup> Ratio of power consumed within a datacenter to the power delivered from grid to the datacenter.

<sup>&</sup>lt;sup>26</sup> Power consumed by networking and switching.

<sup>&</sup>lt;sup>27</sup> Power consumed by storage.

<sup>&</sup>lt;sup>28</sup> Power consumed by cooling facility.

<sup>&</sup>lt;sup>29</sup> Users served by a datacenter.

<sup>&</sup>lt;sup>31</sup> Metrics are defined for a single server unit.

<sup>&</sup>lt;sup>32</sup> Bandwidth between main memory and MPUs.

<sup>&</sup>lt;sup>33</sup> Bandwidth from MPU to peripheral. E.g., the BW through PCI Express to network or storage.

segments.<sup>34</sup> We believe the trend of consolidation will continue as the Internet services and IoT services demand lower latency, dependable, and scalable datacenters.

However, datacenter consolidation is faced with some showstoppers. The analysis from [57] indicates that building diverse new services is slowing down the consolidation because the service providers may intensively rely on localized and customized datacenters to enable differentiated services from competitors. The technology challenges of hardware are also slowing down the consolidation. To continue the consolidation, the following challenges need to be addressed: service latency, space density, power, and integration. These challenges are also confirmed by several observations regarding the major cloud-service companies: **Rapid growth of server nodes in a datacenter.** We have noticed that the number of servers (in terms of rack) of Amazon AWS has grown 27% per year recently [59]. This is mapped to the space density and the integration challenges. **Better power efficiency.** The power consumption of Google data center has decreased by 10% per year recently [60]. **Service latency gap between cloud and local datacenters.** The performance comparison between local storage and Amazon AWS in [61] shows the latency overhead (1~2ms) of cloud datacenters could be a significant performance degradation when the expected service latency is of several millisecond level.

Table SYSINT7 lists the challenges of the datacenter and microserver drivers, organized into latency, power management and integration challenges. A mapping of the challenges to quantitative metrics (Table SYSINT5 and Table SYSINT6) is given in Column 2 of Table SYSINT7, and Table SYSINT8 shows the timeline of the potential solutions. We note that timeline of potential solutions are not very clear beyond 2020.

(i) <u>The service latency challenge</u> rises in datacenter/microserver design because of the crucial requirement for service latency. The research in [3] proposes much more pessimistic metrics (from 50<sup>th</sup> percentile to 99<sup>th</sup> percentile latency) to ensure service quality could be guaranteed when "Big Data" is hosted. To address this application requirement, solutions are expected from a wide range of providers.

- a. Since network performance will dominate service latency, high-radix photonics switching networks are expected to be introduced to address the internode bandwidth requirement.

- b. To host Big Data, conventional memory architectures will be unable to address access time requirements for Big Data. Spindle-based hard drives will be replaced by storage-class memories (SCM).

- c. To improve the intra-node communication performance (e.g., for MPU to memories in Table SYSINT6 or memories to NVMs), better solutions for heterogeneous integration are expected.

(ii) To provide sufficient computing resources with MPU cores and application-specific accelerators,

- a. Moore's Law should continue the transistor scaling so that more functionalities could be hosted in the same die area while avoiding power increases that result in too much overhead to the cooling equipment.

- b. Better memory integration (e.g., memory-over-logic) in each computing node is expected to ease the power management challenge by reducing the power impact.

- c. Advanced power management techniques such as adaptive power management with on-die power sensors [6] are expected to be developed to address the power management issue.

(iii) <u>The electro-optical integration challenge.</u> Since the power and performance requirements of datacenter are both crucial, highly-integrated photonic inter-node networks are expected by 2020 [3]. Since the electro-optical interfaces are distributed all over the datacenter, it is necessary to develop on-chip light sources and on-chip photonic modulators and detectors to reduce the power, space, and performance overhead due to off-chip converters for electro-optical interfaces.

| Challenges                | Metrics                                     | Roadblocks                | Potential solutions                |

|---------------------------|---------------------------------------------|---------------------------|------------------------------------|

| Service Latency Challenge | #MPU cores/rack unit, DRAM cap./ rack unit, | Low #hop connections      | High-radix network [3]             |

|                           | Max Freq., DRAM bandwidth, Off-MPU          | Low bit/J transmission    | Silicon photonics [3] which can    |

|                           | bandwidth (Performance requirement ↑)       |                           | deliver higher switch BW and lower |

|                           |                                             |                           | pJ/bit                             |

|                           |                                             | High performance memory   | SCM to replace hard drives [3]     |

|                           |                                             | architecture              |                                    |

|                           |                                             | High storage bandwidth    | Distributed storage nodes [3]      |

|                           |                                             | Encrypted data processing | Distributed compression and        |

|                           |                                             |                           | encryption engines [3]             |

|                           |                                             | NVM reliability           | Novel memory devices [3]           |

|                           |                                             |                           | Control algorithm [4]              |

| Node Density/Cooling/     | #MPU cores/rack unit, DRAM cap./ rack unit, | Die areas increase due to | Moore's Law scaling                |

| Power Management          | Max Freq., DRAM bandwidth, Off-MPU          | more functionalities      |                                    |

Table SYSINT7: Key challenges and potential solutions of the datacenter and microserver drivers.

<sup>34</sup> The Department of Health and Human Services (HHS) of the United States proposed a 20% reduction plan for their datacenters from 2010 to 2015 [55].

#### 14 ITRS 2.0 System Integration Chapter

| Challenge                   | bandwidth                           | Low power processor           | 64-bit ARM core [5]                 |

|-----------------------------|-------------------------------------|-------------------------------|-------------------------------------|

|                             | (Power consumption $\uparrow$ )     | architecture                  |                                     |

|                             |                                     | Lack of one-fits-all          | Modularized processor 3D stacks     |

|                             |                                     | processor architecture        | (TSV-based) [5]                     |

|                             |                                     | Power management for          | Integrated on-die power sensors [6] |

|                             |                                     | different application context |                                     |

| Electro-Optical Integration | DRAM bandwidth, Off-MPU bandwidth   | On-chip light source          | Silicon compatible laser source     |

| Challenge                   | (Bandwidth requirement $\uparrow$ ) |                               | [100]                               |

|                             |                                     | On-chip detector /            | Silicon compatible laser source     |

|                             |                                     | modulator                     | [100]                               |

#### Table SYSINT8: Timeline of potential solutions of the datacenter and microserver drivers.

|                                                                                                            | 2016 | 2017 | 2018 | 2019 | 2020 | 2021 | 2022 | 2023 | 2024 | 2025 | 2026 | 2027 | 2028 | 2029 | 2030 |

|------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| Silicon photonics                                                                                          |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Qualification: (1) Monolithic integration of silicon photonics [96] [95]<br>(2) > 200GB/s directly off MPU |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Silicon compatible laser source                                                                            |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Qualification: Light source on silicon substrate [100]                                                     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| High-radix networks                                                                                        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Qualification: Optical switches with > 1K ports [97]                                                       |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Storage class memory (SCM)                                                                                 |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Qualification: sub-us latency [98]                                                                         |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Distributed compression, encryption engines                                                                |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Qualification: built-in 10Gbps-level IPsec/SSL accelerator                                                 |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Novel memory devices                                                                                       |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Qualification: achieving < sub-us latency [98] [99]                                                        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 64-bit ARM processor core                                                                                  |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Ready solution                                                                                             |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Modularized processor 3D stacks (using TSV-based 3D)                                                       |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Qualification: 3D contact > 100K/mm <sup>2</sup> [88]                                                      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| On-die power sensors                                                                                       |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Qualification: 25x power efficiency improvement [101]                                                      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

This legend indicates the time during research, development, and qualification pre-production should be taking place for the solution.

#### Qualification: the criteria to reach pre-production

Research Required

Development Underway

Qualification/Pre-production

Continuous Improvement

The solution timeline is explained as follows.

**Silicon photonics.** Optical device development and integration challenges of silicon photonics will be the main showstoppers for deployment of this technology. By 2020, we expect monolithic integration could provide more than 200GB/s directly between the cores/cache [95] [96]. The requirements of high-bandwidth and low-energy to process huge amounts of data will drive pre-production by 2020 [97] [104].

Silicon compatible laser source. Prior to deployment of silicon photonics, silicon compatible laser source needs to be ready by 2018.

**High-radix network.** Since the service latency is critical to the datacenter design, high-radix networks provide fewer hops among server nodes. We expect more than 1000 ports in a single optical switch by 2020.

**Storage-class memory.** Replacing mechanical hard drives with non-volatile storage is required for bandwidth and energy efficiency requirements (sub- µs latency [98] [99]). The full deployment of SCM is expected in pre-production by 2017.

**Distributed compression, encryption engines.** The datacenter is expected to enhance data security and compress sparse data to save both bandwidth and storage. We have observed the existence of the encryption engines within processor cores. We expect higher throughput in the future.

**Novel memory devices.** New memory technologies provide promising solutions for service latency (sub- µs latency), energy efficiency, and server node density scaling. Flash memory, as the current mainstream NVM storage media, will need to be replaced due to durability, integration, and performance issues. Novel memory devices are promising candidates for the datacenter driver. However, the deployment may be constrained by device research progress. We expect novel memory devices to be in pre-production by 2019.

**64-bit ARM cores.** The ARM architecture is popular in the mobile market for its energy efficiency. This solution is ready for the datacenter.

**Modularized processor 3D stacks [5].** From [65], we expect datacenter design would require diverse types of server nodes (e.g., computation and storage). Modularized 3D stacking (based on TSV-based 3D) provides a solution to reduce the NRE cost due to small processor module amount for each node type. The interposer-based integration in [5] is ready, but we require development and optimization of the system. Deployment is constrained by the components to be integrated (e.g., novel memory devices and silicon photonics) and is expected to be in pre-production by 2020.

**On-die power sensor.** This technology combines thermal sensors and DVFS information for real-time power monitoring. Although monitor circuits are ready, aggressive and pervasive self-management is expected in 2019 to achieve 25x power efficiency improvement [6].

# **5. IOT DRIVER**

The IoT driver represents the extreme low power requirement in the semiconductor industry. The operations of IoT devices are constrained by battery sizes and long operation life time. Instead of roadmapping computation performance, we predict power efficiency instead. The key metrics are operation duty cycles, suspend current, Ion/core frequency, and life time.

## **5.1 Key Metrics of IoT Driver**

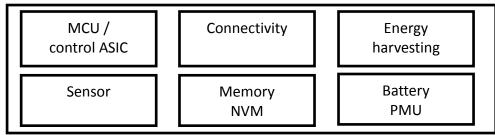

The exemplar block diagram of the IoT driver is shown in Figure SYSINT7. The architecture of the IoT driver is missionoriented. The hardware implementation could be a subset of the listed blocks, or constructed by programmable logic (e.g. FPGA). The integration approach varies from board level (e.g., batteries), package level (sensor/MCU package), 3D stacking (MCU and memory stacking), or chip level integration (baseband and MCU).

Figure SYSINT7: Exemplar block diagram of IoT device.

Based on the baseline configuration shown in Figure SYSINT7, the SI focus team has identified four categories of metrics to be tracked for IoT Driver: power, form factor, performance, and peripheral. The categories and metrics tracked by the SI focus team are listed in Table SYSINT9. Power: The trend of VDD follows latest ORTC voltage scaling. The SI focus team roadmaps the mass deployment of energy harvesting to start at 2019. Due to the constrained energy source, the SI focus team roadmaps the suspend current of the MCU to scale at 0.85x per year. The efficiency and power density of integrated DC-DC converters are roadmapped to scale at  $1.01^{\times}$  and  $1.08^{\times}$  per year, respectively. The connectivity power consumption, constrained by energy source and communication throughput, is also roadmapped to scale down per year. The peak current (mainly constrained by the storage and source of energy) scales at 0.62x per year and the transmission power per bit scales at 0.63x per year. Form factor: the system form factors of IoT devices are mainly constrained by the battery and the passive components. The SI focus team roadmaps the form factor will gradually scale down at 0.8x per year after 2018 due the mass deployment of energy harvesting and higher integration of components. **Performance**: the SI focus team expects MCU performance to scale conservatively relative to MPU or SOC because the strict power efficiency constraint and form factor constraint. The MPU clock scales at 1.085x per year before 2020 and 1.017x per year afterward. The power efficiency metric in terms of I<sub>ON</sub> per MHz, scales at 0.85x per year until 2022 and 0.93x afterward. The number of MCU core is fixed at single cores, and the performance improvement (MCU DMIPS) increases linearly. Peripheral: the SI focus team roadmap expects the number of sensors to increase rapidly in the 2015 to 2017 timeframe. The increase will saturate afterward due to the limitation of integration effort. The power consumed by sensors will scale at 0.7x from 2015 to 2017, 0.85x from 2018 to 2021, and 0.92x afterward, due to the energy constraint. Conversely, the density of battery or other form of energy storage will increase at 1.07x per year to support the increase of connectivity throughput, MCU performance, and integrated sensors.

| 1           | Table SY SIN 19: Summary of scaling trends of 101 driver.                   |       |       |       |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |       |

|-------------|-----------------------------------------------------------------------------|-------|-------|-------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|-------|

| Categories  | Year                                                                        | 2015  | 2016  | 2017  | 2018                | 2019                | 2020                | 2021                | 2022                | 2023                | 2024                | 2025                | 2026                | 2027                | 2028                | 2029  |

|             | Energy source<br>(B = battery; H = energy<br>harvesting)                    | В     | В     | В     | <b>B</b> + <b>H</b> | B + H |

|             | Lowest VDD (V) <sup>35</sup>                                                | 0.8   | 0.8   | 0.75  | 0.75                | 0.7                 | 0.7                 | 0.65                | 0.65                | 0.65                | 0.55                | 0.55                | 0.55                | 0.45                | 0.45                | 0.45  |

| _           | Deep suspend current [35]<br>(nA) <sup>36</sup>                             | 100   | 85    | 72    | 61                  | 52                  | 44                  | 38                  | 32                  | 27                  | 23                  | 20                  | 17                  | 14                  | 12                  | 10    |

| Power       | DC-DC efficiency (%) <sup>37</sup>                                          | 80%   | 81%   | 82%   | 85%                 | 86%                 | 87%                 | 88%                 | 88%                 | 89%                 | 90%                 | 91%                 | 92%                 | 93%                 | 94%                 | 95%   |

|             | DC-DC power density<br>(W/mm <sup>2</sup> ) <sup>38</sup>                   | 10.00 | 10.80 | 11.66 | 12.60               | 13.60               | 14.69               | 15.87               | 17.14               | 18.51               | 19.99               | 21.59               | 23.32               | 25.18               | 27.20               | 29.37 |

|             | Peak Tx/Rx current (mA) <sup>39</sup>                                       | 50.00 | 31.05 | 19.28 | 11.97               | 7.44                | 4.62                | 2.87                | 1.78                | 1.11                | 0.69                | 0.43                | 0.26                | 0.16                | 0.10                | 0.06  |

|             | Tx/Rx power per bit (<br>$\mu$ W/bit) <sup>40</sup>                         | 2.480 | 1.552 | 0.972 | 0.608               | 0.381               | 0.238               | 0.149               | 0.093               | 0.058               | 0.037               | 0.023               | 0.014               | 0.009               | 0.006               | 0.004 |

| Form factor | Module footprint (mm <sup>2</sup> ) <sup>41</sup>                           | 500   | 500   | 500   | 350                 | 280                 | 224                 | 179                 | 143                 | 115                 | 92                  | 73                  | 59                  | 47                  | 38                  | 30    |

|             | MCU #Cores                                                                  | 1     | 1     | 1     | 1                   | 1                   | 1                   | 1                   | 1                   | 1                   | 1                   | 1                   | 1                   | 1                   | 1                   | 1     |

|             | MCU I <sub>ON</sub> / Operation<br>frequency [36]<br>(µA/MHz) <sup>42</sup> | 30.0  | 25.5  | 21.7  | 18.4                | 15.7                | 13.3                | 11.3                | 9.6                 | 8.9                 | 8.3                 | 7.7                 | 7.2                 | 6.7                 | 6.2                 | 5.8   |

| Performance | Max MCU Frequency<br>(MHz) [37]                                             | 200   | 217   | 235   | 255                 | 277                 | 301                 | 306                 | 311                 | 316                 | 322                 | 327                 | 333                 | 338                 | 344                 | 350   |

|             | MCU Flash Size (KB)<br>[38] <sup>43</sup>                                   | 1024  | 1024  | 1024  | 1024                | 2048                | 2048                | 4096                | 4096                | 4096                | 4096                | 8192                | 8192                | 8192                | 8192                | 8192  |

|             | MCU DMIPS <sup>44</sup>                                                     | 200   | 220   | 242   | 266                 | 293                 | 322                 | 354                 | 390                 | 429                 | 472                 | 519                 | 571                 | 628                 | 690                 | 759   |

|             | #Sensors <sup>45</sup>                                                      | 4     | 4     | 8     | 8                   | 10                  | 10                  | 12                  | 12                  | 12                  | 12                  | 13                  | 13                  | 13                  | 13                  | 13    |

| Peripheral  | Max Sensor Power [39] $(\mu W)^{46}$                                        | 2850  | 1995  | 1397  | 1187                | 1009                | 858                 | 729                 | 671                 | 617                 | 568                 | 522                 | 480                 | 442                 | 407                 | 374   |

|             | Battery Power Density<br>(Watt-Hr/Liter)                                    | 561   | 600   | 642   | 687                 | 735                 | 787                 | 842                 | 901                 | 964                 | 1031                | 1104                | 1181                | 1263                | 1352                | 1447  |

Table SYSINT9: Summary of scaling trends of IoT driver.

## 5.2 Key challenges and promising solutions.

From the current roadmapped metrics, the SI focus team has identified the following technology challenges for the IoT driver. The key challenges and their technology solutions are summarized in Table SYSINT10, and the timeline for these solutions are summarized in Table SYSINT11.

(i) Transistor device design and scaling ("reverse" Moore) challenge: due to the extremely low power requirements for both communication and computing, the conventional Moore's Law scaling of transistors is not seen in the IoT driver. The leading technology node of the IoT driver falls behind other drivers (e.g., conventional MPU and SOC) by more than two nodes. This reverse trend is constrained by (i) the IoT device's sensitivity to energy loss during it's suspend mode; (ii) design technology that has not provided enough matched leakage reduction for the increasing transistor number. This reverse trend is a showstopper for increasing the IoT performance to meet the application requirement. Promising solutions to the transistor device scaling challenge include:

<sup>&</sup>lt;sup>35</sup> Lowest VDD consumed by the components in the system.

<sup>&</sup>lt;sup>36</sup> Suspend current of MCU, of which the always-on blocks will dominate the system suspend current.

<sup>&</sup>lt;sup>37</sup> Conversion efficiency of the integrated DC-DC converter at nominal voltage.

<sup>&</sup>lt;sup>38</sup> The spatial efficiency of the converter, which is defined as the output power divided by the circuit area. For the DC-DC converter specification, we obtain the data from a major circuit conference [51]. However, the data points are still sparse so we will keep tracking the trend.

<sup>&</sup>lt;sup>39</sup> Peak current consumed by the connectivity interface.

<sup>&</sup>lt;sup>40</sup> Transmission power for each bit, which is the energy efficiency metric for communication.

<sup>&</sup>lt;sup>41</sup> Physical footprint of the system.

<sup>&</sup>lt;sup>42</sup> Current consumption normalized to the operation frequency, which is the energy efficiency metric for the computation.

<sup>&</sup>lt;sup>43</sup> Flash (or over NVM) size to store programs, configuration, and data

<sup>&</sup>lt;sup>44</sup>DMIPS benchmark as the performance metric of MCU.

<sup>&</sup>lt;sup>45</sup> Number of sensors integrated to the system.

<sup>&</sup>lt;sup>46</sup> Total power consumed by sensors.

(a) Development of emerging devices is the primary solution for the device scaling with leakage current under control. In the recent nodes, FinFET has shown manageable leakage current while providing improved performance. As the technology nodes advance, lateral and vertical gate-all-around (LGAA and VGAA) transistors are promising since they improve the effective gate length of transistors while the device footprint is shrinking. Carbon nanotube (CNT) is the long term solution to the device scaling since its novel physical structure provides better electrical characteristics.

(b) Device scaling could be relaxed by 3D integration [49]. Emerging memory devices, such as resistive RAM (RRAM) [50], provide better durability against wearing, better integration density, and ease of integration to present back end-of-line (BEOL) technology. By means of the device innovation, the scaling challenge could be addressed.

(ii) IP/sensor integration and scaling challenge: the IoT driver is cost sensitive due to the huge amount of deployment. In order to reduce the system cost and integration effort, we have observed the requirement to reduce the component number in the system (i.e., total cost of bill of material, BOM). However, integrating extra components, such as baseband processors for communication, is constrained by the reversed Moore's Law mentioned above. Power conversion circuits, such as integrated DC-DC converters significantly improve the power efficiency and relax the power system design effort. We have observed the tendency of integrating power conversion circuits into the IoT MCUs, which also has also raised interest in the circuit design community in the recent years [51]. Promising solutions to the IP/sensor integration challenge include:

(a) Heterogeneous 3D addresses different requirements for electrical characteristics among analog, logic, MEMS, and imaging pixels, which allows system designers to integrate different substrates in limited package footprints and simplify the system level design effort.

(b) Design technology, such as on-chip passive components (e.g. inductors) over BEOL and configurable/finedgrained regulation are promising technologies to realize high efficiency on-die regulation, which will improve the power efficiency constrained by harsh limits on energy sources (i.e., energy harvesting or compact battery modules).

(iii) Supply voltage scaling challenge: the supply voltage of IoT drivers has been roadmapped to aggressively scale due to the extremely low power requirement. However, scaling is severely constrained by the two design challenges mentioned above. Since the scaling of device dimensions and threshold voltages are blocked by a lack of effective low power design technology, the supply voltage of the IoT driver is unable to be pushed lower. Meanwhile, the integrated blocks in the IoT driver, such as baseband processors and analog blocks, may have different supply voltage requirements. The constraints from device scaling and the fine-grained power domain may complicate the design of on-chip power distribution systems, which calls for improvement by design technology. Promising solutions to the supply voltage scaling challenge include several emerging computing paradigms.