# INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS 2001 EDITION

INTERCONNECT

THE INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS: 2001

## TABLE OF CONTENTS

| Scope                                      | 1  |

|--------------------------------------------|----|

| Difficult Challenges                       | 2  |

| Technology Requirements                    | 3  |

| Potential Solutions                        | 9  |

| Dielectric Potential Solutions             | 9  |

| Conductor Potential Solutions              | 11 |

| Barrier Potential Solutions                | 12 |

| Nucleation Potential Solutions             | 13 |

| Planarization Potential Solutions          | 14 |

| Etch, Strip, and Clean Potential Solutions | 17 |

| Reliability                                | 19 |

| Systems and Performance Issues             | 20 |

| Interconnect Performance                   | 20 |

| System Level Integration                   | 20 |

| New Interconnect Concepts                  | 21 |

| Design Options                             |    |

| Packaging Intermediated Interconnects      |    |

| RF/Microwave Interconnects                 |    |

| Optical Interconnects                      |    |

| 3D Interconnects                           |    |

| Radical Solutions                          |    |

| Crosscut Issues                            | 23 |

| Design                                     | 23 |

| Modeling and Simulation                    | 23 |

| Assembly and Packaging                     | 23 |

| Metrology                                  | 24 |

| Yield Enhancement                          | 24 |

| Environment, Safety, and Health            |    |

| Conclusion                                 | 25 |

## LIST OF FIGURES

| Figure 35 | Delay for Local and Global Wiring versus Feature Size | 3  |

|-----------|-------------------------------------------------------|----|

| Figure 36 | Cross-section of Hierarchical Scaling                 | 4  |

| Figure 37 | Typical ILD Architectures                             | 8  |

| Figure 38 | Dielectric Potential Solutions                        | 10 |

| Figure 39 | Conductor Potential Solutions                         | 12 |

| Figure 40 | Barrier Potential Solutions                           | 13 |

| Figure 41 | Nucleation Potential Solutions                        | 14 |

| Figure 42 | Planarization Potential Solutions                     | 16 |

| Figure 43 | Etch, Strip, and Clean Potential Solutions            | 18 |

## LIST OF TABLES

| Table 61 Interconnect Difficult Challenges                    | 2  |

|---------------------------------------------------------------|----|

| Table 62a MPU Interconnect Technology Requirements—Near-term  | 5  |

| Table 62b MPU Interconnect Technology Requirements—Long-term  | 6  |

| Table 63a DRAM Interconnect Technology Requirements—Near-term | 7  |

| Table 63b DRAM Interconnect Technology Requirements—Long-term | 7  |

| Table 64 Interconnect ESH Needs and Potential Solutions       | 25 |

## INTERCONNECT

## SCOPE

The *Interconnect* chapter of the 1994 National Technology Roadmap for Semiconductors (NTRS) described the first needs for new conductor and dielectric materials that would be necessary to meet the projected overall technology requirements. With the publication of the 1997 edition of the NTRS, the introduction of copper-containing chips was imminent. The 1999 International Roadmap highlights a continued change to new materials, now being introduced at an unprecedented pace. In 2001, these materials introductions continue, but a solution must be found for the problem associated with increases in conductor resistivity (for more detail, a link is provided to the supplemental material regarding *conductor resistivity*). Further, although the technical product driver for the smallest feature size remains the dynamic memory chip, an emerging classification of chips, system-on-a-chip, or SoC, will challenge microprocessors for increased complexity and decreased design rules. Managing this rapid rate of materials introduction and the concomitant complexity represents the overall near-term challenge. For the long term, material innovation with traditional scaling will no longer satisfy performance requirements. Interconnect innovation with optical, RF, or vertical integration combined with accelerated efforts in design and packaging will deliver the solution.

The function of an interconnect or wiring system is to distribute clock and other signals and to provide power/ground, to and among, the various circuits/systems functions on a chip. The fundamental development requirement for interconnect is to meet the high-speed transmission needs of chips despite further scaling of feature sizes. The Interconnect Technology Requirements tables have been updated to reflect the new 2001 node accelerations for both MPU and DRAM.

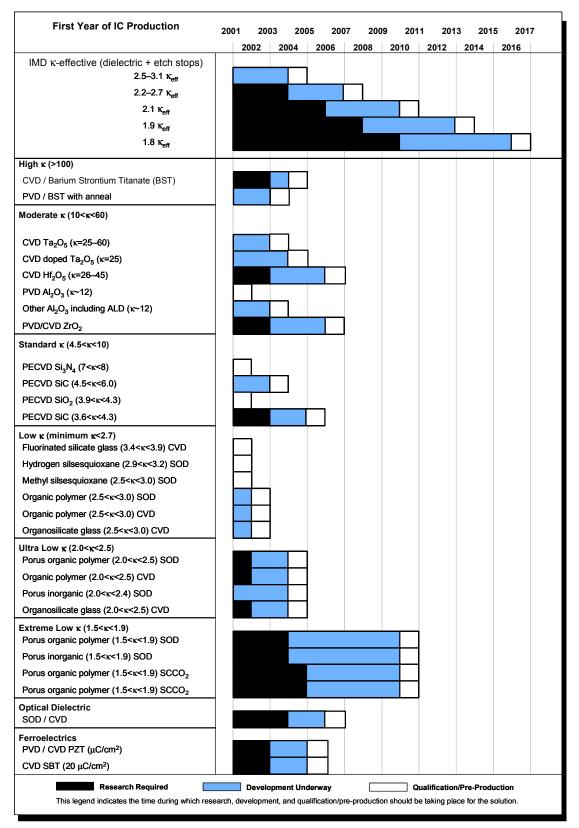

Although copper-containing chips were introduced in 1998 with silicon dioxide insulators, the lowering of insulator dielectric constant predicted by the ITRS is now firmly on track. Fluorine doped silicon dioxide ( $\kappa = 3.7$ ) was introduced at the 180 nm technology node and there will undoubtedly be insulating materials with  $\kappa = 2.6-3.0$  introduced at the 130 nm node. Since the development and integration of these new low  $\kappa$  materials is rather time invariant,  $\kappa$  values will translate to lower technology nodes with the roadmap acceleration. The  $\kappa$  values of the bulk dielectric materials are defined in the dielectric potential solutions figure and the range of effective  $\kappa$  values for the integrated dielectric stack is listed in the technology requirements tables. The introduction of these new low dielectric constant materials, along with the reduced thickness and higher conformality requirements for barriers and nucleation layers, is a difficult integration challenge. (For a more thorough explanation, access the link to the *calculation of the effective*  $\kappa$  *for various integration schemes.*)

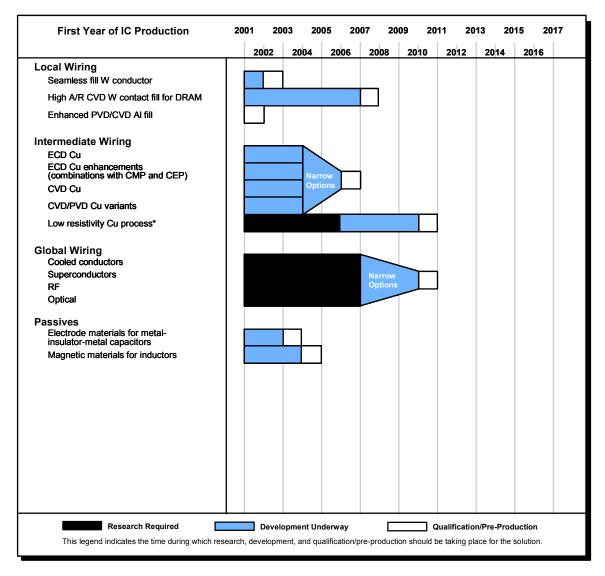

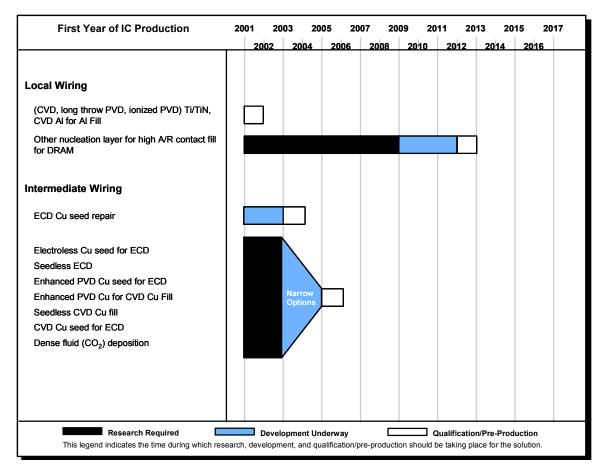

The conductor, barrier, and nucleation potential solutions have been grouped into sections for local, intermediate and global wiring levels, as well as passive devices. Atomic layer deposition (ALD), characterized by excellent conformality and thickness control, is receiving attention for applications in the deposition of barriers, nucleation layers and high  $\kappa$  dielectric materials. Other additions to conductor potential solutions include novel process tools that combine Cu electrochemical deposition (ECD) and planarization. This is particularly relevant for thick metal films used for either global wiring or inductors. Doped Cu has also emerged as a potential solution for improved Cu reliability, but this needs to be balanced against the increased Cu resistivity that occurs. Increases in Cu resistivity due to electron scattering effects will become an important factor in the long term, and is also an area of focus. Links to <u>expanded references to ALD</u> are included as supplemental material.

Figure 43 covers etch, strip, and cleans potential solutions, acknowledging the increased integration challenges of these steps. For example, the etch solution for a dual-Damascene structure with and without an embedded trench etch stop are different. Requirements for pre-etch and post-etch clean, which might utilize novel approaches such as super critical  $CO_{2}$ , have been expanded. Plasma (HDP) etch has been de-emphasized in this Roadmap.

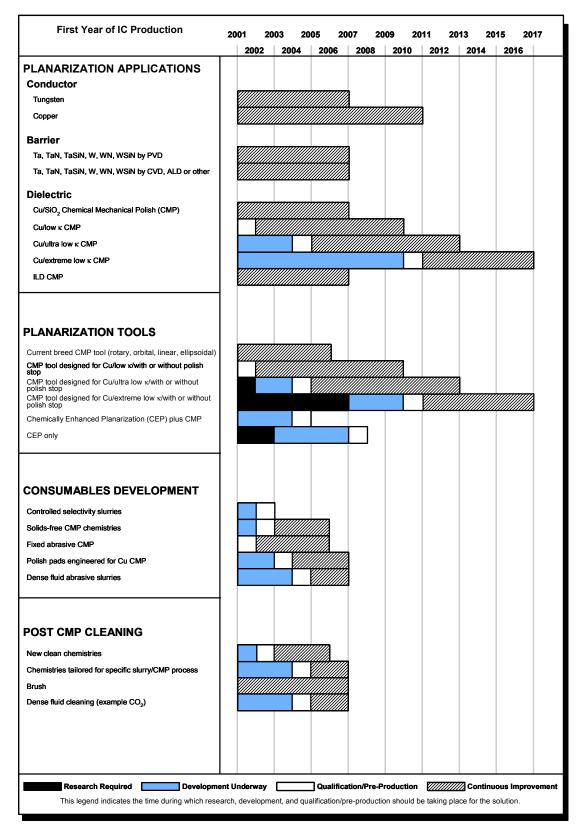

Planarization potential solutions contain a more detailed discussion of chemically enhanced planarization (CEP). One of the primary integration challenges with low  $\kappa$  materials is adhesion failure of barrier or capping materials with the dielectric during planarization. Porous low  $\kappa$  materials are even more problematic and are therefore one of the key focus areas for planarization development efforts. A more detailed <u>schematic on the dishing/erosion/thinning metrics</u> shown in the technology requirements tables is found in the supplemental material link.

## **DIFFICULT CHALLENGES**

Table 61 highlights and differentiates the five key challenges in the near term ( $\geq 65$  nm) and long term (< 65 nm). In the near term, the most difficult challenges for interconnect include the rapid introduction and integration of new materials and processes, dimensional control, physical/electrical reliability of interconnect structures, and interconnect processes with low or no device impact. The introduction of new low  $\kappa$  dielectrics, chemical vapor deposition (CVD) metal/barrier/seed layers, and additional elements for SoC, provide significant process and process integration challenges. Interfaces, contamination, adhesion, mechanical stability, electrical parametrics, and thermal budget, confounded by the number of wiring levels for interconnect, ground planes and passive elements, create a difficult-to-manage complexity.

| Five Difficult Challenges ≥65 nm / Through 2007                                         | SUMMARY OF ISSUES                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Introduction of new materials*                                                          | The rapid introduction of new materials/processes that are necessary to meet conductivity requirements and reduce the dielectric permittivity create integration and material characterization challenges.                                                                                                                                                                                                                                   |

| Integration of new processes and structures*                                            | Combinations of materials and processes used to fabricate new structures create integration complexity.                                                                                                                                                                                                                                                                                                                                      |

| Achieving necessary reliability                                                         | New materials, structures, and processes create new chip reliability<br>(electrical, thermal, and mechanical) exposure. Detecting, testing,<br>modeling and control of failure mechanisms will be key.                                                                                                                                                                                                                                       |

| Attaining dimensional control                                                           | Three-dimensional control (3D CD), with its associated metrology, of<br>interconnect features is necessary for circuit performance and<br>reliability. The multiplicity of levels combined with new<br>materials, reduced feature size and pattern dependent processes<br>create this challenge.                                                                                                                                             |

| Manufacturability and defect management that meet overall cost/performance requirements | As feature sizes shrink, interconnect processes must be compatible with<br>device roadmaps and meet manufacturing targets at the specified<br>wafer size. Plasma damage, contamination, thermal budgets,<br>cleaning of high A/R features, defect tolerant processes,<br>elimination/reduction of control wafers are key concerns. Where<br>appropriate, global wiring and packaging concerns will be<br>addressed in an integrated fashion. |

| FIVE DIFFICULT CHALLENGES <65 nm / BEYOND 2007                                          | SUMMARY OF ISSUES                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Dimensional control and metrology                                                       | Multi-dimensional control and metrology of interconnect features is necessary for circuit performance and reliability.                                                                                                                                                                                                                                                                                                                       |

| Patterning, cleaning, and filling high aspect ratios features                           | As features shrink, etching, cleaning, and filling high aspect ratio structures<br>will be challenging, especially for low κ dual-Damascene metal<br>structures and DRAM.                                                                                                                                                                                                                                                                    |

| Integration of new processes and structures                                             | Combinations of materials and processes used to fabricate new structures<br>create integration complexity. The increased number of levels<br>exacerbate thermomechanical effects. Novel/active devices may<br>be incorporated into the interconnect.                                                                                                                                                                                         |

| Continued introductions of new materials and size effects                               | Further introductions of materials/processes are expected. Microstructure<br>and dimensional effects become important when Cu/low κ<br>interconnect is extended to smaller features.                                                                                                                                                                                                                                                         |

| Identify solutions which address global wiring scaling issues*                          | Traditional interconnect scaling will no longer satisfy performance<br>requirements. Defining and finding solutions beyond copper and<br>low K will require material innovation, combined with<br>accelerated design, packaging and unconventional interconnect.                                                                                                                                                                             |

| Table 61 Interconnect Difficult Challenges | Table 61 | Interconnect | Difficult | Challenges |

|--------------------------------------------|----------|--------------|-----------|------------|

|--------------------------------------------|----------|--------------|-----------|------------|

\* Top three challenges

Dimensional control is a key challenge for present and future interconnect technology generations. The dominant architecture, Damascene, requires tight control of pattern, etch and planarization. To extract maximum performance, interconnect structures cannot tolerate variability in profiles without producing undesirable RC degradation. These dimensional control requirements place new demands on high throughput imaging metrology for measurement of high aspect ratio structures. New metrology techniques are also needed for inline monitoring of adhesion and defects. Larger wafers and the need to limit test wafers will drive the adoption of more *in situ* process control techniques. Dimensional

control, a challenge now, will become even more critical as new materials, such as porous low  $\kappa$  dielectrics and CVD metals, play a role at the tighter pitches and higher A/R (aspect ratio) of intermediate and global levels. At the 45 nm node, feature size effects, such as electron surface scattering, will increase the effective resistivity and new conductor technologies may be required. Cu and low  $\kappa$  will continue to find applications in future chip generations, but for global wiring, new interconnect solutions incorporating RF or optical propagation will be required, bringing even more material and process integration challenges.

Feature size reduction, new materials, and Damascene structures all challenge metrology for on-chip interconnect development and manufacture. Critical dimension measurements are needed for very high aspect ratio features and ultrathin barriers. Methods must be developed to accommodate the increased complexity of the wiring levels of future chips. Other metrology challenges include measuring resistivity and dielectric constant at high frequency, adhesion and mechanical properties.

## **TECHNOLOGY REQUIREMENTS**

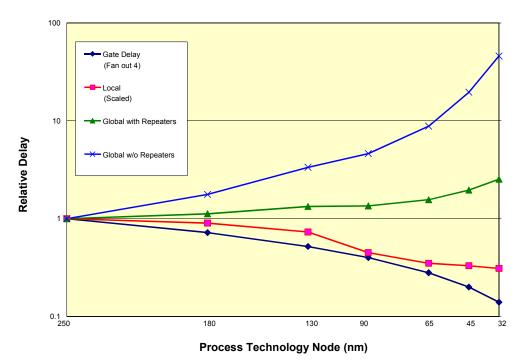

To adequately describe the wiring needs of interconnect, near term (2001–2007) and long term (2010–2016) technology requirements and potential solutions are addressed for two specific classes of products: high performance microprocessors (HP MPU) and dynamic memory (DRAM [Tables 62–63]. For MPUs, local, intermediate, and global wiring pitches/aspect ratios are differentiated to highlight a hierarchical scaling methodology that has been broadly adopted. Implementation of copper and low  $\kappa$  materials allows scaling of the intermediate wiring levels and minimizes the impact on wiring delay. Local wiring levels are relatively unaffected by traditional scaling. RC delay, however, is dominated by global interconnect and the benefit of materials changes alone is insufficient to meet overall performance requirements. Figure 35 shows the delay of local and global wiring in future generations. Repeaters can be incorporated to mitigate the delay in global wiring but consume power and chip area.

Figure 35 Delay for Local and Global Wiring versus Feature Size

In the long term, new design or technology solutions (such as co-planar waveguides, free space RF, optical interconnect) will be needed to overcome the performance limitations of traditional interconnect. Inductive effects will also become increasingly important as frequency of operation increases, and additional metal patterns or ground planes may be required for inductive shielding. As supply voltage is scaled or reduced, crosstalk has become an issue for all clock and signal wiring levels; the near term solution adopted by the industry is the use of thinner metallization to lower line-to-line

capacitance. This approach is more effective for the lower resistivity copper metallization, where reduced aspect ratios (A/R) can be achieved with less sacrifice in resistance as compared with aluminum metallization. The 2001 Roadmap continues to reflect the design trend featuring reduced aspect ratios (as an alternative means of reducing capacitance) and less aggressive scaling of dielectric. The latter change expands the development window to address the difficulty in integrating low  $\kappa$  dielectrics into a Damascene architecture.

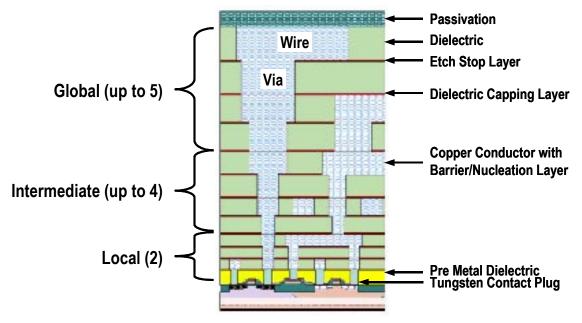

MPUs utilize a high number of metal layers; designers are adopting a hierarchical wiring approach with steadily increasing pitch and thickness at each conductor level to alleviate the impact of interconnect delay on performance. Refer to Figure 36.

Figure 36 Cross-section of Hierarchical Scaling

To accommodate the need for ground planes or on-chip decoupling capacitors, the growth of metal levels is projected to increase beyond those specified solely to meet performance requirements. Copper wire aspect ratios are lower than those for Al, which provides for a reduction in line-to-line capacitance and crosstalk but leads to higher wire resistance. Aspect ratios of features at the global levels will be comparable for both copper and aluminum conductor solutions, to minimize delay. Refer to Table 62a and b. More information regarding *optional levels* is provided through a link to supplemental files.

| YEAR OF PRODUCTION                                                                                                        | 2001    | 2002    | 2003    | 2004    | 2005    | 2006    | 2007    |

|---------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|

| DRAM ½ PITCH (nm)                                                                                                         | 130     | 115     | 100     | 90      | 80      | 70      | 65      |

| MPU/ASIC <sup>1</sup> / <sub>2</sub> PITCH (nm)                                                                           | 150     | 130     | 107     | 90      | 80      | 70      | 65      |

| MPU PRINTED GATE LENGTH (nm)                                                                                              | 90      | 75      | 65      | 53      | 45      | 40      | 35      |

| MPU PHYSICAL GATE LENGTH (nm)                                                                                             | 65      | 53      | 45      | 37      | 32      | 28      | 25      |

| Number of metal levels                                                                                                    | 8       | 8       | 8       | 9       | 10      | 10      | 10      |

| Number of optional levels-ground planes/capacitors                                                                        | 2       | 2       | 4       | 4       | 4       | 4       | 4       |

| Total interconnect length (m/cm <sup>2</sup> )—active wiring only, excluding global levels [1]                            | 4086    | 4843    | 5788    | 6879    | 9068    | 10022   | 11169   |

| FITs/m length/cm <sup>2</sup> × 10 <sup>-3</sup> excluding global levels [2]                                              | 1.22    | 1.03    | 0.86    | 0.73    | 0.55    | 0.50    | 0.45    |

| Jmax (A/cm <sup>2</sup> )—wire (at 105°C)                                                                                 | 9.6E5   | 1.1E6   | 1.3E6   | 1.5E6   | 1.7E6   | 1.9E6   | 2.1E6   |

| Imax (mA)—via (at 105°C)                                                                                                  | 0.32    | 0.29    | 0.27    | 0.24    | 0.22    | 0.20    | 0.18    |

| Local wiring pitch (nm)                                                                                                   | 350     | 295     | 245     | 210     | 185     | 170     | 150     |

| Local wiring A/R (for Cu)                                                                                                 | 1.6     | 1.6     | 1.6     | 1.7     | 1.7     | 1.7     | 1.7     |

| Cu thinning at minimum pitch due to erosion (nm),<br>$10\% \times$ height, 50% areal density, 500 µm square array         | 28      | 24      | 20      | 18      | 16      | 14      | 13      |

| Intermediate wiring pitch (nm)                                                                                            | 450     | 380     | 320     | 265     | 240     | 215     | 195     |

| Intermediate wiring dual Damascene A/R<br>(Cu wire/via)                                                                   | 1.6/1.4 | 1.6/1.4 | 1.7/1.5 | 1.7/1.5 | 1.7/1.5 | 1.7/1.6 | 1.8/1.6 |

| Cu thinning at minimum intermediate pitch due to<br>erosion (nm), 10% × height,<br>50% areal density, 500 µm square array | 36      | 30      | 27      | 23      | 20      | 18      | 18      |

| Minimum global wiring pitch (nm)                                                                                          | 670     | 565     | 475     | 460     | 360     | 320     | 290     |

| Global wiring dual Damascene A/R (Cu wire/via)                                                                            | 2.0/1.8 | 2.0/1.8 | 2.1/1.9 | 2.1/1.9 | 2.2/2.0 | 2.2/2.0 | 2.2/2.0 |

| Cu thinning global wiring due to dishing and erosion (nm), $10\% \times$ height, 80% areal density, 15 µm wide wire       | 67      | 57      | 50      | 48      | 40      | 35      | 32      |

| Cu thinning global wiring due to dishing (nm),<br>100 µm wide feature                                                     | 40      | 34      | 30      | 29      | 24      | 21      | 19      |

| Conductor effective resistivity $(\mu\Omega\text{-cm})$ Cu intermediate wiring                                            | 2.2     | 2.2     | 2.2     | 2.2     | 2.2     | 2.2     | 2.2     |

| Barrier/cladding thickness<br>(for Cu intermediate wiring) (nm) [3]                                                       | 16      | 14      | 12      | 10      | 9       | 8       | 7       |

| Interlevel metal insulator<br>—effective dielectric constant (κ)                                                          | 3.0-3.6 | 3.0–3.6 | 3.0–3.6 | 2.6–3.1 | 2.6–3.1 | 2.6–3.1 | 2.3–2.7 |

| Interlevel metal insulator (minimum expected)<br>—bulk dielectric constant (κ)                                            | <2.7    | <2.7    | <2.7    | <2.4    | <2.4    | <2.4    | <2.1    |

Table 62a MPU Interconnect Technology Requirements—Near-term

White-Manufacturable Solutions Exist, and Are Being Optimized

Yellow-Manufacturable Solutions are Known

Notes for Table 62a and b

[1] Calculated by assuming that only one of every three minimum pitch wiring tracks for local and semiglobal wiring levels are populated. The wiring lengths for each level are then summed to calculate the total inteconnect length per square centimeter of active area.

[2] This metric is calculated by assuming that a 5 FIT reliability budget is apportioned to interconnect for the highest reliability grade MPUs. This number is then divided by the total interconnect length to arrive at the FITs per meter of wiring per one square centimeter of active area.

[3] Calculated for a conformal layer in intermediate wiring to meet minimum effective conductor resistivity

| YEAR OF PRODUCTION                                                                                                             | 2010           | 2013    | 2016    |

|--------------------------------------------------------------------------------------------------------------------------------|----------------|---------|---------|

| DRAM <sup>1</sup> / <sub>2</sub> PITCH (nm)                                                                                    | 45             | 32      | 22      |

| MPU/ASIC 1/2 PITCH (nm)                                                                                                        | 45             | 32      | 22      |

| MPU PRINTED GATE LENGTH (nm)                                                                                                   | 25             | 18      | 13      |

| MPU PHYSICAL GATE LENGTH (nm)                                                                                                  | 18             | 13      | 9.0     |

| Number of metal levels                                                                                                         | 10             | 11      | 11      |

| Number of optional levels - ground planes/capacitors                                                                           | 4              | 4       | 4       |

| Total interconnect length (m/cm <sup>2</sup> ) – active wiring only, excluding global levels [1]                               | 16063          | 22695   | 33508   |

| FITs/m length/cm <sup>2</sup> $\times$ 10 <sup>-3</sup> excluding global levels [2]                                            | 0.31           | 0.22    | 0.15    |

| Jmax (A/cm <sup>2</sup> )—wire (at 105°C)                                                                                      | 2.7E6          | 3.3E6   | 3.9E6   |

| Imax (mA)—via (at 105°C)                                                                                                       | 0.10           | 0.07    | 0.04    |

| Local wiring pitch (nm)                                                                                                        | 105            | 75      | 50      |

| Local A/R (for Cu)                                                                                                             | 1.8            | 1.9     | 2.0     |

| Cu thinning at minimum pitch due to erosion (nm), $10\% \times$ height, 50% areal density, 500 µm square array                 | 5              | 4       | 3       |

| Intermediate wiring pitch (nm)                                                                                                 | 135            | 95      | 65      |

| Intermediate wiring dual Damascene A/R (Cu wire/via)                                                                           | <b>1.8/1.6</b> | 1.9/1.7 | 2.0/1.8 |

| Cu thinning at minimum intermediate pitch due to erosion (nm),<br>$10\% \times$ height, 50% areal density, 500 µm square array | 12             | 9       | 7       |

| Minimum global wiring pitch (nm)                                                                                               | 205            | 140     | 100     |

| Global wiring dual-Damascene A/R (Cu wire/via)                                                                                 | 2.3/2.1        | 2.4/2.2 | 2.5/2.3 |

| Cu thinning global wiring due to dishing and erosion (nm),<br>$10\% \times$ height, 80% areal density, 15 µm wide wire         | 24             | 17      | 13      |

| Cu thinning global wiring due to dishing (nm), $100 \ \mu m$ wide feature                                                      | 14             | 10      | 8       |

| Conductor effective resistivity<br>(μΩ-cm) Cu intermediate wiring                                                              | 2.2            | 2.2     | 2.2     |

| Barrier/cladding thickness<br>(for Cu intermediate wiring) (nm) [3]                                                            | 5              | 3.5     | 2.5     |

| Interlevel metal insulator—effective dielectric constant ( $\kappa$ )                                                          | 2.1            | 1.9     | 1.8     |

| Interlevel metal insulator (minimum expected)<br>—bulk dielectric constant (κ)                                                 | <1.9           | <1.7    | <1.6    |

Table 62b MPU Interconnect Technology Requirements—Long-term

White–Manufacturable Solutions Exist, and Are Being Optimized Yellow–Manufacturable Solutions are Known Red–Manufacturable Solutions are NOT Known

|                                                                  | Tuble of a Dillin interconnect reennotes, nequinements intera term |         |         |         |         |         |         |  |

|------------------------------------------------------------------|--------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|--|

| YEAR OF PRODUCTION                                               | 2001                                                               | 2002    | 2003    | 2004    | 2005    | 2006    | 2007    |  |

| DRAM <sup>1/2</sup> PITCH (nm)                                   | 130                                                                | 115     | 100     | 90      | 80      | 70      | 65      |  |

| MPU/ASIC 1/2 PITCH (nm)                                          | 150                                                                | 130     | 107     | 90      | 80      | 70      | 65      |  |

| MPU PRINTED GATE LENGTH (nm)                                     | 90                                                                 | 75      | 65      | 53      | 45      | 40      | 35      |  |

| MPU PHYSICAL GATE LENGTH (nm)                                    | 65                                                                 | 53      | 45      | 37      | 32      | 28      | 25      |  |

| Number of metal levels                                           | 3                                                                  | 3–4     | 4       | 4       | 4       | 4       | 4       |  |

| Contact A/R-stacked capacitor                                    | 11.4                                                               | 11.9    | 12.4    | 13.0    | 13.6    | 14.3    | 15.2    |  |

| Local wiring pitch (nm) non-contacted                            | 260                                                                | 230     | 200     | 180     | 160     | 150     | 130     |  |

| Specific contact resistance ( $\Omega$ -cm <sup>2</sup> )        | 1.5E-7                                                             | 1.3E-7  | 1.0E-7  | 8.0E-8  | 7.0E-8  | 6.0E-8  | 5.0E-8  |  |

| Specific via resistance ( $\Omega$ -cm <sup>2</sup> )            | 2E-9                                                               | 1.4E-9  | 1.0E-9  | 9.0E-10 | 7.0E-10 | 6.0E-10 | 5.0E-10 |  |

| Conductor effective resistivity $(\mu\Omega\text{-cm})$          | 3.3                                                                | 3.3     | 3.3     | 2.2     | 2.2     | 2.2     | 2.2     |  |

| Interlevel metal insulator—<br>effective dielectric constant (κ) | 4.1                                                                | 3.0-4.1 | 3.0–4.1 | 3.0–4.1 | 3.0-4.1 | 2.6–3.1 | 2.6–3.1 |  |

Table 63a DRAM Interconnect Technology Requirements—Near-term

Table 63b DRAM Interconnect Technology Requirements—Long-term

| YEAR OF PRODUCTION                                                    | 2010                 | 2013    | 2016    |

|-----------------------------------------------------------------------|----------------------|---------|---------|

| DRAM ½ PITCH (nm)                                                     | 45                   | 32      | 22      |

| MPU/ASIC ½ PITCH (nm)                                                 | 45                   | 32      | 22      |

| MPU PRINTED GATE LENGTH (nm)                                          | 25                   | 18      | 13      |

| MPU PHYSICAL GATE LENGTH (nm)                                         | 18                   | 13      | 9.0     |

| Number of metal levels                                                | 4                    | 4       | 4       |

| Contact A/R—stacked capacitor                                         | <b>16.1</b>          | 19.3    | 23.2    |

| Local wiring pitch (nm) non-contacted                                 | 90                   | 64      | 44      |

| Specific contact resistance ( $\Omega$ -cm <sup>2</sup> )             | 4.0E-8               | 2.0E-8  | 1.0E-8  |

| Specific via resistance ( $\Omega$ -cm <sup>2</sup> )                 | 5E-10                | 3E-10   | 1.0E-10 |

| Conductor effective resistivity (µΩ-cm)                               | 2.2                  | 2.2     | 2.2     |

| Interlevel metal insulator—effective dielectric constant ( $\kappa$ ) | <mark>2.3–2.7</mark> | 2.3–2.7 | 2.1     |

White–Manufacturable Solutions Exist, and Are Being Optimized Yellow–Manufacturable Solutions are Known Red–Manufacturable Solutions are NOT Known

DRAM interconnect technology reflects the most aggressive metal pitch and highest aspect ratio contacts and will continue to provide the most significant challenges in dimensional control and defect management (refer to Table 63). The introduction of low  $\kappa$  dielectric materials at the 115 nm ½ pitch and copper at the 90 nm ½ pitch is required to meet the performance of high speed memory products. However, the pricing sensitivity of the marketplace may delay introduction if cost savings associated with copper are not realized. This suggests that capability for aluminum processing must be continuously improved and extended.

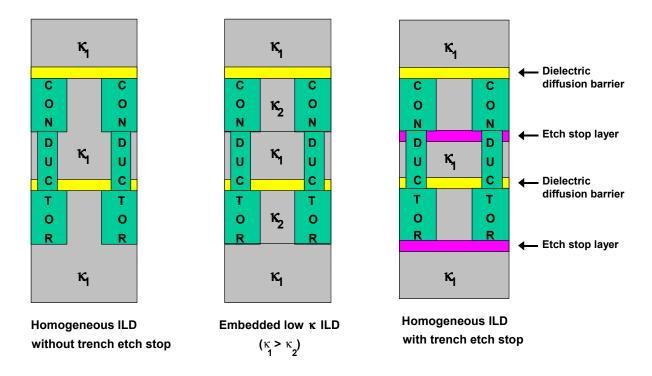

Damascene processing flows dominate MPU/ASIC fabrication methodologies and usage in DRAM is expected to broaden. Figure 37 illustrates several typical interlevel dielectric (ILD) architectures available to create the interconnect wiring levels. While current copper Damascene processes utilize physical vapor deposited (PVD) Ta-based barriers and Cu nucleation layers, continued scaling of feature size requires development of other materials and nucleation layer deposition solutions. Continuous improvement of tools and chemistries will extend electrochemically deposited Cu (ECD) to the 22 nm generation but small, high A/R features necessitate the simultaneous development and subsequent selection of alternative filling techniques. A thin barrier is also needed to maintain the effective conductor resistivity in these features. Nucleation layer conformality requirements become more stringent to enable Cu ECD filling of Damascene

features. Surface segregated, CVD, ALD, and dielectric barriers represent intermediate potential solutions; zero thickness barriers are desirable but not required.

Near-term dielectric needs include lower permittivity materials for wire insulators and etch stops, higher permittivity materials for decoupling and metal insulator metal (MIM) capacitors and materials with high remanent polarization for ferroelectric memories. The thermal, mechanical, and electrical properties of these new materials present a formidable challenge for process integration. In the longer term, dielectric characteristics at high frequency will become more important, and optical materials will be required that have sufficient optical contrast to serve as low-loss waveguides.

#### Figure 37 Typical ILD Architectures

Continuous improvement in dielectric CMP and post-CMP defect reduction will be needed in the near term. The development of alternative planarization techniques is a potential long-term solution. For copper CMP, minimization of erosion and dishing will be necessary to meet performance needs as the wiring thickness is scaled. Planarization processes (with associated end-point) that are compatible with low  $\kappa$  dielectrics that may have low density and poor mechanical strength must be developed. Improvements in post-CMP clean will be critical in achieving the low defect densities required for future devices. Etch, resist strip, and post-etch cleans must be developed that maintain the desired selectivity to etch stop layers and diffusion barriers, but which do not degrade low  $\kappa$  dielectrics. Low or no device damage during etch and deposition processes is the goal, especially as thinner gate oxides and/or new gate dielectric materials are introduced.

## **POTENTIAL SOLUTIONS**

#### DIELECTRIC POTENTIAL SOLUTIONS

The *1999 ITRS* indicated the need for a substantial change in the dielectric materials used in ICs and the 2001 Roadmap will substantiate the occurrence of this change. All ranges of material permittivity (from  $\kappa > 100$  to  $\kappa < 2$ ) are under discussion and development with materials having  $\kappa > 20$  and  $\kappa < 3$  being commercially implemented in 2001. The  $\kappa$  values in this document are bulk film permittivity values unless otherwise indicated. Effective values,  $\kappa_{eff}$ , are defined later. The following three overall dielectric challenges remain valid throughout the 15-year scope of this roadmap:

- Development and integration of high  $\kappa$  materials and processes to achieve the maximum permittivity for standalone memory applications, decoupling and (MIM) capacitors for MPU/ASICs and system-on-a-chip (SoC)

- Development and integration of low  $\kappa$  materials and processes to achieve the minimum possible permittivity ( $\kappa_{eff}$ ) primarily for Cu dual-Damascene technology

- Development and integration of new materials for emerging technologies to replace conventional wiring with alternatives, such as RF and optical interconnect.

Higher  $\kappa$  materials will be targeted for BEOL decoupling capacitors in logic and SoC beginning at the 130 nm node. The driver of increased permittivity to support a conservation of interconnect real estate must be balanced with compatibility requirements of these higher  $\kappa$  materials with the evolving BEOL process technologies. The primary focus will be on thermal, mechanical, and stress properties of these films. Topographical challenges associated with multi-layer capacitor structures may require CMP development. The technical requirements of these materials consist of frequency invariance of permittivity matched to the device operating needs, low electrical leakage, *I-V* linearity and available/compatible electrode materials. CVD tantalum oxide is the most widely used of the commercially implemented high  $\kappa$  materials, with multiple supplier support. Development of aluminum oxide (MIM) structures continues. Perovskites (BST, PZT) still require additional development to reduce process temperatures while achieving higher permittivity values.

Low  $\kappa$  FSG ( $\kappa$ =3.7) materials have been in production since the 250 nm node, and were introduced into the 180 nm node with Cu dual Damascene. The measurable performance benefit derived from FSG, spurred the aggressive introduction of lower  $\kappa$  materials ( $\kappa$ <3.0) at the 130 nm node, with organic spin-on-polymers (SOP) and both spin-on and PECVD inorganic/organic hybrid materials. These materials have been commercially implemented as monolithic dielectric layers, dual layers with an intermediate etch stop layer and as hybrid dielectric layers with USG at the via level. The most challenging integration modules are dielectric etch, integrated clean, CMP, and packaging.

Lower  $\kappa$  dielectric materials ( $\kappa$ <2.5) are in development. Integration efforts focus on solving the problems of these reduced density materials with their compromised thermal and mechanical properties. This inevitable trend in density reduction is most troublesome for CMP and packaging. Although incorporation of fluorine into low  $\kappa$  materials reduces dielectric constant approximately 10%, further reductions in FSG were found to be incompatible with refractory metal liner materials; the use of fluorine-containing ULK and ELK materials must therefore be carefully considered. The ideal ultra-low  $\kappa$  material ( $\kappa$ <2.5) will have a closed pore structure and uniformly distributed pores with a maximum pore size, tied to, and decreasing with, technology node. A tight pore size distribution is also desirable.

The effective permittivity encountered by the signal in the interconnect structure is the most important parameter, and this has as much to do with the integration scheme as the permittivity of the bulk interlayer dielectric. Each material in the ILD stack contributes to the  $\kappa_{eff}$  (etch stop, Cu capping layer and hard mask (s). Novel integration schemes may still be required, in addition to these ultra low  $\kappa$  materials, to realize a  $\kappa_{eff}$  of 2.0 or less.

RF and optical interconnect are the leading technologies poised to replace conventional wiring and alleviate the global interconnect problem. Oxide-based optical interconnects are a logical step, but current deposition technologies are incapable of producing material of sufficient quality for direct implementation. Transition metal purity and hydroxol content must improve by several orders of magnitude, in some cases, to meet acceptable loss targets. The challenge for polymeric materials will be achievement of sufficient refractive index contrast between core and cladding layers to ensure low loss at small radius turns. The conversion efficiencies (electron to photon and photon to electron) still need to be significantly improved for insertion at design frequencies greater than 10 GHz. One advantage of optical interconnects is the application of wavelength and frequency multiplexing of signals simultaneously on the same interconnect. Local (on chip) RF is also being explored.

Figure 38 Dielectric Potential Solutions

#### **CONDUCTOR POTENTIAL SOLUTIONS**

Tungsten will continue to be used for local wiring and for the contact level to the devices in microprocessors, ASICs and DRAMs. ALD, in conjunction with CVD techniques, will be utilized first in the W deposition area to accomplish a seamless W fill. These same techniques, with more emphasis on ALD, need to be employed to accomplish W fill of high aspect ratio (15:1 in 2007) contacts for stacked capacitor DRAM designs. Other materials and techniques may ultimately be needed to address the long-term requirements of DRAM stacked capacitor contacts, which are projected to have aspect rations greater than 20:1 by 2016. Aluminum may continue to be used for local wiring. Enhanced CVD/PVD flow techniques may also be utilized for Damascene architectures. Cu will also be used for local wiring levels and these will be the first to be impacted by the size effects that will increase Cu resistivity toward the end of the period covered by the 2001 ITRS.

Cu will be the preferred solution for the intermediate wiring levels in microprocessors and ASICs and electrochemical deposition will continue to dominate the market in the near term. CVD Cu fill may become competitive as a fill technology if the same "superfilling" behavior and microstructure characteristic of ECD can be achieved. At the intermediate wiring pitches predicted for the long-term years of this Roadmap, size effects will also increase Cu resistivity for intermediate wiring levels. This is much more problematic since intermediate wiring traverses longer lengths and is much more likely to impact performance than local wiring. Cu interfaces, microstructures and impurity levels will be engineered to alleviate the impact of this resistivity rise for a few additional technology generations.

Global wiring levels, with their much larger linewidths, will be the last to be impacted by size effects in Cu. However, scaling at each technology generation has the largest impact on global wiring levels that nominally traverse lengths on the order of the die size. This problem is currently being addressed by the judicious use of repeaters, or by oversized drivers, which impact both chip size and power. Future potential solutions include RF, optical, cooled conductors and superconductors, which are expected to be introduced into manufacturing at the beginning of the long-term years of this Roadmap.

The increasing market for wireless devices and telecom applications will spur a focus on processes and materials for passive devices within the interconnect structure. In particular, there will be a focus on new processes and materials for forming the electrodes of metal-insulator-metal (MIM) capacitors to improve yield and reliability. Both Al and Cu are currently in use for standard spiral inductors, but in the future various magnetic materials may emerge with different inductor designs to reduce the area of these devices.

\*Cu process with optimized interfaces, microstructure and impurities to alleviate resistivity rise at small critical dimensions

Figure 39 Conductor Potential Solutions

#### **BARRIER POTENTIAL SOLUTIONS**

Ti/TiN will continue to be used as the contact and for barrier materials for high aspect ratio contacts (e.g., DRAM stacked capacitor) filled with W conductor. Long throw and ionized PVD, as well as CVD and ALD techniques, will be developed as potential solutions in this area. In addition, surface treatments of the TiN with  $SiH_4$  and other gaseous species will be used to enhance nucleation of the subsequently deposited CVD or ALD W film.

The barrier materials used for Cu wiring will continue to be selected from the nitrides and silicon nitrides of Ta, Ti, and W. Long throw, ionized PVD and CVD deposition will continue to be the predominate solutions. However, ALD deposition methods will emerge as the dominant solutions because of their superior conformality and improved thickness control. In addition, elimination of deposited barriers may be possible through *in situ* treatment of the etched low  $\kappa$  dielectric sidewall to form an effective barrier to Cu diffusion. Barriers will undoubtedly be a key focus area toward the long term years of this Roadmap, since engineering the smoothness and other properties of the Cu barrier interface will be key to ameliorating the expected Cu resistivity increase due to electron scattering effects.

Figure 40 Barrier Potential Solutions

#### **NUCLEATION POTENTIAL SOLUTIONS**

PVD Cu deposited through either long throw or various ionized PVD techniques continues to be the dominant nucleation layer for ECD Cu. Since these PVD techniques yield marginal coverage on next generation dual Damascene structures, electroless and ECD Cu seed layer repair are being developed as nucleation solutions over the next few years. As a more extendible solution to the issue of seed conformality in high aspect ratio structures, electroless Cu seed, direct ECD plating on barriers—such as seedless ECD, CVD Cu seed, and enhanced PVD seeds—are being pursued. These are expected to emerge and be ready for manufacturing by the 65 nm technology node. Figure 41 shows the nucleation potential solutions chart.

Figure 41 Nucleation Potential Solutions

### PLANARIZATION POTENTIAL SOLUTIONS

Planarization continues to be a critical and enabling step for interconnect technology. As the materials comprising the interconnects become less conventional and the demands on planarization tolerances become more exacting, the planarization processes themselves become more closely coupled to the choice of an integration scheme. Chemical-mechanical polishing remains the leading planarization technology in current and future manufacturing.

The CMP of silicon dioxide for ILD and pre-metal dielectrics and CMP of tungsten for plugs/local interconnect will remain a requirement for the foreseeable future. The accelerating industry movement to Cu Damascene technology has resulted in the need for Cu CMP processes that address advanced material requirements spanning three technology nodes: Cu/SiO<sub>2</sub>, Cu/low  $\kappa$  dielectrics, and Cu/ultra-low  $\kappa$  dielectrics. Each of these BEOL material sets brings new metal planarization challenges. Among these is the need to reduce the mechanical forces applied to the wafer during CMP, in order to prevent adhesive/cohesive failures in the dielectric, due to the reduced mechanical strength of many porous ULK dielectrics. Although this problem can be alleviated through integration choices, an effective dielectric constant performance penalty is likely.

As minimum wire dimensions scale with each new technology node, the primary influence that planarization has on control of wire thickness becomes increasingly important. Thinning of the local and intermediate Cu wiring at minimum pitch is a result of pattern erosion during CMP. Thinning of the global wiring results from both pattern erosion and dishing of the individual wires. With the projected scaling of wire thickness, it is likely that Cu thinning due to CMP must be limited to less than 10% of the nominal thickness for any interconnect level. For the wide global features, Cu dishing from CMP results in localized non-planarity, leading to conductive defects at subsequent interconnect layers. Tighter control of metal planarization will need to be addressed by improvements in all facets of CMP, including tools (end point, removal non-uniformity, process parameters), slurries (selectivity), and pads (planarization lengths).

Related links are provided for *thinning of the local and intermediate Cu wiring at minimum pitch*; thinning of the *global wiring from both pattern erosion and dishing of the individual wires*, and *wide global features and Cu dishing from CMP*.

Development will continue in alternative metal planarization techniques, sometimes referred to as Chemically Enhanced Planarization (CEP) and the similar spin-etch planarization (SEP). These two approaches use controlled chemical etching of metals to avoid some of the disadvantages associated with CMP processing, such as dielectric erosion. They may also employ electrochemical and diffusion-controlled chemical reactions for planarizing. Combining CEP/SEP with conventional CMP may be particularly useful for productivity enhancements and compatibility with weak/porous dielectrics.

Planarization tools for metal CMP must evolve so that Cu can be polished in the advanced dielectrics. The current breed tools all control relative speed and distributed force to the wafer surface, with techniques to enhance cross-wafer slurry transport. Various polish endpoint detection techniques are used, with inline dielectric thickness metrology as an available option. Integrated wafer cleaning is a popular architecture for metal planarization tools. It is important that future tools be designed for processing Cu in low  $\kappa$  and ultra low  $\kappa$  dielectrics. In addition to the above features, the next generation tool for manufacturing may include tribological metrology to measure frictional forces, and *in situ* (or inline) metrology for dielectric and metal thickness, planarity, defects/residuals, and reliable full-wafer endpoint detection for both Cu and barrier films. These features will enable a machine-tunable, radially uniform, polish and allow an improved implementation of automatic process control (APC). The polisher is likely to have fully integrated slurry metrology and to incorporate a number of "green tool" features. Beyond the next generation, the futuristic CMP tool may be specifically designed to operate in a low-shear-force region of the CMP process space. This may require novel tool designs. Tribological metrology may be fully integrated for active force control. Metrology and active control of the wafer surface temperature may become important to control the polishing chemical reaction. Tools may have the capability of precision "point-of-use" slurry mixing, and a green tool design should be well established.

Advances in CMP consumables will share equal importance with tools in enabling future metal planarization. The attention focused on polishing slurries has resulted in significant improvements in their performance. Producing slurries with controlled selectivities for Cu/barrier/dielectric has allowed the user to engineer the polish sequence for minimal Cu thinning. At the same time, attention must be paid to the slurries' role in creating scratch and residual defects on the Cu wires and dielectric surfaces, and corrosion of the Cu wires. The RMS roughness of the polished Cu surface may become important, as interface scattering effects start to influence the conductivity of small wires. The advent of solids-free CMP chemistries for Cu may improve manufacturing margin through improved selectivity and dishing control, two areas that may also be addressed by fixed-abrasive pads. Development of new abrasive materials with engineered chemical-physical properties and engineered pad materials both may lead to enhanced precision in the metal polishing process. What is demonstrated by these consumable innovations is the less explored regions of CMP process space (both *chem-* and *mech-*) that may hold answers to problems of metal planarization in the future. A materials pathway to a low shear force metal polish is a potential solution. For CMP consumables it is expected that a path of continuous improvement will be taken.

Post-CMP wafer cleaning will likely become more closely integrated with the metal planarization process. With respect to tools, the combined polisher/cleaner for Cu CMP is common in manufacturing. The brush scrubber, in combination with megasonic and chemical treatments, is currently favored. The chemistries employed for cleaning are now formulated for metal applications, and in the future may need to be tailored for the specific slurry and CMP process with which they are used. Since the chemical characteristics of the cleanable defects are more and more determined by the slurry used and the polishing byproducts, closer collaboration between the slurry providers, chemical providers, and end user will be required. Metal corrosion remains a concern, as it is often tied to the specifics of the metals deposition. Development will continue on alternative cleaning technologies.

Figure 42 Planarization Potential Solutions

#### ETCH, STRIP, AND CLEAN POTENTIAL SOLUTIONS

Plasma etching of interconnect structures will be required throughout the ITRS forecast period, as shown in Figure 43. Subtractive metal etch, the standard for pattern transfer for many decades, will continue to be used for DRAM until at least 100 nm half pitch; there may also be applications in logic products with copper wiring that include aluminum at the packaging interface. RIE etch of high A/R aluminum conductors for DRAM at 90 nm and below is expected to be extremely difficult and will require continued development by tool suppliers, for those manufacturers who do migrate to Cu. High aspect ratio W contacts for Al DRAM technologies may see an additional challenge with the incorporation of low  $\kappa$  materials requiring new development in sidewall passivation chemistries. Contact/via etch for all product classes will extend to 22 nm. Damascene and dual Damascene approaches will be utilized with copper conductors.

The Reactive Ion Etching (RIE) process will continue to be applied to an increasing diversity of materials. New material introductions for BEOL ILD materials, capacitor structures (electrode and storage materials) as well as Cu capping or barrier materials. Development of needed etch capability must be timed to match the permittivity trend in the dielectric potential solutions roadmap. There is no strong drive for novel plasma source technology development but rather a focus on etch and passivation chemistry strategies required for multi component materials and integration stack configurations. Porous materials are particularly sensitive to distortion, and geometric control and aspect-ratio-dependent etching effects (ARDE) must be minimized. Etch processes must not introduce electrical, chemical, or physical damage, for the 65 nm node, new processes such as neutral stream, are a potential solution.

Many new interconnect materials are associated with the ILD, capacitors and their electrodes, barriers, hard mask and capping layers and top and bottom antireflection layers. The BEOL ILD will introduce increasing organic content coincident with the simultaneous increase in porosity to reduce dielectric constant. This hybridization of the ILD material, now containing both organic and inorganic functionality, must meet the dual challenges of minimizing the effective  $\kappa$  of the stack with the use of a reduced  $\kappa$  etch stop and capping materials as well as the selectivity needs. Cu barrier and capping layer improvements will introduce several new classes of materials which maybe be multi-component in nature, likely amorphous, and continually thinner to address lower  $\kappa_{eff}$  targets. These Cu cap layers represent the etch stop material at the bottom of the high aspect ratio dual Damascene contact that must offer continual higher selectivity to the low  $\kappa$  ILD etch chemistry to address this projected thinning.

Emerging capacitor materials and novel electrode materials will create challenging etching requirements. Multicomponent capacitor materials will require significant etch chemistry development. Coupled with the use of noble metal electrode materials, there may be a requirement for different plasma etch chemistries incorporated on the same etch platform.

These interconnect materials create new cleaning challenges associated with surface preparation and post-etch residue removal. Cleaning technology encompassing dry, semi-dry, wet and combinations will be required. Wet cleans, effective for metallic removal, will be incorporated on platforms with more dilute chemistries, and point of use generation and dispense. Semi-dry modifications of wet cleans, those that utilize aqueous ammonia and ozonated water or acids, will also move away from batch to single wafer with the same point of use needs. Dry cleaning methods are likely to be used for surface preparation or "conditioning" prior to deposition but are inefficient for removing elevated concentrations of metallic elements.

Damascene structures will force a change in photoresist stripping and subsequent cleaning. The complete move from wet to plasma or dry etching is not possible for the subsequent cleans/strips. Oxygen-based chemistries are often used for etching organic low  $\kappa$  dielectrics for trench, via and contact steps. Unfortunately, dry processes, generally used to remove organic materials, may be insufficient to remove residues and particles from structures with high aspect ratios without attacking the low  $\kappa$  dielectrics or copper barrier structures. Wet chemicals or other techniques, including the use of supercritical or dense fluids, can be effective and may be necessary. These fluids, especially when combined with surfactants or co-solvents, can be particularly effective in high A/R features for cleaning and stripping.

Alternative stripping gases, such as hydrogen-reducing chemistries, might be needed for porous silicon oxide or similar low  $\kappa$  materials. Cryogenic aerosol technologies which create ice crystals from cooled argon or nitrogen can be effective for particulate removal and are environmentally benign. High  $\kappa$  materials and capacitor electrodes which might contain barium strontium titanate or ruthenium, etc., have their own unique set of challenges. The most promising hybrid approaches will combine multiple technologies in gas phase and liquids to meet both surface preparation, cleaning and

stripping requirements. Other issues that will affect the future development of these technologies include finding new chemistries that are compatible with ESH mandates, selectivity needs, and electrical requirements.

| First Year of IC Production                                                | 2001 2      | 2003 20 | 005 20<br>2006 | 07 20<br>2008 | 009 20<br>2010 | 011 20<br>2012 | 13 20<br>2014 | 15 20<br>2016 | )17  |

|----------------------------------------------------------------------------|-------------|---------|----------------|---------------|----------------|----------------|---------------|---------------|------|

| ЕТСН                                                                       |             | 2004    | 2000           | 2000          | 20,10          | 2012           | 2014          | 2010          |      |

| Metal Etch                                                                 |             |         |                |               |                |                |               |               |      |

| New electrode materials for high $\kappa$ applications ( $\kappa$ >100)    |             |         | ]              |               |                |                |               |               |      |

| Dielectric etch of contact, via, and trench                                |             |         |                |               |                |                |               |               |      |

| High κ materials (κ>100)                                                   |             |         |                |               |                |                |               |               |      |

| Moderate $\kappa$ materials (10< $\kappa$ <60)                             |             |         |                |               |                |                |               |               |      |

| Standard κ (SiO <sub>2</sub> , Si <sub>3</sub> N <sub>4</sub> ) (4.5<κ<10) |             |         |                |               |                |                |               |               |      |

| Standard κ (SiC) (4.5<κ<10)                                                |             |         |                |               |                |                |               |               |      |

| Low $\kappa$ materials (minimum $\kappa$ <2.7)                             |             |         |                |               |                |                |               |               |      |

| Ultra low κ materials (2.0<κ<2.5)                                          |             |         |                |               |                |                |               |               |      |

| Extreme low $\kappa$ materials (1.5< $\kappa$ <1.9)                        |             |         |                |               |                |                |               |               |      |

| Ferroelectrics                                                             |             |         |                |               |                |                |               |               |      |

| PZT, SBT                                                                   |             |         |                |               |                |                |               |               |      |

| STRIP AND CLEAN                                                            |             |         |                |               |                |                |               |               |      |

| Post metal (Al) etch cleans                                                |             |         |                |               |                |                |               |               |      |

| Integrated wet and dry solutions                                           |             |         |                |               |                |                |               |               |      |

| Dense fluid CO <sub>2</sub> with co-polymer/additives                      |             |         |                |               |                |                |               |               |      |

| Ozone combined gas/liquid approaches                                       |             |         |                |               |                |                |               |               |      |

| Research Required Developme                                                | nt Underway | ,       | Qualific       | ation/Pre-l   | Production     |                | 🖉 Continu     |               | veme |

Figure 43 Etch, Strip, and Clean Potential Solutions

## RELIABILITY

The semiconductor industry move to copper metallization promises significant improvements in interconnect currentcarrying capacity and high-temperature operation, but presents numerous new material integration and reliability challenges. Since copper readily diffuses into silicon and most dielectrics, it must be encapsulated with metallic (such as Ta, TaN) or dielectric (such as SiN, SiC) diffusion barriers to prevent electrical leakage between metal wires and degradation of transistor performance. Cu diffusion is also greatly enhanced by electric fields imposed between adjacent wires during device operation, and absolute barrier integrity is crucial to long term device reliability. As barrier thickness scales with metal width to meet effective resistivity goals, copper containment becomes increasingly more problematic, and eventually new copper passivation techniques and/or diffusion-resistant dielectrics are needed to provide "zero thickness" solutions.

Copper, unlike aluminum, has no self-passivation layer. Therefore, surface diffusion is expected to dominate electromigration behavior, and material interfaces will play a key role in determining overall reliability. Maintaining the mechanical and electrical integrity of dielectric and metal barriers, particularly at their critical corner juncture, will also be essential to prevent catastrophic copper diffusion between metal leads. CVD copper barriers and seed layers, while providing scaling relief, bring additional integration concerns, and the impact of texture and intermixed CVD/ECD copper layers must be understood.

Damascene structures may change the approach to photoresist stripping and subsequent cleaning for interconnect layers. The use of hard mask materials and oxygen-based chemistries for etching organic low  $\kappa$  dielectrics enables *in situ* stripping of the photoresist during the trench, contact or via etch steps. Dry stripping alone may be insufficient to remove residues and particles from structures with high aspect ratios without attacking the low  $\kappa$  dielectrics or copper and its barriers. The implementation of porous silicon oxide or similar low  $\kappa$  materials may allow the continued use of traditional oxygen-based stripping processes, but the detailed reliability implications of this combination of processes and materials will need to be understood. All of these unit processes bring their own specific yield loss mechanisms as well as susceptibility to longer term reliability problems.

The integration of new low  $\kappa$  dielectrics needed for performance enhancement bring numerous reliability concerns that include thermally or mechanically-induced cracking or adhesion loss, poor mechanical strength, moisture absorption, time-dependent behavior, texture effects, and poor thermal conductivity. The typical thermal conductivity of low  $\kappa$  dielectrics is less than one third that of oxide, leading to higher metal wire temperatures and enhanced electromigration. Bi-layer or embedded oxide/low  $\kappa$  dielectric schemes may be required to enhance the mechanical strength and heat dissipation of future low  $\kappa$  dielectric systems.

The lessened mechanical strength of low  $\kappa$  dielectrics and anticipated higher temperature operation of some of the copper interconnects will drive the need for novel packaging techniques and structures. These, combined with the move to higher packaging process temperatures and migration to Pb-free solders, will provide new reliability challenges for the research and development community to resolve. Expanding use of advanced technology in assembly, such as area-array bumps, need to be considered and integrated with circuit, material, and process selections in order to maintain product reliability in the future. This is especially important to encompass low  $\kappa$  dielectrics and assembly-related process steps, so that steps such as under-bump fill, integrate with low  $\kappa$ .

Computer-aided design (CAD) tools will need to incorporate contextual reliability considerations in the design of new products and technologies. It is essential that advances in failure mechanism understanding and modeling, which result from the use of improved test methodologies, be used to provide input data for these new CAD tools. With these data and smart reliability CAD tools, the impact on product reliability of design selections can be evaluated. New CAD tools need to be developed that can calculate degradation in electrical performance of the circuit over time. The inputs used would be the predicted resistance increases in interconnect wires and vias in the circuit based on the following:

- Wire length

- Current densities expected for the currents required by the circuit

- Calculated local operating temperature, which includes the effects of Joule heating in the circuit and elsewhere

These tools will need to become an integral part of the circuit designer's tool set to aid in the prediction of product reliability before processing begins and to develop solutions that anticipate technology and thereby accelerate their introduction.

Continuing research is needed to fully understand the multi-variable nature of copper and low  $\kappa$  interconnect reliability and provide accurate models for designed-in reliability. The fundamental limits of copper metallization must also be explored to assess technology extendibility, especially to feature sizes where electron surface scattering effects become a significant contributor to resistivity (< 45 nm for Cu).

It is expected that one or more alternate interconnect approaches, such as optical interconnects, package intermediated interconnects, 3D interconnects, or microwave interconnects will begin to be used within the next five years. Although it is too early to know the full integration scheme for these approaches, and also too early for complete reliability investigations, it is critical for the research community to use reliability requirements as one of the key considerations in alternate interconnect process and design selection.

## SYSTEMS AND PERFORMANCE ISSUES

#### INTERCONNECT PERFORMANCE

The adequacy of near-term interconnect technologies (copper wires and low  $\kappa$  dielectrics) to continue meeting the performance requirements for ICs fabricated for succeeding technology nodes varies with the intended function of the interconnect net and the technology used to fabricate the Cu wires. For a constant span of gates (such as 40 gates), the signal delay time for local wires is typically a small fraction of a clock cycle, and is expected to decrease at a rate similar to the reduction of the gate propagation delay as a function of technology scaling. This trend is expected to continue down to the 65 nm or 45 nm nodes, at which point the signal delay for local wires will begin to increase. The delay for intermediate wires in terms of half the perimeter of a functional block will grow only slightly with technology scaling. Conversely, crosstalk and noise for local wires (and some intermediate wires) are expected to increase with decreasing wire pitch. These trends are a strong function of design strategy, and should be considered in that context.

It has been shown by several researchers that the global interconnect performance needed for future generations of ICs cannot be achieved even with the most optimistic values of metal resistivity and dielectric constant. The signal delay time for global wires will continue to increase with technology scaling primarily due to the increasing resistance of the wires and their increasing lengths (delay for a non-repeated wire increases with the square of wire length). Power distribution at constant voltage through equipotential wires to all  $V_{dd}$  bias points requires increasingly lower resistance global wires to avoid the voltage drop problem. The increasing power supply current, related to the decreasing  $V_{dd}$ , causes an increased voltage drop between power supply and the bias point for fixed global wire resistance. Consequently, this requirement demands increasingly lower resistance paths from the power supply to the  $V_{dd}$  bias points. This need is being partially addressed by the introduction of ball-grid-array packaging technology that distributes power feeds across the area of the chip, eliminating much of the on-chip lateral power feeds through relatively high-resistance global wires. Interconnect nets for distributing clock signals and power can dissipate up to 40-50 % of the power on the chip, which may exceed 120 Watts.

#### SYSTEM LEVEL INTEGRATION

System level integration encompasses the physical and functional assembly of a system's macro functions to achieve its desired operating characteristics. Assembly of individual functional components (such as bare chip or block functions on a single chip) into the system must encompass all the performance and reliability requirements imposed on the system. For interconnect, the requirements are currently met through the distinctly separate functions of on-chip interconnect, packaging and board-level technologies. It is now widely conceded that technology alone (in the short term, and probably not in the long term) cannot solve the on-chip global interconnect problem with current design methodologies. Rather, the current view is that design, process technology, packaging, and board construction will all need to come together to provide an optimized integrated system level solution for interconnect requirements.

The current projection for evolution of interconnect is that in the short term interconnect delay problems in new ICs will be met by circuit design within the constraints of planar technology with special attention to minimizing the lengths of critical paths. This will be done in concert with a substantial push in Cu-low  $\kappa$  technology, as well as more innovative

packaging and board approaches, to minimize the changes needed in design architectures while still meeting the continued advances in performance projected by the ITRS. In the intermediate term, Cu-low  $\kappa$  will be pushed to its limits, and new design architectures as well as chip-package co-design will be achieved with new CAD tools to significantly facilitate needed performance advances. Beyond these extrapolations of current practices, radically new design, packaging, and technology options will be needed.