# INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS

2011 EDITION

# **ASSEMBLY AND PACKAGING**

THE ITRS IS DEVISED AND INTENDED FOR TECHNOLOGY ASSESSMENT ONLY AND IS WITHOUT REGARD TO ANY COMMERCIAL CONSIDERATIONS PERTAINING TO INDIVIDUAL PRODUCTS OR EQUIPMENT.

### **TABLE OF CONTENTS**

| 1. | Scope                                                      | 1  |

|----|------------------------------------------------------------|----|

| 2. | Difficult Challenges                                       | 1  |

| 3. | Single Chip Packaging                                      |    |

| (  | Overall Requirements                                       | 4  |

| ı  | Electrical Requirements                                    | 5  |

|    | Cross Talk                                                 |    |

|    | Power Integrity                                            |    |

|    | Thermal Requirements                                       |    |

| _  | Hot Spots                                                  |    |

|    | Mechanical Requirements                                    |    |

|    | Mechanical Modeling and Simulation                         |    |

|    | Cost                                                       |    |

|    | Reliability                                                |    |

| (  | Chip to Package Substrate                                  | 10 |

| I  | Interconnect Technologies for Single Chip Package          |    |

|    | Wire Bonding                                               |    |

|    | Flip Chip                                                  |    |

| _  | Molding                                                    |    |

| I  | Package Substrate to Board InterconnectLead Frames         |    |

|    | High Density Connections                                   |    |

|    | Package Substrates                                         |    |

|    | For Low-Cost Applications—Laminate for PBGA                |    |

|    | Hand-Held Applications—Fine Laminate for FBGA              |    |

|    | Mobile Applications—Build-Up Substrate for SiP             |    |

|    | Cost Performance Applications—Build-Up Substrate for FCBGA |    |

|    | High Performance—Low κ Dielectric Substrate for FCBGA      | 17 |

| 4. | Wafer Level Packaging                                      | 18 |

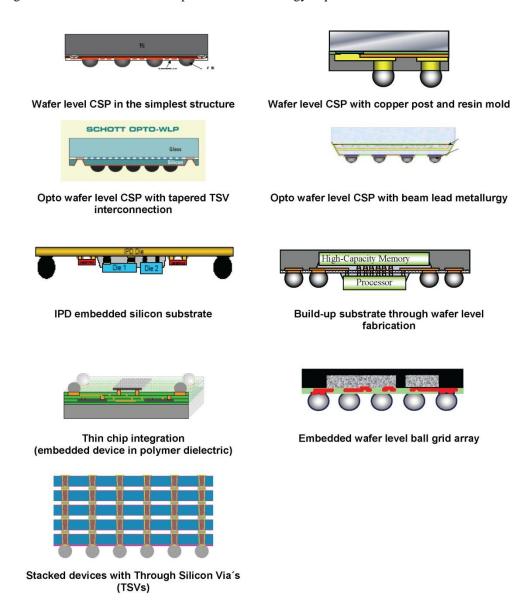

| 5. | Wafer Level Package Developments and Trends                | 20 |

| I  | Future Trends for Wafer Level Packaging                    | 21 |

| ĺ  | Difficult Challenges for WLP                               | 21 |

| I  | Examples for Emerging Wafer Level Package Technologies     | 22 |

|    | Wafer Level Through Silicon Via (TSV) for 3D Integration   |    |

|    | Fan Out WLP Using Reconfigured Wafer Level Technologies    |    |

| 3. | System Level Integration in Package                        | 23 |

| I  | Definition of SiP                                          | 24 |

| ,  | SiP versus SoC                                             | 25 |

| ,  | SiP-Level System Design versus Board-Level System Design   | 25 |

| I  | Difficult Challenges for SiP                               | 26 |

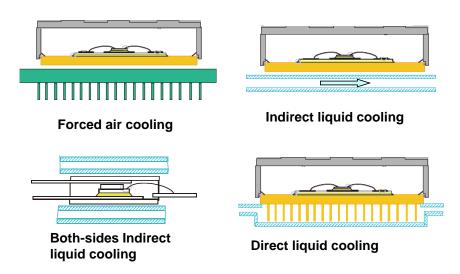

|    | Thermal Management                                         | 26 |

|    | Thermal Challenge of Hot Spots in SiP                      |    |

|    | Cooling Solution Design Requirements for SiP               |    |

|    | Thermal Challenges of Processor and Memory Die SiP         |    |

|    | Thermal Management of 3D Technology with TSV Interconnect  | 28 |

| Power Delivery/Power Integrity                      | 29                         |

|-----------------------------------------------------|----------------------------|

| Testing of SiP                                      | 29                         |

|                                                     |                            |

|                                                     |                            |

| Mechanical and Thermal Testing                      | 30                         |

|                                                     |                            |

| · · · · · · · · · · · · · · · · · · ·               |                            |

| Diversification and Management of Complexity        | 32                         |

| The Need for Coherent Chip-Package-System Codesign  |                            |

|                                                     |                            |

| ·                                                   |                            |

| , , ,                                               |                            |

| ·                                                   |                            |

|                                                     |                            |

|                                                     |                            |

| 3D Integration                                      | 36                         |

| Scope                                               | 36                         |

| Difficult Challenges                                | 37                         |

| Technology Requirements                             | 38                         |

| Interposers                                         | 38                         |

|                                                     |                            |

| 3D Issues                                           | 39                         |

| 3D Integration Definition of Terms                  | 40                         |

| Processes for 3D-TSV Integration                    | 41                         |

| Wafer/Device Stacking                               | 41                         |

| TSV Interconnect Methods                            | 42                         |

| Emerging Inter-Die Interconnect                     | 42                         |

|                                                     |                            |

| ,                                                   |                            |

| • •                                                 |                            |

| •                                                   |                            |

| <u> </u>                                            |                            |

| 3 3 1                                               |                            |

|                                                     |                            |

|                                                     |                            |

| ·                                                   |                            |

|                                                     |                            |

|                                                     |                            |

|                                                     |                            |

| · · ·                                               |                            |

| · · · · · · · · · · · · · · · · · · ·               |                            |

|                                                     |                            |

| · · · · · · · · · · · · · · · · · · ·               |                            |

| Summary of Optical Data Transmission Needs          | 58                         |

| Packaging for MEMS                                  | 58                         |

| Semiconductor Packaging for Automotive Applications |                            |

|                                                     | Testing of SiP Test Access |

|     | Automotive Electronics                                       | 60 |

|-----|--------------------------------------------------------------|----|

|     | Global Warming                                               | 60 |

|     | Packaging Technology Development                             | 63 |

|     | Medical and Bio Chip Packaging                               | 65 |

| S   | olar Cell Packaging                                          | 66 |

| 9.  | Advanced Packaging Processes                                 | 67 |

| S   | cope                                                         | 67 |

| Εı  | mbedded and Integrated Active and Passive Devices            | 67 |

|     | Applications for Embedded Active and Passive Devices         |    |

| W   | afer Thinning and Singulation                                |    |

|     | Wafer Thinning                                               | 69 |

|     | Wafer Singulation                                            | 69 |

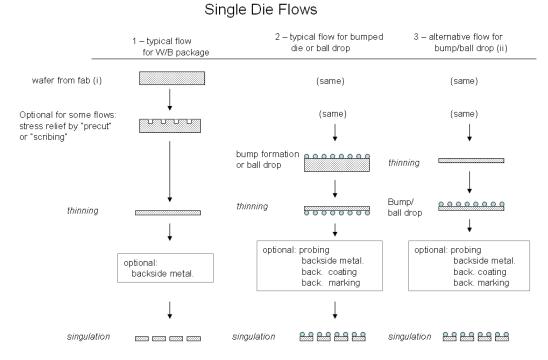

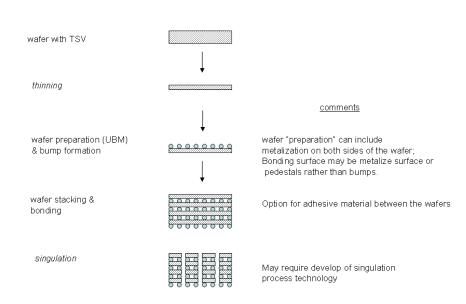

|     | Process Flows Associated with Wafer Thinning and Singulation | 70 |

| 10. | Packaging Materials Requirements                             | 72 |

| S   | cope                                                         | 72 |

| 11. | Environmental Issues                                         | 73 |

| 12. | Packaging Gaps and Technology Needs                          | 74 |

| 13. | Industry Consortia                                           | 74 |

| 14. | References                                                   | 74 |

# **List of Figures**

| Figure AP1:  | Hardware Components of Cloud Computing                                                                                                                                             | 4  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure AP2:  | The Use of Compliant/Flexible I/O Can Potentially Eliminate the Need for Underfill                                                                                                 | 9  |

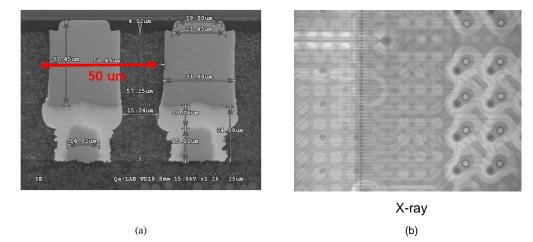

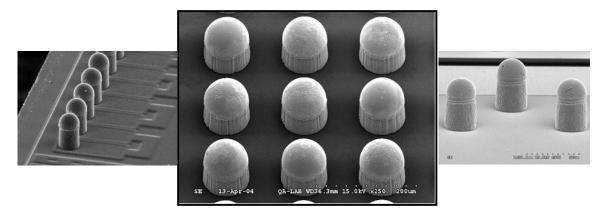

| Figure AP3:  | Micro Bump and Pillar Bump Structures for High Reliable Chip-to-Substrate Interconnects                                                                                            | 1( |

| Figure AP4:  | Wirebond and Flip Chip Pitch versus Technology Nodes                                                                                                                               | 11 |

| Figure AP5:  | Example of 15 µm Cu Wire Bond with Die Stacking                                                                                                                                    | 12 |

| Figure AP6:  | Example of Multi-Tier Cu Wire Bonding with 847 Lead PBGA                                                                                                                           | 12 |

| Figure AP7:  | Bonding Overhang Die                                                                                                                                                               | 13 |

| Figure AP8:  | Wire Bond on Both Sides of Lead Frame Substrate                                                                                                                                    | 13 |

| Figure AP9:  | Examples of Copper Pillar Bumps (a) and Assembled Copper Pillar (b) X-Ray                                                                                                          | 14 |

| Figure AP10: | Example of Copper Pillars with Solder Tips Single Line 50 µm Pitch (staggered (100 µm)                                                                                             | 14 |

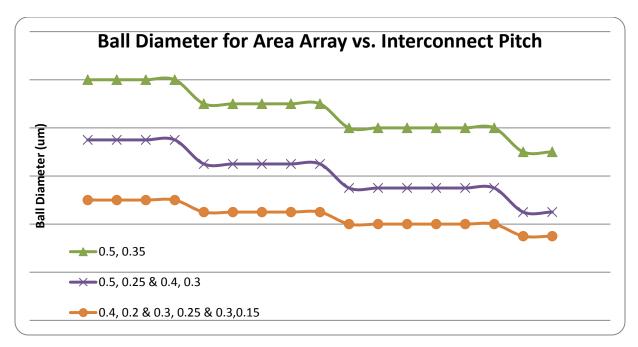

| Figure AP11: | Ball Diameter versus Pitch for Area Array Interconnect                                                                                                                             | 18 |

| Figure AP12: | Examples of Wafer Level Packaging Types                                                                                                                                            | 19 |

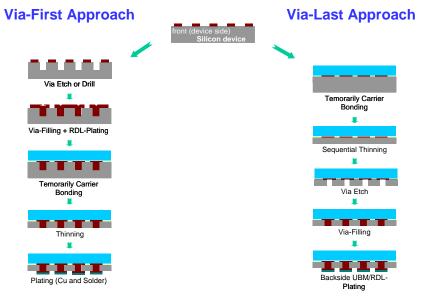

| Figure AP13: | Basic Process Flow Via-first versus Via Last                                                                                                                                       | 22 |

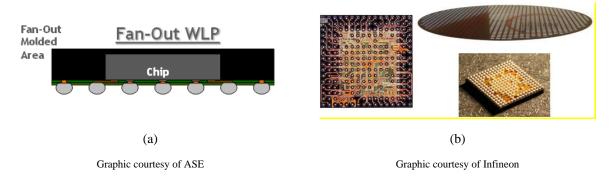

| Figure AP14: | Example of a Side-by-Side Solution of a Fan-Out WLP                                                                                                                                | 23 |

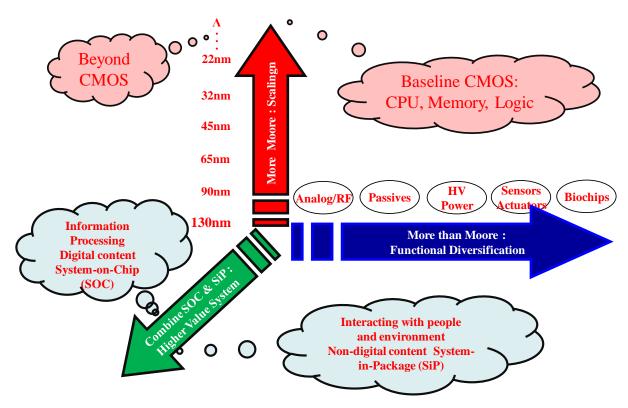

| Figure AP15: | Higher Value Added System by Combining More Moore and More than Moore                                                                                                              | 24 |

| Figure AP16: | Categories of SiP                                                                                                                                                                  | 25 |

| Figure AP17: | SiP Design Improves Footprint, Reduces PCB Layers Reduction and Improves Performance                                                                                               | 26 |

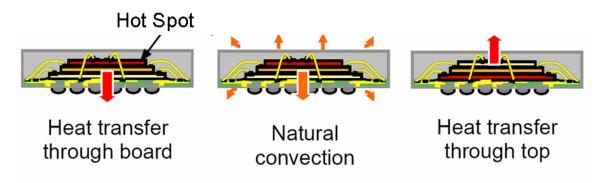

| Figure AP18: | Location of High Power Die versus Primary Heat Flow Path                                                                                                                           | 27 |

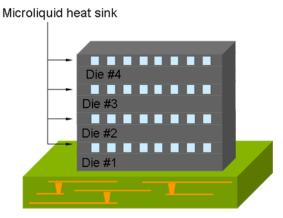

| Figure AP19: | Interposer Based Microliquid Heat Sink for Stacked Die                                                                                                                             | 29 |

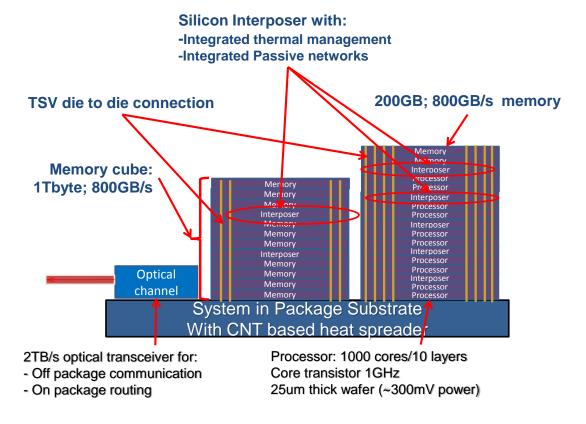

| Figure AP20: | Current Vision for Packaging of 3D-SiP                                                                                                                                             | 31 |

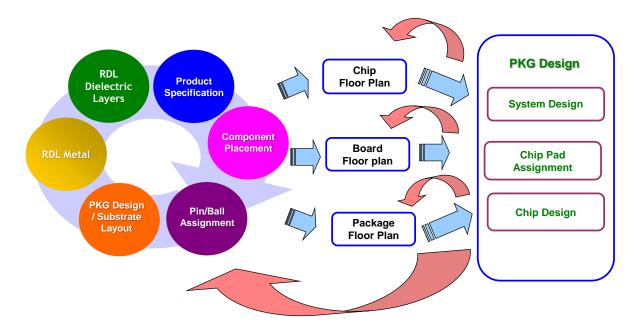

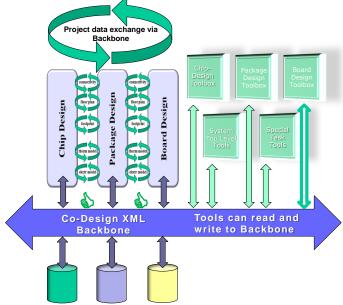

| Figure AP21: | Chip-Package-System Co-Design Flow                                                                                                                                                 | 33 |

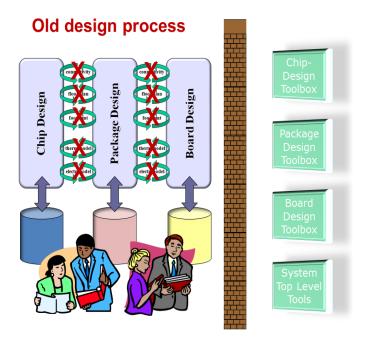

| Figure AP22: | Past and Future Design Process for 3D SiP                                                                                                                                          | 34 |

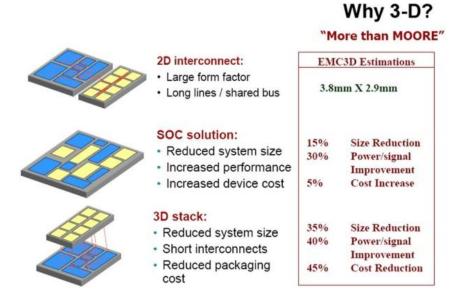

| Figure AP23: | Driving Forces for 3D Integration                                                                                                                                                  | 37 |

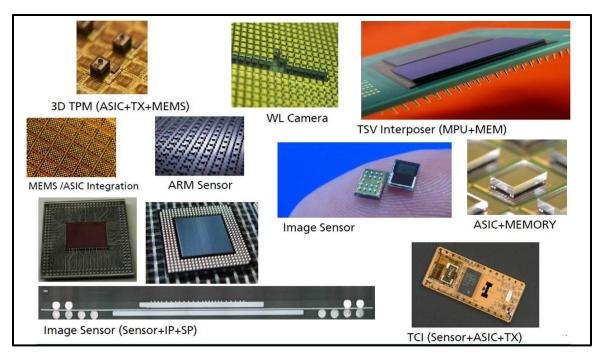

| Figure AP24: | Examples of 3D SiP Integration                                                                                                                                                     | 38 |

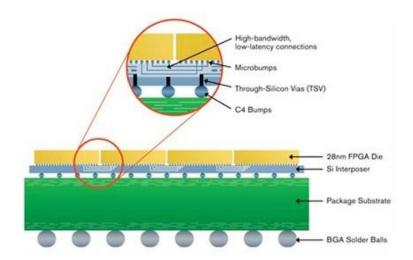

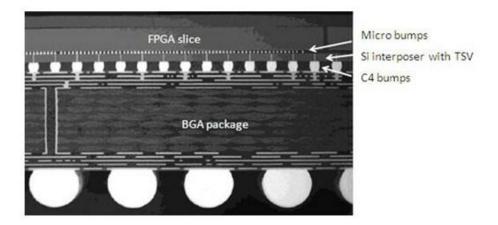

| Figure AP25: | 2.5D Interposer for Xilinx FPGA                                                                                                                                                    | 39 |

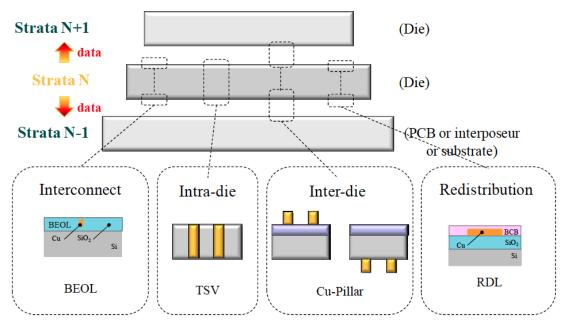

| Figure AP26: | A Schematic of 3D Integration                                                                                                                                                      | 40 |

| Figure AP27: | Example of Process Flow and Equipment for 3D Integration                                                                                                                           | 41 |

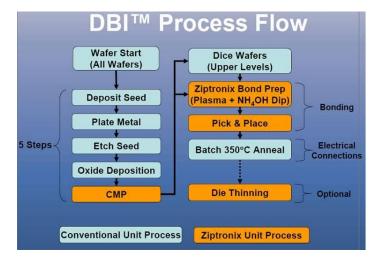

| Figure AP28: | Direct Bond Interconnect Process Flow                                                                                                                                              | 42 |

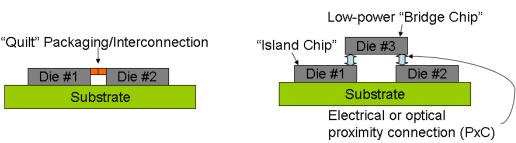

| Figure AP29: | Methods of System Interconnect for 3D Integration                                                                                                                                  | 43 |

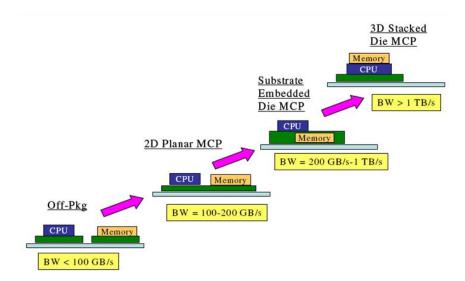

| Figure AP30: | Roadmap for Package Transitions Addressing the Memory Bandwidth Challenge                                                                                                          | 44 |

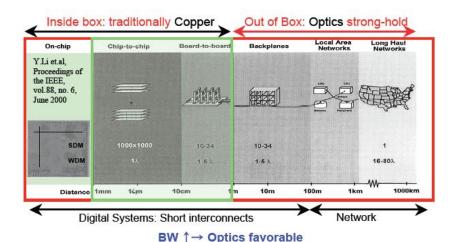

| Figure AP31: | Electronic vs. Optical Data Transmission                                                                                                                                           | 46 |

| Figure AP32: | Overview of the Role of Optical Data Transmission vs. Electrical Methods Illustrating Optical Methods Moving Down to the Meter Distance as Data Rates Increase into the Gb/s Range | 46 |

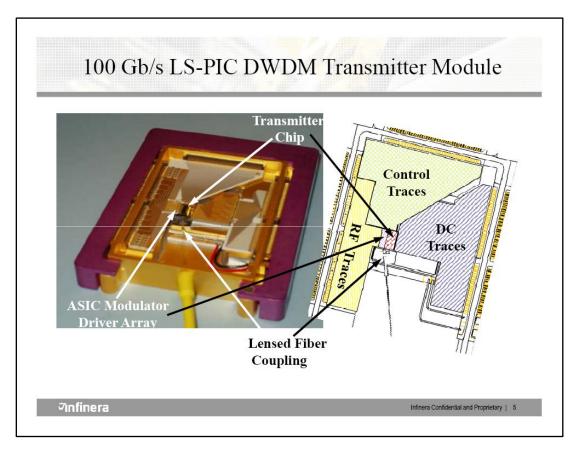

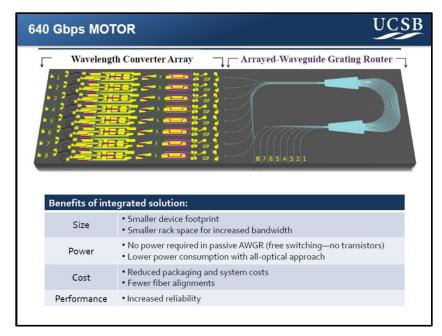

| Figure AP33: | A telecommunications Transmitter Module from Infinera                                                                                                                              | 47 |

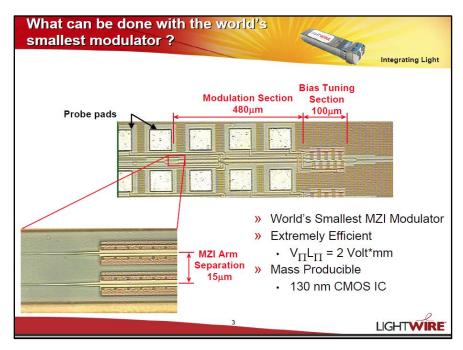

| Figure AP34: | Even the World's Smallest Modulator is Large vs. Transistors                                                                                                                       | 48 |

| Figure AP35: | A Planar Lightwave Circuit, a Passive Device that Requires No Power                                                                                                                | 49 |

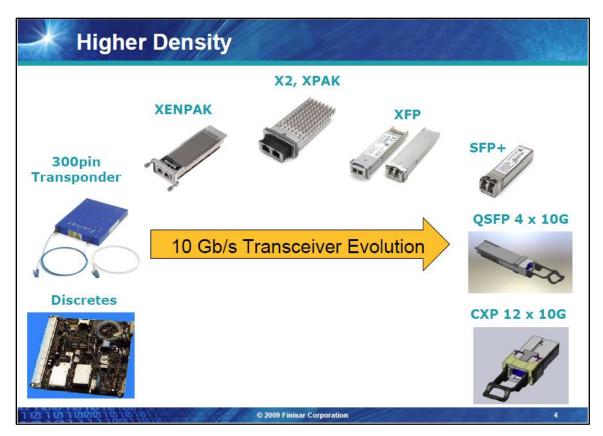

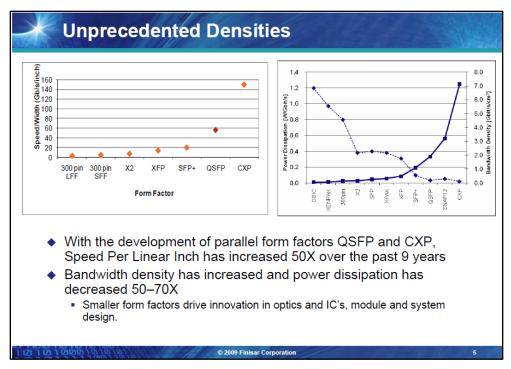

| Figure AP36: | The Evolution of Optical Transceivers Over the Last 30 Years                                                                                                                       | 50 |

| Figure AP37: | The Evolution of Rack Density on the Left in Gb/s/inch and Power in Watts/Gb/s or the Right as the Transceiver Form Factor Changed                                                 | 5′ |

| Figure AP38: | A Luxtera Active Optical                                                                                                                                                           | 51 |

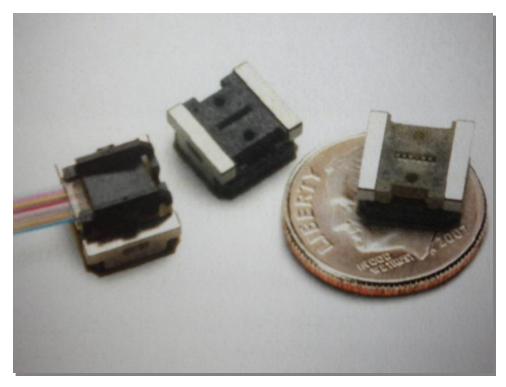

| Figure AP39: | The Micropod Optical Cable System                                                                                                                                                  | 52 |

| Figure AP40: | The Avago MicroPOD                                                                                                                                                                 | 53 |

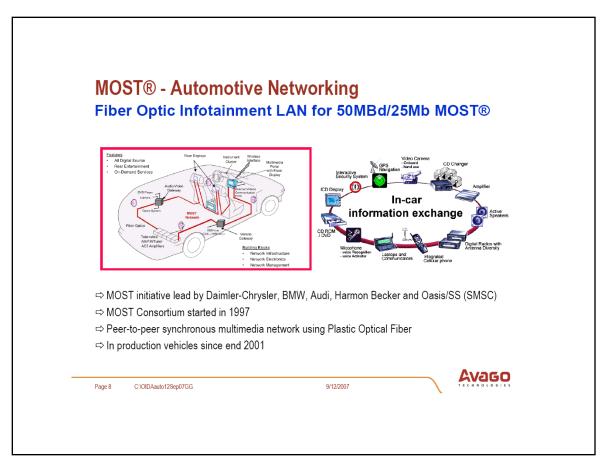

| Figure AP41: | The Use of Plastic Optical Fiber (POF) in Automotive Applications                                                 |    |

|--------------|-------------------------------------------------------------------------------------------------------------------|----|

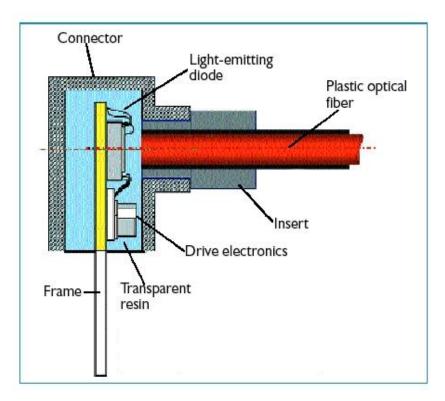

| Figure AP42: | Connector, Light Source, and Plastic Optical Fiber are Easily Interfaced                                          | 55 |

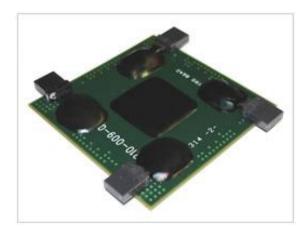

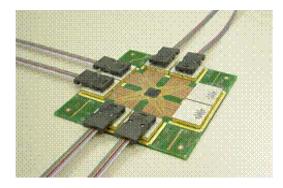

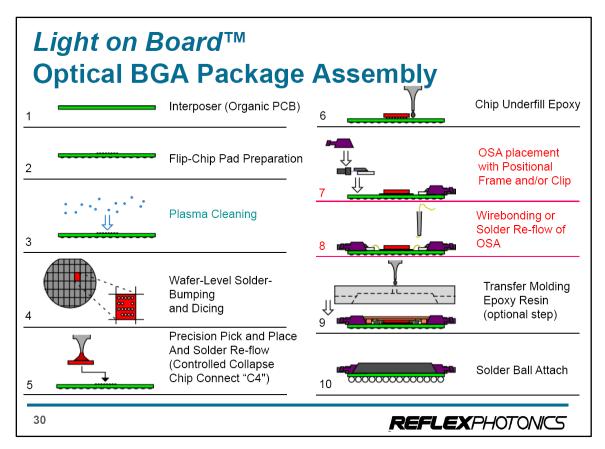

| Figure AP43: | Gb/s Data Rates On-to and Off-of Chip Using Optically Connectorized Chip Packaging per Reflex Photonics           | 56 |

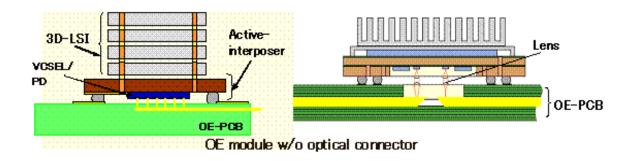

| Figure AP44: | An Optical Wiring Board Based on the Work of Mr. Takahara of NTT                                                  | 56 |

| Figure AP45: | Manufacturing Process for an Optical Product                                                                      | 57 |

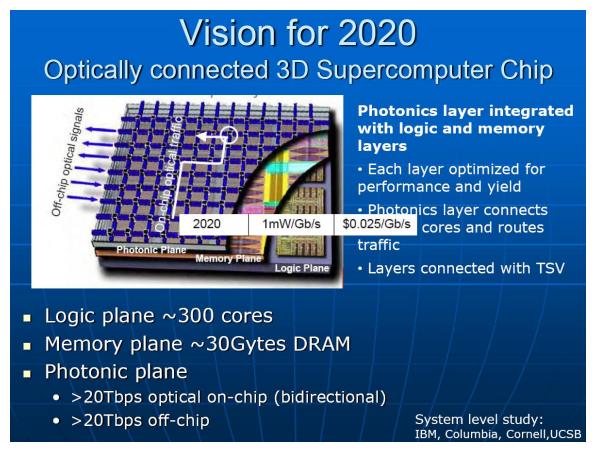

| Figure AP46: | A Vision of 2020 Projected Needs with On-Chip Optical Data Transmission Using TSVs and Specialized Chip Layers    | 58 |

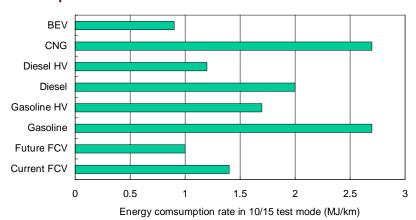

| Figure AP47: | Automotive Energy Consumption                                                                                     | 61 |

| Figure AP48: | Alternative Energy Vehicle Characteristics                                                                        | 62 |

| Figure AP49: | Roadmap of Automotive Electronics                                                                                 | 63 |

| Figure AP50: | Requirements to Packages for Vehicles                                                                             | 63 |

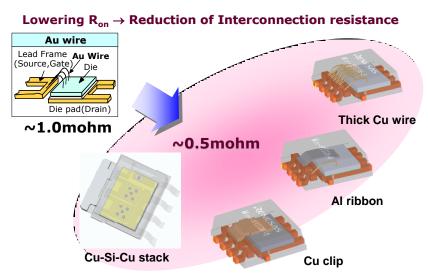

| Figure AP51: | Thermal Management for the Inverter Electronics                                                                   | 64 |

| Figure AP52: | Techniques for Reducing Interconnect Resistance in Automotive Electronics                                         | 65 |

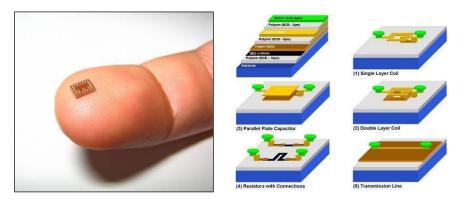

| Figure AP53: | CSP with Integrated Passive Devices and Thin-film Build-Up Passive Elements                                       | 67 |

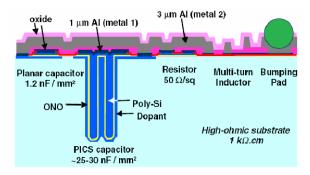

| FIGURE AP54: | PICS Substrate with High Density "Trench" MOS Capacitors, Planar MIM, Multi-Turn Inductors, and Poly-Si Resistors | 68 |

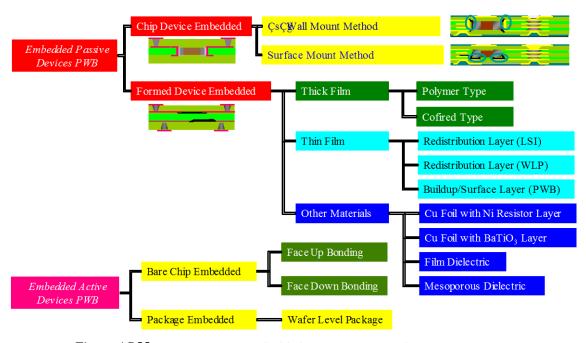

| Figure AP55: | Overview of Embedded Active Devices and Passive Devices                                                           | 68 |

| Figure AP56: | Extract of Thinning and Singulation Process Flow for Single Die Package                                           | 70 |

| Figure AP57: | Extract of Thinning and Singulation Process Flow for Packages Using Die on Wafer Process                          | 71 |

| Figure AP58: | Extract of Thinning and Singulation Process Flow for Packages Using Bonded Wafers                                 | 72 |

| Figure AP59: | Current Environmental Regulations                                                                                 | 74 |

|              |                                                                                                                   |    |

## **List of Tables**

| Table AP1:  | Assembly and Packaging Difficult Challenges                     | 2  |

|-------------|-----------------------------------------------------------------|----|

| Table AP2:  | Single-chip Package Technology Requirements                     | 5  |

| Table AP3:  | Chip-to-package Substrate Technology Requirement                | 8  |

| Table AP4:  | Package Warpage at Peak Processing Temperature                  | 8  |

| Table AP5:  | Substrate to Board Pitch                                        | 8  |

| Table AP6:  | Package Failure Modes                                           | 8  |

| Table AP7:  | Package Substrates:Low Cost (PBGA)                              | 16 |

| Table AP8:  | Package Substrates: Hand-held (FBGA)                            | 16 |

| Table AP9:  | Package Substrates: Mobile Products (SiP, PoP)                  | 16 |

| Table AP10: | Package Substrates: Cost performance (CPU, GPU, Game Processor) | 16 |

| Table AP11: | Package Substrates: High Performance (High End)                 | 17 |

| Table AP12: | Package Substrates: High Performance (LTCC)                     | 17 |

| Table AP13: | Wafer Level Packaging                                           | 19 |

| Table AP14: | Key Technical Parameters for Stacking Architectures             | 22 |

| Table AP15: | System in Package Requirements                                  | 23 |

| Table AP16: | Comparison of SoC and SiP Architecture                          | 25 |

| Table AP17: | Difficult Challenges for SiP                                    | 26 |

| Table AP18: | Key Technical Parameters for Interposers                        | 37 |

| Table AP19: | Materials Challenges                                            | 37 |

| Table AP20: | Difficult Challenges and Potential Solutions for 3D Integration | 38 |

| Table AP21: | TSV Interconnect Methods                                        | 42 |

| Table AP22: | Difficult Challenges for Optical Packaging                      | 46 |

| Table AP23: | Technology Requirements for Optical Packaging                   | 47 |

| Table AP24: | Potential Solutions for Optical Packaging                       | 47 |

| Table AP25: | Key Parameters for Automotive Electronics                       | 64 |

| Table AP26: | Multiple-Sun Photovoltaic Cell Packaging Issues                 | 66 |

| Table AP27: | Thinned Silicon Wafer Thickness                                 | 69 |

| Table AP28: | Challenges and Potential Solutions in Thinning Si Wafers        | 69 |

| Table AP29: | Packaging/Gaps/Technology Needs Summary                         | 74 |

| Table AP30: | Consortia and Research Institutes in Packaging Technology       | 74 |

# **ASSEMBLY AND PACKAGING**

#### 1. SCOPE

This chapter addresses the near term assembly and packaging roadmap requirements and introduces many new requirements and potential solutions to meet market needs in the longer term. Assembly and Packaging is the final manufacturing process transforming semiconductor devices into functional products for the end user. Packaging provides electrical connections for signal transmission, power input, and voltage control. It also provides for thermal dissipation and the physical protection required for reliability.

Today assembly and packaging is a limiting factor in both cost and performance for electronic systems. This is stimulating an acceleration of innovation. Design concepts, packaging architectures, materials, manufacturing processes and systems integration technologies are all changing rapidly. This accelerated pace of innovation has resulted in development of several new technologies and both expansion and acceleration of others introduced in prior years. Wireless and mixed signal devices, bio-chips, optoelectronics, and MEMS are placing new requirements on packaging and assembly as these diverse components are introduced as elements for System-in-Package (SiP) architectures.

The electronics industry is nearing the limits of traditional CMOS scaling. The continued growth of the industry, driven by a continuous reduction in cost per function, will require new devices types, new package architectures and new materials. There will be a gap between the time CMOS scaling can no longer maintain progress at the Moore's Law rate and the time a new generation of device architectures and electronic material will support a continued drop in cost per function. As traditional Moore's law scaling becomes more difficult, innovation in assembly and packaging enabling functional diversification and allowing scaling in the third dimension must take up the slack.

Assembly and Packaging provides a mechanism for cost effective incorporation of functional diversification through System-in-Package technology. This technology enables the continued increase in functional density and decrease in cost per function required to maintain the progress in cost and performance for electronics. This will provide the principle mechanism for delivering cost effective functional diversification and thereby, equivalent scaling, to maintain the pace of progress.

New architectures including printed electronic circuits, thinned wafers and both active and passive embedded devices are emerging as solutions to market requirements. The materials and equipment used in assembly and packaging are also changing rapidly to meet the requirements of these new architectures and the changing environmental regulatory requirements.

This chapter is organized in eight major sections:

Difficult Challenges Single Chip Packaging Wafer Level Packaging System Level Integration in Package (SiP) 3D Integration Packaging for Specialized Functions **Advanced Packaging Elements Environmental Issues**

Wherever possible we have aligned the ITRS Assembly and Packaging chapter with other industry roadmap organizations including iNEMI, JISSO and IPC.

#### 2. DIFFICULT CHALLENGES

There are a few key limitations faced by the Semiconductor industry in the near term that will involve most, if not all, of the Technical Working Groups (TWGs) that must be overcome. These are:

Manage the power and thermal dissipation requirements by reduction of power requirements and improving the heat dissipation capability of the packages.

- Increasing the physical density of bandwidth in order to make use of the enormous gains in the physical density of processor power.

- Support the growing functional diversity requirements driven by More than Moore technologies.

- Support the reliability, power integrity and thermal management challenges of 3D integration.

- Drive down cost in assembly and packaging to reduce the impact of packaging cost not scaling to match device

cost.

- Reduce time to market and by co-design and simulation that includes electrical, thermal, mechanical and in some cases chemical requirements from the device, package and system.

The difficult challenges identified for the Packaging and Assembly Roadmap are presented in Table AP1. The challenges arising from the list above provide more specific granularity for these issues. Difficult challenges for geometries greater than 16 nm are presented in the table below. There has been a rapid pace of change in materials, processes and architectures to meet these challenges in the last few years and this progress continues. To maintain the rate of progress the difficult challenges in the table below must be overcome.

| Table AP                                                        | 1: Assembly and Packaging Difficult Challenges                                                                                                            |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Difficult Challenges ≥16 nm                                     | Summary of Issues                                                                                                                                         |

|                                                                 | Direct wire bond and bump to Cu for very fine pitch due to thin wire limits)                                                                              |

|                                                                 | - Dicing for ultra low k dielectric (Includes k<2.5eff and air gaps)                                                                                      |

|                                                                 | - Improved fracture toughness of dielectrics                                                                                                              |

| Impact of BEOL including Cu/low                                 | - Interfacial adhesion                                                                                                                                    |

| κ on packaging                                                  | <ul> <li>Mechanical reliability for chip-package interconnect (requires co-design due to chip-package interaction)</li> </ul>                             |

|                                                                 | - Methodologies for measurement of critical properties needed.                                                                                            |

|                                                                 | – Probe damage for copper/ultra low κ                                                                                                                     |

|                                                                 | - I/O pitch for small die with high pin count                                                                                                             |

| W-f11i                                                          | Solder joint reliability for tight pitch-low stand-off interconnect                                                                                       |

| Wafer level packaging                                           | - Compact ESD structures                                                                                                                                  |

|                                                                 | - CTE mismatch compensation for large die and fanout die                                                                                                  |

|                                                                 | Mix signal co-design and simulation environment                                                                                                           |

|                                                                 | - Rapid turn around modeling and simulation                                                                                                               |

| Coordinated design tools and                                    | <ul> <li>Integrated analysis tools for transient thermal analysis and integrated thermal mechanical<br/>analysis</li> </ul>                               |

| simulators to address chip, package,<br>and substrate co-design | <ul> <li>Electrical (power disturbs, EMI, signal and power integrity associated with higher<br/>frequency/current and lower voltage switching)</li> </ul> |

| -                                                               | - System level co-design is needed now.                                                                                                                   |

|                                                                 | - EDA for "native" area array is required to meet the Roadmap projections.                                                                                |

|                                                                 | - Models for reliability prediction                                                                                                                       |

|                                                                 | CTE mismatch for large interposers                                                                                                                        |

|                                                                 | - Defect density at very thin interfaces                                                                                                                  |

| Interposers and Embedded                                        | - Low cost embedded passives: R, L, C                                                                                                                     |

| components                                                      | - Embedded active devices                                                                                                                                 |

|                                                                 | Quality levels required not attainable on chip                                                                                                            |

|                                                                 | Electrical and optical interface integration                                                                                                              |

|                                                                 | - Wafer level embedded components                                                                                                                         |

| Thinned die packaging | - Handling technologies for thin wafers (particularly for bumped wafers)                    |

|-----------------------|---------------------------------------------------------------------------------------------|

|                       | - Impact of different carrier materials (organics, silicon, ceramics, glass, laminate core) |

|                       | - Establish new process flows                                                               |

|                       | - Reliability                                                                               |

|                       | - Testability                                                                               |

The challenges for geometries below 16 nm include the items listed below. These challenges reflect the fundamental changes associated with continued scaling. The challenges are complex and will require substantial innovation.

| Table AP1:                                                        | Assembly and Packaging Difficult Challenges (continued)                                         |

|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Difficult Challenges ≤ 16 nm                                      | Summary of Issues                                                                               |

| Close gap between chip and substrate, Improved Organic substrates | - Increased wireability at low cost                                                             |

|                                                                   | - Improved impedance control and lower dielectric loss to support higher frequency applications |

|                                                                   | Improved planarity and low warpage at higher process temperatures                               |

|                                                                   | - Low-moisture absorption                                                                       |

|                                                                   | - Increased via density in substrate core                                                       |

|                                                                   | Silicon I/O density increasing faster than the package substrate technology                     |

| High current density packages                                     | -Low resistance contacts                                                                        |

| riigii current density packages                                   | - Electromigration                                                                              |

|                                                                   | - Conformal low cost organic substrates                                                         |

| Flexible system packaging                                         | - Small and thin die assembly                                                                   |

|                                                                   | - Handling in low cost operation                                                                |

|                                                                   | - Thermal management                                                                            |

|                                                                   | - Design and simulation tools                                                                   |

|                                                                   | - Wafer to wafer bonding                                                                        |

| AD 11 1 1 1                                                       | Through wafer via structure and via fill process                                                |

| 3D assembly and packaging                                         | - Singulation of TSV wafers/die                                                                 |

|                                                                   | - Test access for individual wafer/die                                                          |

|                                                                   | - Cost of TSV                                                                                   |

|                                                                   | - Bumpless interconnect architecture                                                            |

| Package cost does not follow the                                  | Margin in packaging is inadequate to support investment required to reduce cost                 |

| die cost reduction curve                                          | Increased device complexity requires higher cost packaging solutions                            |

|                                                                   | Electromigration at high current density for interconnect (die, package).                       |

| Small die with high pad count                                     | - Thermal dissipation                                                                           |

| and/or high power density                                         | - Improved current density capabilities                                                         |

|                                                                   | - Higher operating temperature                                                                  |

|                                                                   | - Substrate wiring density to support >20 lines/mm                                              |

| Tr. 1.6                                                           | - Lower loss dielectrics                                                                        |

| High frequency die                                                | - "Hot spot" thermal management                                                                 |

|                                                                   | - Package substrates with lines and spaces below 10 microns.                                    |

|                                                                   | I.                                                                                              |

| System-level design capability to integrated chips, passives, and                                   | <ul> <li>Partitioning of system designs and manufacturing across numerous companies will make<br/>required optimization for performance, reliability, and cost of complex systems very difficult.</li> </ul> |

|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| substrates                                                                                          | <ul> <li>Complex standards for information types and management of information quality along with a<br/>structure for moving this information will be required.</li> </ul>                                   |

| Emerging device types (organic, nanostructures, biological) that require new packaging technologies | - Organic device packaging requirements not yet defined (will chips grow their own packages)                                                                                                                 |

|                                                                                                     | - Biological interfaces will require new interface types                                                                                                                                                     |

| Power Integrity                                                                                     | - Power supply quality                                                                                                                                                                                       |

|                                                                                                     | - Power delivery in stacked die                                                                                                                                                                              |

|                                                                                                     | - Reducing power supply voltage with high device switcihng currents                                                                                                                                          |

#### 3. SINGLE CHIP PACKAGING

#### **OVERALL REQUIREMENTS**

Electronics and electronic products are being deeply woven into the fabric of our society. Without electronics, cars and trains will not move, planes would not fly, and certainly home appliances and home entertainment systems, and personal mobile devices (cell phones, smart phone, tablets), laptops and desktops and others would not function. From communications, commerce, transportation, energy, environment medical and health, electronics has provided the tools for operations, global productivity, innovation, improvement and sustaining of the standards of living for people everywhere.

The ubiquitous electronic components continue to find applications in traditional markets for data processing, communication networks and computing, military and aerospace as well as new applications in personal communication such as smart phones and PDA, game consoles, home and home entertainment, medical and health care, energy and environment, automotive, and security systems. New device categories such as light emitting diodes, photonic devices, MEMs and other sensors add families of integrated circuits for packaging and assembly into electronic components. The advent of cloud computing coincide with double digit growth in bandwidth requirements accentuate the demand for high performance network systems and servers which provide the backbone structures to global internet traffic and data flow.

Figure AP1: Hardware Components of Cloud Computing

The dynamics of market requirements and new device types led to requirements for new packaging technologies and new packaging architecture. In this chapter the packaging and assembly technology requirements are divided into devices serving five different market segments:

- Low cost low end: Low end consumer electronics and memory, e.g. electronics in household appliances, toys, MP3, DVD players, portable hard drive products, electronic books, and cell phones.

- Mobile Products: Smart phones, high end cell phones, portable personal devices, portable video systems.

- Cost Performance: PC, notebook, tablets, and high-end electronic books, Blade server and processors, game consoles, and small business routers and servers.

- High End: High performance servers, routers and network systems and computers.

- Harsh Environment: Automotive, aerospace, and military systems.

There will be gray areas between the five market segments. While the very low end cell phone belongs to the low end market, it is, by definition, part of the mobile market. And the game consoles performance rival those of blade servers. Tablets and electronic readers are duplicating functions in market competition. The market momentum for mobile video entertainment is elevating the speed and bandwidth for mobile products and drive the speed, bandwidth and capacity of network system infrastructure, and server farms. The advent of cloud computing connects mobile intelligence platforms with fixed network infrastructure and database, blurring the boundary between the market segments in functions, form factors and price points.

For each of the five market segments, their technology requirements, cost per pin, die size, power, package pin count, operating characteristics, and environments, have been addressed in Table AP2. Where solutions are not proven or unknown, they will be color coded to show the solution status. In many cases the reason for the color is not that the parameter cannot be met, but that the cost of implementation would be beyond the cost targets for that specific product segment.

#### *Table AP2:* Single-chip Package Technology Requirements

The technology requirement for the Cost Performance Market has been the leader for package technology innovations in the past decade with the drive for performance in notebooks, game consoles, routers, and servers as the technology nodes advances while keeping cost at bay. The leading package technologies are flip chip ball grid array organic packages with large die and high density. The issues have been performance, heat dissipation, reliability and cost.

The dramatic rise of the mobile market with smart phones, tablets, portable personal devices, and portable entertainment systems has brought up a different set of technology challenges in form factors (height and size) and weight, functional diversification such as RF and video, system integration, reliability, time to market, and cost. The packaging community has responded with wafer level packaging, new generations of flip chip CSPs, various forms of SiP including 3D stacked die and stacked packages, fine pitch surface mount, silicon and glass interposers (2.5D) and 3D IC. They illustrate the dynamic nature of the Packaging and Assembly world in "More Moore" and "More than Moore". The dramatic escalation and gyration in the price of gold works against consumer market expectations for cost reduction. It has given great impetus to the conversion from gold wire bond to copper wire bond. As the experience in conversion from lead solder materials to non-lead solder materials, the replacement of gold wire by copper wire in fine pitch wire-bonding lead to a very significant set challenges in new assembly process development, a whole set of material changes and equipment infrastructure. In Cu wirebond the industry is seeing major challenges in what commonly perceived as "mature" technology with well-established manufacturing infrastructures. For flip chip technologies the transition from lead based solder to lead free solder, and the implementation of low-κ d e-low-κ and ultra low-κ dielectric and finer bond pad pitch adds a new set of challenges to the packaging technologists. With flip chip moving towards cu pillar bumping for reasons of finer pitch and lower cost solutions, one would find that new materials set and different assembly process and equipment would be required. In wafer level packaging WLCSP is the fastest growing packaging type driven by the mobile phone market. This packaging technology is being re-invented to expand its application space in response to market demand for minimum package thickness and small form factor.

#### **ELECTRICAL REQUIREMENTS**

Manufacturing tolerances have a major impact on the performance of electrical designs. The manufacturing tolerance roadmap reflected by the tables, for via diameter, via alignment, metal thickness, line width and dielectric thickness must be aligned with the electrical requirements. The major issues defining requirements for single chip packages are discussed below.

#### **CROSS TALK**

Circuit speed and density continue their improvements from one CMOS generation to the next. Faster circuits translate into shorter clock cycles and increased density gives rise to more closely spaced parallel threads. These

device advancements demand increased package I/O at ever-increasing speed. These advanced circuits require packages that minimize device, package, and system noise.

A major noise source is crosstalk between parallel signal lines. Crosstalk noise is roughly proportional to the ratio of dielectric thickness to edge spacing between adjacent signal lines. For a given signal line width and spacing, a lower dielectric constant medium requires a thinner dielectric to obtain the same characteristic impedance, resulting in smaller crosstalk noise. Cross talk issues are also associated with fine pitch bonding wires and fine pitch vias.

#### **POWER INTEGRITY**

Power integrity issues are becoming more critical for high-speed integrated circuits as frequency and increases and operating voltage decreases. Discrete decoupling capacitors are extensively used today to damp AC noise. The Equivalent Series Inductance (ESL) associated with discrete capacitors is the major factor limiting performance at high frequency. Embedded planar capacitors and on-die decoupling cells are used to reduce high-frequency noise due to high ESL in discrete capacitors. The cost and complexity of on-die decoupling will be an increasing problem. Due to resonance between package and die and package and PCB, it is difficult to control power distribution impedance over a wide frequency range. This results in a packaging related bottle-neck in high-speed power delivery system design and new technology is required.

#### THERMAL REQUIREMENTS

Temperature control is critical for the both operating performance and long term reliability of single chip packages. The high junction-to-ambient thermal resistance resulting from an air-cooled heat sink provides inadequate heat removal capability at the necessary junction temperatures for ITRS projections at the end of this roadmap. Today, a massive heat sink, which may be larger than the chip by orders of magnitude, is attached to a silicon chip through a heat spreader and variety of thermal interface materials (TIM). Not only does this insert a large thermal resistance between the chip and the ambient, it also limits the chip packing density in electronic products thereby increasing wiring length, which contributes to higher interconnect latency, higher power dissipation, lower bandwidth, and higher interconnect losses. The ITRS projected power density and junction-to-ambient thermal resistance for highperformance chips at the 14 nm generation are >100 W/cm<sup>2</sup> and <0.2°C/W, respectively. The main bottlenecks in reducing the junction-to-ambient thermal resistance are the thermal resistances of the thermal interface material (TIM) and the heat sink. There is a need for TIMs that provide the highest possible thermal conductivity, are mechanical stable during chip operation, have good adhesion, and conform to fill the gaps between two rough surfaces. To address this need, new TIMs are being explored. The integration of carbon nanotubes (CNTs), which exhibit very high thermal conductivity, within a TIM's matrix is being investigated. More details may be found in the Emerging Materials chapter. The die stacking 3D and interposer (2.5D) package architecture give challenges thermal solutions in limited space for thermally designed package solutions. There has been a commonly held assumption that mobile devices, powered by batteries would not require thermal management solutions. With stacked POP design packages and 3D architecture, thermal design will be an important technical challenge.

#### **HOT SPOTS**

Hot spot thermal management generally dictates the thermal solution of the component. Even when the total power of a component is unchanged, hot spot power density increase could limit the device performance. While this is a critical issue for SiP it is also important for single chip devices such as SoC circuits, high power lasers and diodes, RF devices and other high power devices that have portions of the die generating thermal loads substantially higher than the die average.

New liquid and phase change (liquid to gas) active heat sinks are in limited use today and are addressed in more detail in the System in Package section of this chapter. They hold the promise of decreased thermal resistance and improved heat spreading capability to address the effect of hot spots.

#### MECHANICAL REQUIREMENTS

The constant drive for increased functionality and flexibility in the end product will be the key driver for the electronic industry in future. With shorter design turns and faster time to market, there is little room for error during the design, development, and validation phases. The continued geometric scaling of integrated circuits and the introduction of low- $\kappa$  and e-low-k dielectric film materials raise serious concerns about mechanical stress damage in the dielectric layers due to thermo-mechanical stresses in the combined package device structure. Chip package interaction (CPI) has become a major area for trade off between die designers and packaging engineers. Legislative

requirements for lead free and halogen free materials in electronic products introduced higher temperature stresses and new packaging materials and materials interfaces into the package. New package types including stacked die packages, Package on Packages (PoPs), Package in Packages (PiPs), and wafer level packages have brought forth new failure mechanisms. This is especially true for 3D TSV and interposer based packaging architectures.

Consumers in the mobile market demand more functions and faster performance in thin handheld size package. Stacked die and stacked packages are by its very nature "thickness challenged". The drive for reducing package thickness across the different package types poses challenges in architecture, materials and design innovations.

The packaging industry will face the challenge of integrating multiple device technologies such as digital, RF and MEMS, optoelectronics, displays and others on the same packaging platform. Expanding consumer markets introduced new paradigms in reliability requirements. For example drop tests, in various forms, are being added to components to be used in cell phones and other portable electronic products. To ensure reliability of the end products, it is imperative to have focused R&D efforts in mechanical and thermal modeling and simulation tools.

#### MECHANICAL MODELING AND SIMULATION

Electronic packages represent a classic case of convergence of multi-scale, multi-physics, multi materials, and multimaterials interface systems. The length scale varies from nm to cm, a wide range of materials with mechanical properties from stiff and brittle inorganics like Si, glass and other dielectrics with property modifications such as micro-pores to achieve low-κ, to softer materials like solders or polymers and polymer composites with very nonlinear time and temperature dependent material behaviour are combined. Material response varies from elastic to non-linear in time-temperature dependent characteristics. It is critically important to have practical and usable tools for predictive thermal mechanical and dynamic modeling of electronic packaging structures to assist packaging engineers in predicting failure modes and elucidate the failure mechanisms in the development stages. This would enable trade-offs in design, materials and manufacturing processes, and ultimately in feature, performance, cost, and time to market. Such predictive modeling tools would need to be integrated into device package co-design environments. Coupled analysis for thermal, electrical, hydrothermal, and mechanical characteristics is also needed.

Accurate experimental techniques to observe and experimentally measure mechanical deformation such as package and die warpage will be very important to observe the package deformation phenomena and to quantitatively verify the physical models. Warpage has been typically defined as the largest value of non-planarity. For full understanding of package deformation full field warpage including z and x-y deformation will be highly desirable.

To complement mechanical analysis and modeling efforts, it is necessary to develop accurate materials properties data over a range of loading and environmental conditions. Characterization of interface properties such as polymer/metal and polymer/polymer interface fracture toughness and micromechanical properties is required. A key challenge in this area is associated with the small dimensions. Bulk properties are often not usable for thin material layers. Interface effects, grain size and pre-stresses due to process or adjacent materials become very important. Metrologies are needed that can handle thin films of sub-micron thickness to measure both bulk and interfacial response. Properties of materials such as intermetallics formed from solder under bump metallurgy (UBM) metals interaction which grow and evolve over time and temperature will be required. Physical failure mechanisms such as electromigration, thermal migration in combination with mechanical stresses need to be understood and modeled for practical life assessment.

There is also a need to develop metrologies that can be used to efficiently measure either stress or strain under both thermal and mechanical loading conditions in thin films (for example in layers within Silicon) in packaged form. For example, interferometry-based techniques with sub-micron resolution are required whereas the current state of art methods have spatial resolution of 1 to 2 µm. Efforts are needed in extending other known techniques such as digital image correlations, micro-Raman spectroscopy, and PZT sensors to sub-micron length scales.

#### Cost

The continuous reduction in cost per function has been the key to growth of the electronics industry. This has been achieved historically through scaling of the wafer fabrication processes and improvements in design. The cost of assembly and packaging has not kept pace with the cost reduction in wafer fabrication and today packaging costs often exceed silicon IC fabrication cost. The cost reduction challenge is made more difficult by several factors increasing cost of packaging. Cost of packaging materials such as bonding wire, molding compound, substrate,

leadframe, contributes substantially to the cost of the package. The cost of gold wire is a substantial portion of the package cost. With the dramatic escalation of gold price, maintenance of package cost requires game changing strategies such as the high level of momentum shifting to copper wire from gold wire. Reducing cost is a important motivation for innovations from flip chip CSP to WLCSP.

Lead-free solder materials, halogen free molding compounds, low- $\kappa$  dielectrics, and high- $\kappa$  dielectrics are more costly than the materials they replace. Higher processing temperatures and a wider range of environmental temperature associated with portable consumer electronics require new, more expensive, substrate and interconnect technology. The increasing power density and decreasing junction temperature require more efficient thermal management. The details of the chip to package substrate technology are covered in Table AP3 and the specific issues associated with package warpage during processing are covered in Table AP4. The changes in substrate to board pitch are covered in Table AP5.

New technology is required to meet the demand for more cost effective packaging. Wafer-level packaging and systems in a package (SiP) are among the innovative approaches to reduce cost and achieve advantages of scaling similar to the front end processes.

Table AP3: Chip-to-package Substrate Technology Requirement

Package Warpage at Peak Processing Temperature

Table AP5: Substrate to Board Pitch

#### RELIABILITY

*Table AP4:*

Rapid innovation in packaging is evident from the introduction of new package formats including area array packages (flip chip BGA and flip chip CSP); leadless packages, direct chip attach, wafer level packaging (WLP), wirebond die stacking, flip chip Cu Pillar and FC-wirebond hybrid, PoP, PiP and other forms of 3D package integration. With 3D TSV and Silicon or Glass Interposers, new failure mechanisms and package risks needs to be identified. In addition there are new packaging requirements emerging such as Cu/E low-κ materials, interconnects to address the need for flexibility and expanding heat and speed requirements. The introduction of low-κ and e-low-κ materials makes the low κ layer in the chip susceptible to mechanical stresses in the combined chip package structure. New environmental constraints such as Pb-free and halogen-free requirements enforced by law, and use of electronics in extreme environments also force rapid changes. The introduction of these new materials and package architectures are posing new reliability challenges. For example in the flip chip package the interaction of the stiffer Pb free solder bump to the mechanically weaker low k dielectric requires chip and design and materials selection to address reliability risks in chip to packaging interaction (CPI). This comes at a time when there must be substantially higher reliability on a per transistor basis to meet market requirements. Many of the reliability issues involve the Chip to Package Substrate Technology which is covered in Table AP3.

Some new package designs, materials, and technologies will not be capable of the reliability required in all market applications. More in-depth knowledge of failure mechanisms coupled with knowledge of end product use conditions will be required to bring reliable new package technologies into the market-place. For example mobile products have drop test requirements for dynamic mechanical integrity in drop impact environments.

There are many factors that determine the reliability of electronic components. The factors that must be considered are similar for all systems but the relative importance changes for consumer products. Consumer products have higher thermal cycle count due to the use pattern of consumer electronics and greater mechanical stress due to vibrations and dropping for the same reason. Typical package failure modes are presented in Table AP6.

Table AP6: Package Failure Modes

The storage and use environments also have a wider range than components not used in consumer applications. Meeting the reliability requirements for future components will require tools and procedures that are not yet available. These include:

- Failure classification standards

- Identification of failure mechanisms

- Improved failure analysis techniques

- Electrical/thermal/mechanical simulation

- Lifetime models with defined acceleration factor

- Test vehicles for specific reliability characterization

- Early warning structures

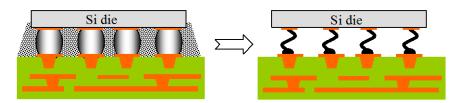

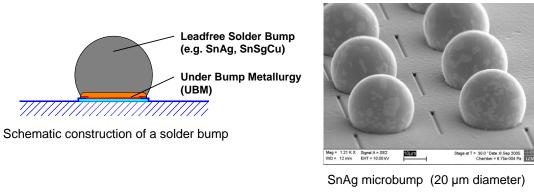

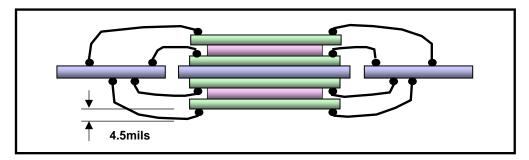

As described earlier, the use of low-k ILD to reduce on-chip interconnect parasitic capacitance has exacerbated the difficultly of maintaining high thermomechanical reliability of die assembled on organic substrates in flip chip packages. Due to the fragile nature of low-κ ILDs in the die and their relatively poor adhesion to the surrounding materials, it is becoming progressively critical to minimize stresses imparted on the chip during thermal cycling and wafer-level probing. The large CTE mismatch between the silicon die (3 ppm/°C) and the organic substrate (17 ppm/°C) have been shown to be destructive for ILD materials and their interfaces. This issue has motivated the investigation of new I/O interconnect technologies that minimize mechanical stresses on the chip. The pending replacement of lower modulus lead solder bump material by lead free solder bump material or copper pillar makes the problem more difficult. To this end, the device and package communities must collaborate together to address the chip package interaction issue in the design of UBM structure, solder bump or Cu pillar, underfill materials, and surface finishes. In addition, the use of solder bumps augmented with mechanically flexible electrical leads to replace underfill is a potential solution.

In addition to compliant/flexible interconnects, thin solder interconnects and micro-bumps (diameter: <20 µm) as well as Cu pillar bump structures (Figures AP2 and AP3) are used to improve interconnect reliability. The selection of the type will depend on die sizes, thickness and interconnect density.

Moving forward reliability considerations of dies with TSV and microbumps will pose significant challenges to the chip and package designers and their reliability counterparts. This will be addressed in future editions for the roadmap.

Figure AP2: The Use of Compliant/Flexible I/O Can Potentially Eliminate the Need for Underfill

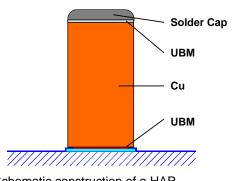

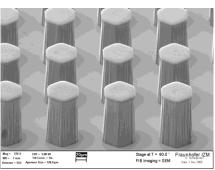

Schematic construction of a HAR (High Aspect Ratio) Cu pillar bump with solder cap

Cu pillar bump (height: 80 µm)

Figure AP3: Micro Bump and Pillar Bump Structures for High Reliable Chip-to-Substrate Interconnects

#### CHIP TO PACKAGE SUBSTRATE

There are several factors that drive the selection of the appropriate chip to package substrate technology. The issues are addressed in Table AP3 Chip-to-package Substrate Technology, Table AP4 Package Warpage at Peak Processing Temperature, and Table AP5 Substrate Board Pitch. The specific technologies are discussed in the sections below.

#### INTERCONNECT TECHNOLOGIES FOR SINGLE CHIP PACKAGE

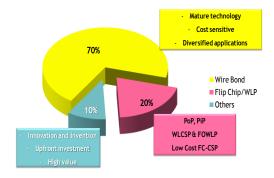

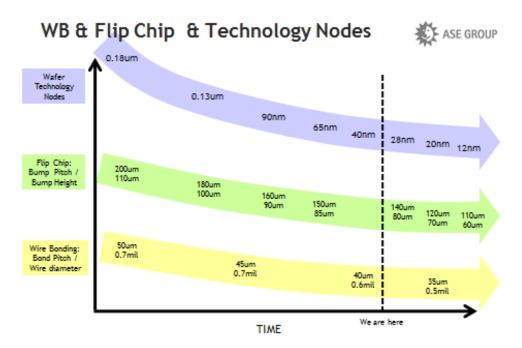

Single Chip package is till the volume leader, and wirebond and flip Chip continue to be the two basic interconnect technology for the semiconductor packaging industry. Today in IC packaging (excluding LEDs, MEMs and discretes) wirebond serves as the basic interconnect technology for 87% of the unit in production and flip chip interconnect serves as the basic interconnect technology for 12% of the units in production. In terms of package value the ratio is about 70% and 20%. There has been major and significant innovations in both interconnect technologies in the last few years in response to dynamic market requirements and technology node advancement.

Figure AP4: Wirebond and Flip Chip Pitch versus Technology Nodes

#### **WIRE BONDING**

Wire bonding has been the workhorse of the semiconductor industry. It is the dominant method for interconnecting to semiconductor device. IC devices, wire bonded to various forms of lead frames and organic substrates and molded in epoxy molding compounds have been the standard of the industry for years. Despite repeated predictions that wire bond technology has reached its practical physical limit, wire bond technology continues to re-invent itself with new innovative concepts and technology improvements. Today it has been estimated that 70% and more of the world semiconductor components are packaged in wirebond.

In the last few years year the replacement of gold with copper wire in fine pitch wirbond packages has moved into mainstream. A majority of new wirebond packages will be using Cu wire and PdCu wire. And momentum is building to convert Au to Cu (including Pd Cu) in existing packaged components. The implementation of Cu wirebond requires changes of almost the entire packaging materials set, and assembly manufacturing equipment infrastructure. In other words the industry has completely re-invented the wirebond technology in bonding wires, in wire bonders, in molding compounds, and in the manufacturing infrastructure. The implementation for Cu Wire is remarkable in the rapid market acceptance to a major high volume manufacturing technology change.

Replacement of Au wire by Cu is being implemented across both generic package types, e.g. leadframe and PBGA. At the same time the introduction of advanced nodes and low  $\kappa$  materials will demand finer diameter wires for Au as well as Cu below the 18 um being practiced today. While copper wirebond has been in use for power devices with

50 micron diameter wires and low IO counts, fine pitch Cu wirebond is a recent development. Fine pitch applications with Cu wire diameters at 25 micron and below requires improvements in understanding of wire properties, IMC formation and evolution, wire bonding processes and equipment development and control for wire oxidation.

Pd coated wire has been introduced to eliminate the need for forming gas in production.

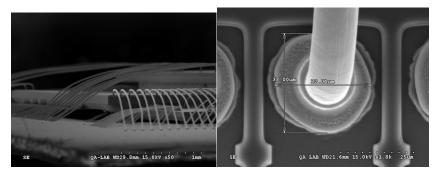

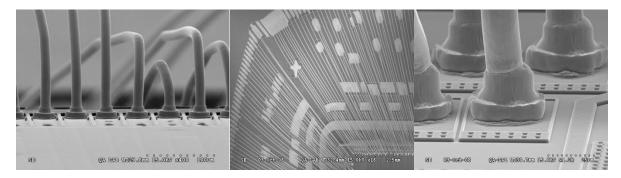

Multi-tier wire bonding has provided good practical solutions to meet increased IO requirements. Wire bonded stacked die packaging, typically with two to five vertically stacked dies with a leadframe, laminate substrate or flex circuit base has proven to be particularly versatile method for multi-chip or SiP in the mobile market. While the majority is for various memory to memory combinations, a significant proportion involves memory stacked with logic devices. The developments that enabled die stacking package include wafer thinning, low profile wire bonding, mold compound flow and filler size, and wafer level test for known good die. Shown below is example of stacked die Cu Wirebond structure with 15 µm Cu wire.

Figure AP5: Example of 15 µm Cu Wire Bond with Die Stacking

In order to meet thinner and more densely integrated package requirements lower profile wire bond loops are necessary. Innovations such as forward bond loops with 50  $\mu$ m loop height are in production. Other innovations such as die to die bonding and cascade bonding are shown in Figure AP6. While many of these developments have been in production for Au wires, it is expected that these capabilities would be extend Cu wirebond in time.

Figure AP6: Example of Multi-Tier Cu Wire Bonding with 847 Lead PBGA

Some of the technology issues being addressed are bonding overhang die and wire bonding on both sides of the lead frame shown in Figures AP7 and AP8.

Figure AP7: Bonding Overhang Die

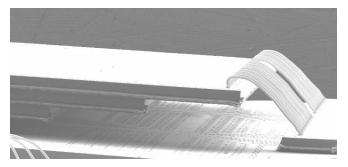

Figure AP8: Wire Bond on Both Sides of Lead Frame Substrate

There is a well-established global infrastructure and supply chain for wire bonded and molded packages from design practices and tools, materials, manufacturing processes, and equipment. The industry has been developing faster wire bonders, larger format substrate assembly, and more efficient molding processes to address the market demand for efficiency and cost saving. The next few years will see significant innovations in design, process, materials and equipment for the implementation of Cu wirebond. As the wafer technology approaches 45 nm node and below, the bonding wire diameter will be reduced correspondingly to 20 nm and below. In the long term such cost improvements efforts may be approaching their practical limits and are of diminishing returns.

#### FLIP CHIP

Flip chip and wire bond are the two standard processes to connect die to a substrate. Flip chip PBGA processes evolve from technologies originally developed for multi-chip applications on ceramic modules with high lead solder bumps. It has become the standard die interconnect solution for organic substrates for microprocessors and graphics processors in the cost performance and high end markets. The key elements are: wafer bumping (UBM and bump metallurgy), underfill, TIM, and build-up substrates. For these applications flip chip pitch, lower than 150 µm, has been limited by availability of high-volume cost-effective substrates and high-volume defect-free underfill processes, with higher Pb-free temperature, higher Tj, and increased current density, there are requirements to improve underfills, UBM structure, high lead solder, eutectic and lead free alternatives, and TIM materials in order to meet the demands of future technology nodes and market applications. Plated wafer bumping including copper pillar wafer bumping is being introduced in microprocessor applications and will be expanded to broader applications. The advantages are in finer pitch, lead free and electrical/thermal performance.

Figure AP9: Examples of Copper Pillar Bumps (a) and Assembled Copper Pillar (b) X-Ray

Figure AP10: Example of Copper Pillars with Solder Tips Single Line 50 µm Pitch (staggered (100 µm)

For applications beyond the microprocessor, graphics and game processors, flip chip FC CSP packages have been developed for applications with smaller die, lower IO array pitch and low profile small package format requirements. Primary driver has been the mobile market application, and drop test is an important requirement. Laminate substrate and 1+2+1 buildup substrates are used to meet cost targets. To save cost of redistribution process the bond pads would remain in peripheral single line or staggered. These flip chip CSP packages may have multiple dies side-by-side or they may be stacked onto other flip chip and wire bond packages. Analog and RF ICs have different electrical requirements than digital only applications. The industry has developed several package variations to meet different application requirements, In addition to the classical capillary underfill process, they include molded underfill and underfill plus molding processes. The large format molded underfill process provides significant cost saving. Potential solutions include redesigned UBM, copper pillar or flexible interconnect, fluxless reflow and PoP and PiP package structures. There is a movement for a new generation of flip chip structures, materials, manufacturing processes and equipment sets to serve the industry for the More than Moore era. A good example is the flip chip CSP package with copper pillar bump, bond on lead assembly process, molded underfill with low cost laminate substrate in large format.

#### MOLDING

Conventional bottom-gate molding has been a highly successful workhorse for the industry. For some complex stack dice and complex SiP package there is risk for excessive wire sweep and yield loss. Recent industry adoption in top center mold gate (TCMG) process provides a radial mold compound flow from a top gate that minimizes wire sweep

and filler separation that can occur as the fine pitch bond wires filter out part of the fillers as the compound moves between them.

Also compression molding is entering the mainstream. The liquid mold compound is dispensed onto the substrate before it is placed into the mold die. No gate is needed and the mold flow speed is minimized preventing wire sweep. Lower cost powder molding compound developed for compression molding process is coming on board.

Thin packages are prone to warpage, and chips with low-κ dielectrics are more sensitive to stress. In both cases, low modulus molding compounds are in development to minimize the problems.

A novel approach to reduce or eliminate the occurrences of wire shorts in molding is the use of coated wire. Coated wire has been in development for some years and has achieved some level of technical success. However the high cost of coated wire has limited its application and prevented its broad proliferation into the industry.

#### PACKAGE SUBSTRATE TO BOARD INTERCONNECT

#### LEAD FRAMES

Lead frame carriers have thrived for their low cost and good reliability for more than 30 years. They are expected to continue to thrive with innovations in package design and processes. New material related challenges appeared because environmental and health regulatory requirements demand the elimination of Pb. The move from Pb to Sn led to the challenge of tin whiskers. For improved reliability and low-cost new plating materials are required, e.g., based on NiPd, Cu, lead-free solder alloys. Other challenges include improved heat dissipation and higher interconnect density including increased pin count capability for platforms such as QFN and QFP. Innovations in advanced multi-row QFN has extended the I/O and performance for QFN packages.

#### **HIGH DENSITY CONNECTIONS**