# INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS

# 2011 EDITION

# DESIGN

THE ITRS IS DEVISED AND INTENDED FOR TECHNOLOGY ASSESSMENT ONLY AND IS WITHOUT REGARD TO ANY COMMERCIAL CONSIDERATIONS PERTAINING TO INDIVIDUAL PRODUCTS OR EQUIPMENT.

THE INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS: 2011

# TABLE OF CONTENTS

| Scope                                                         | 1  |

|---------------------------------------------------------------|----|

| Overall Challenges                                            |    |

| Detailed Design Technology Challenges                         |    |

| Design Methodology                                            | 6  |

| System-Level Design                                           |    |

| Logical, Circuit and Physical Design                          |    |

| Design Verification                                           | 16 |

| Design For Test                                               |    |

| Design For Manufacturability (DFM)                            | 28 |

| More Than Moore Analysis                                      | 35 |

| Analog, Mixed-Signal and RF Specific DT Trends and Challenges | 35 |

| Cross-cut TWG Issues                                          | 39 |

| Modeling and Simulation                                       | 39 |

| Appendix I: Variability Modeling and Roadmap                  | 39 |

| Appendix II: DT Cost and Value                                | 41 |

| Appendix III: DT-Based Reductions of Power Consumption        | 45 |

| Appendix IV: Design Challenges for 3DIC                       | 47 |

# LIST OF FIGURES

| Figure DESN1  | Impact of Design Technology on SOC Consumer Portable<br>Implementation Cost | 2  |

|---------------|-----------------------------------------------------------------------------|----|

| Figure DESN2  | The V-Cycle for Design System Architecture                                  |    |

| Figure DESN3  | Hardware and Software Design Gaps versus Time                               | 8  |

| Figure DESN4  | System-Level Design Potential Solutions                                     | 9  |

| Figure DESN5  | Evolving Role of Design Phases in Overall System Power Minimization         | 11 |

| Figure DESN6  | Logical/Circuit/Physical Design Potential Solutions                         | 15 |

| Figure DESN7  | Design Verification Potential Solutions                                     |    |

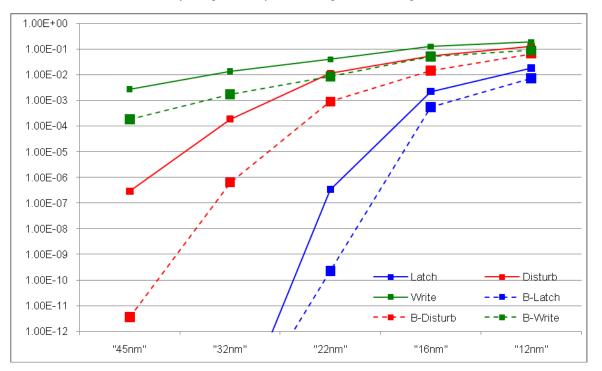

| Figure DESN8  | Variability-Induced Failure Rates for Three Canonical Circuit Types         |    |

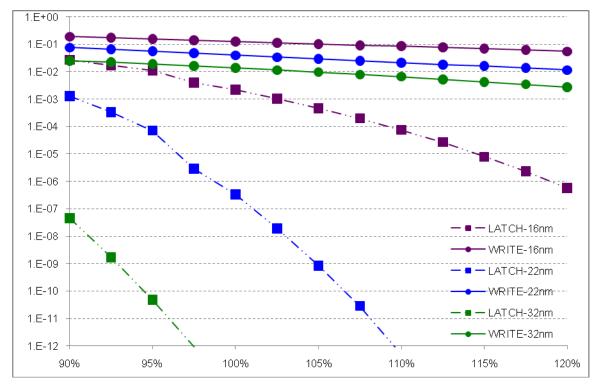

| Figure DESN9  | Power Supply-Dependent Failure Rates for Three Canonical Circuit Types.     | 31 |

| Figure DESN10 | Design for Manufacturability Potential Solutions                            | 33 |

| Figure DESN11 | Moore and Non-Moore Design Technology Improvements                          | 35 |

| Figure DESN12 | Possible Variability Abstraction Levels                                     |    |

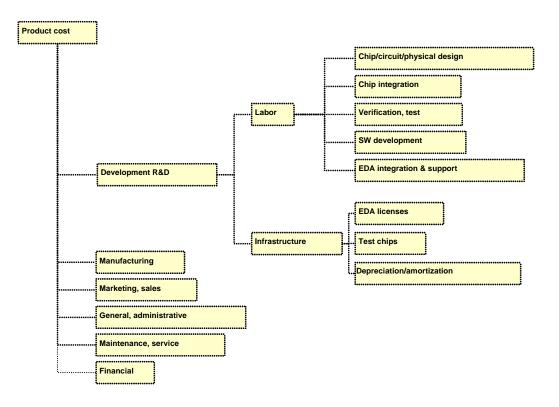

| Figure DESN13 | Simplified Electronic Product Development Cost Model                        |    |

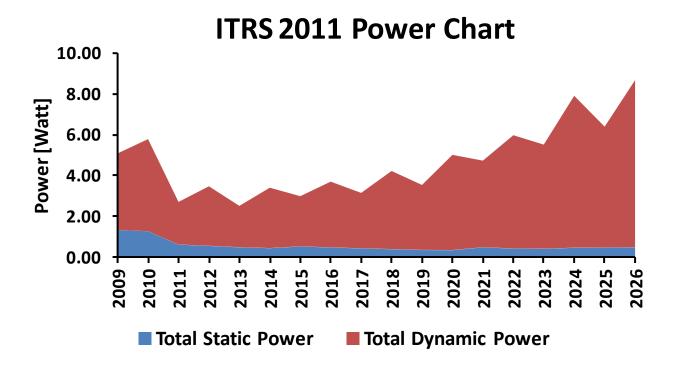

| Figure DESN14 | Impact of Low-Power Design Technology on SOC Consumer Portable              |    |

| -             | Power Consumption                                                           | 45 |

# LIST OF TABLES

| Overall Design Technology Challenges                                            | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System-Level Design Technology Requirements                                     | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Correspondence between System-Level Design Requirements and Solutions           | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Logical/Circuit/Physical Design Technology Requirements                         | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Correspondence between Logical/Circuit/Physical Requirements and Solutions      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Design Verification Technology Requirements                                     | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Verification Strategy Planning                                                  | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Correspondence between Design Verification Requirements and Solutions .         | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Design for Test Technology Requirements                                         | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Design for Manufacturability Technology Requirements                            | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Correspondence between Design for Manufacturability Requirements and Solutions  | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Required Simulation Models for AMSRF Design                                     | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Design Technology Improvements and Impact on Designer Productivity              | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Low-Power Design Technology Improvements and Impact on Dynamic and Static Power | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Three Phases of Design Product Maturity and Design Challenges in 3DIC           | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                 | System-Level Design Technology Requirements<br>Correspondence between System-Level Design Requirements<br>and Solutions<br>Logical/Circuit/Physical Design Technology Requirements<br>Correspondence between Logical/Circuit/Physical Requirements<br>and Solutions<br>Design Verification Technology Requirements<br>Verification Strategy Planning<br>Correspondence between Design Verification Requirements and Solutions .<br>Design for Test Technology Requirements<br>Design for Test Technology Requirements<br>Correspondence between Design for Manufacturability Technology Requirements<br>Design for Manufacturability Technology Requirements<br>Correspondence between Design for Manufacturability Requirements and Solutions .<br>Design for Manufacturability Technology Requirements<br>Correspondence between Design for Manufacturability Requirements and Solutions<br>Required Simulation Models for AMSRF Design<br>Design Technology Improvements and Impact on Designer Productivity<br>Low-Power Design Technology Improvements and Impact on Dynamic<br>and Static Power |

# DESIGN

# SCOPE

Design technology (DT) enables the *conception*, *implementation*, and *validation* of microelectronics-based systems. Elements of DT include *tools*, *libraries*, *manufacturing process characterizations*, and *methodologies*. DT transforms ideas and objectives of the electronic systems designer into manufacturable and testable representations. The role of DT is to enable profits and growth of the semiconductor industry via cost-effective production of designs that fully exploit manufacturing capability. In the 2011 ITRS, the International Technology Working Group (ITWG) for Design is responsible for the Design and *System Drivers* chapters, along with models for clock frequency, layout density, and power dissipation in support of the Overall Roadmap Technology Characteristics. Specific DT challenges and needs are mapped, as appropriate, to System Drivers. Readers of this chapter are encouraged to also review previous editions of the ITRS Design Chapter, which provide excellent and still-relevant summaries of DT needs.

The main message in 2011 remains—*Cost (of design) is the greatest threat to continuation of the semiconductor roadmap.* Cost determines whether differentiating value is best achieved in software or in hardware, on a programmable commodity platform, or on a new IC. Manufacturing non-recurring engineering (NRE) costs are on the order of millions of dollars (mask set + probe card); design NRE costs routinely reach tens of millions of dollars, with design shortfalls being responsible for silicon re-spins that multiply manufacturing NRE. Rapid technology change shortens product life cycles and makes time-to-market a critical issue for semiconductor customers. Manufacturing cycle times are measured in weeks, with low uncertainty. Design and verification cycle times are measured in months or years, with high uncertainty.

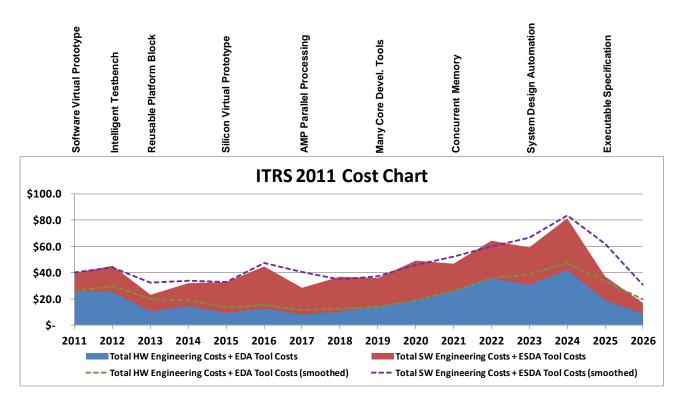

Previous editions of the ITRS have noted a *design productivity gap*—the number of available transistors growing faster than the ability to meaningfully design them. This gap impacts IC product value, placing at risk foundry amortization, return on investment (ROI) for supplier industries, and indeed the entire semiconductor investment cycle. Yet, investment in process technology continues to dominate investment in design technology. The DT roadmap enables control of design costs, as shown in Figure DESN1. In the figure:

1) Hardware aspects of design continue to witness soaring verification team sizes and test costs, and design for manufacturability (DFM) issues now permeate the design flow. DT innovations keep hardware design costs in check, at an estimated \$25.7M in 2011 for the consumer portable system-on-chip (SOC-CP) defined in the *System Drivers Chapter*, versus around \$7,708M had DT innovations between 1993 and 2009 not occurred.

2) Software aspects of IC design can now account for 80% or more of embedded systems development cost, with the industry having fully entered the era of multi-core designs, with both homogeneous and heterogeneous architectures. In 2011, with the addition of hardware-related software development cost, overall design cost reaches \$39.8M. Many DT innovations required in the next 15 years address software aspects of design; indeed, the design of concurrent software is noted as a long-term "Grand Challenge" for DT in the 2011 ITRS *Executive Summary*.

Failure to effectively develop and deploy the roadmap of DT innovations will break the long-standing trend of progress in the semiconductor industry. Hence, we view these DT gaps as crises that must be addressed in the next 15 years.

This chapter first presents *silicon complexity* and *system complexity* challenges, followed by five *crosscutting challenges* (productivity, power, manufacturing integration, interference, and error tolerance) that permeate all DT areas. The bulk of the chapter then sets out detailed challenges in the form of design technology requirements and solutions tables that comprise a *quantitative* design technology roadmap. The organization follows a traditional landscape of DT areas: design process; system-level design; logical, circuit and physical design; design verification; design test, and design for manufacturability.<sup>1</sup> These challenges are discussed at a level of detail that is actionable by management, R&D, and academia in the target supplier community, particularly the electronic design automation (EDA) industry. When appropriate, the detailed challenges are mapped to the microprocessor (MPU), system on chip (SOC, consumer or networking), analog/mixed-signal (AMS), and memory system drivers. Most challenges map to MPU and SOC, reflecting today's EDA technology and market segmentation. A brief unified overview of AMS-specific DT is also

<sup>&</sup>lt;sup>1</sup> Additional discussion of analog/mixed-signal circuits issues is contained in the System Drivers Chapter (AMS Driver). Test equipment and the test of manufactured chips are discussed in the Test Chapter, while this chapter addresses design for testability, including built-in self test (BIST).

provided. The overall approach to the chapter organization and discussion reflects the rise of application- and driver-specific DT.

## Figure DESN1 Impact of Design Technology on SOC Consumer Portable Implementation Cost

Roadmapping of DT is different from roadmapping of manufacturing technology. Manufacturing technology seeks to implement a set of requirements, and faces limits imposed by physical laws and material properties. In contrast, DT seeks to optimize designs so that they will meet their market requirements, and faces limitations imposed by computational intractability, the unknown scope of potential applications, and the multi-objective nature of design optimization. Because underlying optimizations are intractable, heuristics are inherent to DT, as are practical tradeoffs among multiple criteria such as density, speed, power, testability, or turnaround time. Evaluation of DT quality is thus context-sensitive, and dependent on particular methodologies or design instances. Furthermore, while ITRS technology generations occur discretely when all needed technology elements are in place, DT improvements can increase productivity or quality even "in isolation," and are thus deployable when developed.

# **OVERALL CHALLENGES**

DT faces two basic types of complexity—*silicon complexity* and *system complexity*—that follow from roadmaps for ITRS manufacturing technologies.

*Silicon complexity* refers to the impact of process scaling and the introduction of new materials or device/interconnect architectures. Many previously ignorable phenomena now have great impact on design correctness and value:

- *Non-ideal scaling of device parasitics and supply/threshold voltages* (leakage, power management, circuit/device innovation, current delivery)

- *Coupled high-frequency devices and interconnects* (noise/interference, signal integrity analysis and management, substrate coupling, delay variation due to cross-coupling)

- *Manufacturing variability* (statistical process modeling and characterization, yield, leakage power, with implications for, and impacts on, library characterization, analog and digital circuit performance, error-tolerant design, layout reuse, reliable and predictable implementation platforms)

- Complexity of manufacturing handoff (reticle enhancement and mask writing/inspection flow, NRE cost)

- Scaling of global interconnect performance relative to device performance (communication, synchronization)

- *Decreased reliability* (gate insulator tunneling and breakdown integrity, joule heating and electromigration, single-event upset, general fault-tolerance)

- *Codesign* (additional complexity of codesign of multiple chips and packages, especially with the introduction of 3D stacking technologies with Through-Silicon Vias (TSVs))

Silicon complexity places long-standing paradigms at risk, as follows: 1) system-wide synchronization becomes infeasible due to power limits and the cost of robustness under manufacturing variability; 2) the CMOS transistor becomes subject to ever-larger statistical variabilities in its behavior; and 3) fabrication of chips with 100% working transistors and interconnects becomes prohibitively expensive. Available implementation fabrics (from direct-mapped custom through general-purpose software-programmable) easily span four orders of magnitude in performance metrics (e.g., GOps/mW), and there is added opportunity to leave value on the table via ill-advised guardbands, abstractions, or other methodological choices. These challenges demand more broadly trained designers and design technologists, as well as continued mergers between traditionally separated areas of DT (synthesis-analysis, logical-physical, etc.).

*System complexity* refers to exponentially increasing transistor counts enabled by smaller feature sizes and spurred by consumer demand for increased functionality, lower cost, and shorter time-to-market.<sup>2</sup> Many challenges are facets of the nearly synonymous *productivity* challenge. Additional complexities (system environment or component heterogeneity) are forms of *diversity* that arise with respect to system-level SOC integration, and 3D integration. Design specification and validation become extremely challenging, particularly with respect to complex operating contexts. Tradeoffs must be made between all aspects of value or quality, and all aspects of cost. (A simplistic example: "Moore's Law" for performance might suggest a tradeoff of design time (= time-to-market) for performance at roughly 1% per week.) Implied challenges include:

- *Reuse*—support for hierarchical design, heterogeneous SOC integration (modeling, simulation, verification, test of component blocks) especially for analog/mixed-signal

- *Verification and test*—specification capture, design for verifiability, verification reuse for heterogeneous SOC, system-level and software verification, verification of analog/mixed-signal and novel devices, self-test, intelligent noise/delay fault testing, tester timing limits, test reuse

- *Cost-driven design optimization*—manufacturing cost modeling and analysis, quality metrics, co-optimization at die-package-system levels, optimization with respect to multiple system objectives such as fault tolerance, testability, etc.

- *Embedded software design*—predictable platform-based electronic system design methodologies, codesign with hardware and for networked system environments, software analysis and verification

- *Reliable implementation platforms*—predictable chip implementation onto multiple circuit fabrics, higher-level handoff to implementation

- Design process management—design team size and geographic distribution, data management, collaborative design support, "design through system" supply chain management, metrics and continuous process improvement

Together, the silicon and system complexity challenges imply *superexponentially increasing complexity* of the design process. To deal with this complexity, DT must provide concurrent optimization and analysis of more complex objectives and constraints, acknowledge added considerations such as design reuse and manufactured system cost in the design optimization, and encompass added scope such as embedded software design and interfaces to manufacturing. The sheer breadth of silicon and system complexities is also a challenge to roadmapping of DT and the electronic design automation (EDA) industry.

Five *crosscutting challenges*—1) design productivity (a near-term "Grand Challenge" for DT noted in the 2011 ITRS *Executive Summary*), 2) power management (a near-term Grand Challenge), 3) design for manufacturability (a near-term Grand Challenge), 4) interference, and 5) reliability and resilience (a long-term Grand Challenge)—underlie the design cost "meta-challenge" and have potential solutions that span all areas of DT. Three are highlighted as difficult challenges in the ITRS Executive Summary. *Design productivity* (a "cost-effective manufacturing" challenge) is closely linked to system and design process complexity, and is the most massive and critical DT, challenge both near and long term.

<sup>&</sup>lt;sup>2</sup> A "Law of Observed Functionality," notorious in consumer electronics, states that transistor count increases exponentially while the system value (utility) increases linearly (see T. Claasen, "The Logarithmic Law of Usefulness," Semiconductor International, July 1998).

*Power management* (an "enhancing performance" challenge) oscillates between a performance-driven active power crisis and a variability-driven leakage power crisis in the near term. *Design for Manufacturing* (a "cost-effective manufacturing" challenge) is required for the industry to produce chips in large quantities at acceptable cost and on economically feasible schedules: the past focus on lithography hardware limitations will broaden as variability in its many forms becomes a crisis, and deep integrations of DFM with yield management and design for test are needed. Table DESN1 summarizes key aspects of the crosscutting DT challenges.

*Crosscutting Challenge 1: Design Productivity.* To avoid exponentially increasing design cost, overall productivity of designed functions on chip must scale at  $> 2\times$  per technology generation. Reuse productivity (including migration and analog, mixed-signal, and RF (AMSRF) core reuse) of design, verification and test must also scale at  $> 2\times$  per technology generation. Implied needs are in: (1) verification, which is a bottleneck that has now reached crisis proportions, (2) reliable and predictable silicon implementation fabrics that support ever-high level electronic system design handoff, (3) embedded software design, which has emerged as the most critical challenge to SOC productivity, (4) particularly for the MPU context, improved productivity of large, distributed design organizations that work with tools from a variety of sources, and (5) automated methods for AMS design and test, which are required by the SOC and AMS system drivers. And (6) methods for optimal codesign of 3D systems, particularly 3D systems integrated using Through-Silicon Vias (TSVs) and emerging monolithic 3D technologies. These improvements require metrics of normalized design quality as a function of design quality, design NRE cost, manufacturing NRE cost, manufacturing variable cost, and semiconductor product value. Metrics of design technology quality such as stability, predictability, and interoperability must be improved as well. Time-to-market of new design technology must be reduced, e.g., via standards and platforms for interoperability and DT reuse.

| Challenges ≥ 22nm          | Summary of Issues                                                                                                                                                           |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design productivity        | System-level: high level of abstraction (HW/SW) functionality spec, platform-based design, multi-processor programmability, system integration, AMS codesign and automation |

|                            | Verification: executable specification, ESL formal verification, intelligent test bench, coverage-based verification                                                        |

|                            | Logic/circuit/physical: analog circuit synthesis, multi-objective optimization                                                                                              |

|                            | Logic/circuit/physical: SIP and 3D (TSV-based) planning and implementation flows                                                                                            |

|                            | Heterogeneous component integration (optical, mechanical, chemical, bio, etc.)                                                                                              |

| Power consumption          | Logic/circuit/physical: dynamic and static, system- and circuit-level power optimization                                                                                    |

| Manufacturability          | Performance/power variability, device parameter variability, lithography limitations impact on design, mask cost, quality of (process) models                               |

|                            | ATE interface test (multi-Gb/s), mixed-signal test, delay BIST, test-volume-reducing DFT                                                                                    |

| Interference               | Logic/circuit/physical: signal integrity analysis, EMI analysis, thermal analysis                                                                                           |

| Reliability and resilience | Logic/circuit/physical: MTTF-aware design, BISR, soft-error correction                                                                                                      |

| Table DESN1 Overall Design Technology Challenge |

|-------------------------------------------------|

|-------------------------------------------------|

| Challenges <22nm           | Summary of Issues                                                                                                                      |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Design productivity        | Verification: complete formal verification of designs, complete verification code reuse,<br>complete deployment of functional coverage |

|                            | Tools specific for SOI and non-static logic, and emerging devices                                                                      |

|                            | Cost-driven design flow                                                                                                                |

| Power consumption          | Logic/circuit/physical: SOI power management                                                                                           |

|                            | Logic/circuit/physical: Reliability and resilience- and temperature-constrained 3D physical implementation flows                       |

| Manufacturability          | Uncontrollable threshold voltage variability                                                                                           |

|                            | Advanced analog/mixed signal DFT (digital, structural, radio), "statistical" and yield-<br>improvement DFT                             |

|                            | Thermal BIST, system-level BIST                                                                                                        |

| Interference               | Interactions between heterogeneous components (optical, mechanical, chemical, bio, etc.)                                               |

| Reliability and resilience | Autonomic computing, robust design, SW reliability and resilience                                                                      |

ATE—automatic test equipment

BISR—built-in self repair

BIST—built-in self test

DFT—design for test

EMI—electromagnetic interference

ESL—Electronic System Level

HW/SW—hardware/software

MTTF—mean time to failure

SOI silicon on insulator

*Crosscutting Challenge 2: Power Management.* Non-ideal scaling of planar CMOS devices, together with the roadmap for interconnect materials and package technologies, presents a variety of challenges related to power management and current delivery. (1) Both the MPU and Consumer Portable drivers in the *System Drivers Chapter* require flat active and standby power, even as logic content and throughput continue to grow exponentially. DT must address the resulting *power management gap.* (2) Increasing power densities worsen thermal impact on reliability and resilience and performance, while decreasing supply voltages worsen leakage currents and noise. These trends stress on-chip interconnect resources (such as to control V = IR power supply drop in light of the *Assembly and Packaging* roadmap for bump count and passivation opening size), ATE equipment limits, and burn-in paradigms. The emergence of 3D technologies further complicates this problem as chips have to be codesigned to deliver power to co-stacked sub-systems while managing the number and location of TSVs. (3) Integration of distinct high-performance, low operating power (LOP), and low standby power (LSTP) devices demands power optimizations that simultaneously exploit many degrees of freedom, including multi- $V_{th}$ , multi- $T_{ox}$ , multi- $V_{dd}$  coexisting in a single core—while guiding additional power optimizations at the architecture, operating system, and application software levels. (4) Leakage power varies exponentially with key process parameters such as gate length, oxide thickness and threshold voltage; this presents severe challenges to both analysis and optimization in light of both scaling and variability.

*Crosscutting Challenge 3: Design for Manufacturing.* "Red bricks," that is, technology requirements for which no known solutions exist, are increasingly common throughout the ITRS. At the same time, challenges that are impossible to solve within a single technology area of the ITRS may be solvable (more cost-effectively) via appropriate synergies with DT. New interconnections between design and all other manufacturing-related disciplines lead to the rise of design for manufacturability (DFM), to which this DT roadmap devotes an entire section. Indeed, the feasibility of future technology nodes will come to depend on this communication. Several examples are as follows. (1) Tester equipment cost and speed limitations may be addressed by more rapid adoption of new fault models (for example, crosstalk, path delay), along with corresponding automatic test pattern generation (ATPG) and BIST techniques. (2) System implementation cost, performance verification, and overall design turnaround time (TAT) may be improved through diepackage-board co-optimization and analysis, as well as DT for system-in-package design. (3) CD control requirements in the *Lithography*, *Process Integration*, *Devices, and Structures* (PIDS), *Front-End Processing* (FEP), and *Interconnect* technology areas may be relaxed by new DT for correctness under manufacturing variability (e.g., variability-aware circuit design, regularity in layout, timing structure optimization, and static performance verification). (4) Manufacturing non-recurring costs can be reduced by more intelligent interfaces to mask production and inspection flows.

*Crosscutting Challenge 4: Interference.* Resource-efficient communication and synchronization, already challenged by global interconnect scaling trends, are increasingly hampered by noise and interference. Prevailing signal integrity methodologies in logical, circuit and physical design are reaching their limits of practicality. These methodologies include repeater insertion rules for long interconnects, slew rate control rules, power/ground distribution design for inductance management, etc. Scaling and SOC integration of mixed-signal and (radio frequency) RF components will require more flexible and powerful methodologies. Issues include noise headroom (especially in low-power devices and

dynamic circuits), large numbers of capacitively and inductively coupled interconnects, supply voltage IR drop and ground bounce, thermal impact on device off-currents and interconnect resistivities, and substrate coupling. A basic DT challenge is to improve characterization, modeling, analysis, and estimation of noise and interference at all levels of design.

*Crosscutting Challenge 5: Reliability and Resilience.* Relaxing the requirement of 100% correctness for devices and interconnects may dramatically reduce costs of manufacturing, verification, and test. Such a paradigm shift will likely be forced in any case by technology scaling, which leads to more transient and permanent failures of signals, logic values, devices, and interconnects. Several example issues are as follows. (1) Below 65nm, single-event upsets (soft errors) impact field-level product reliability, not only for embedded memories, but for logic and latches as well. (2) Methods for accelerated lifetime testing (burn-in) become infeasible as supply voltages decrease (resulting in exponentially longer burn-in times); even power demands of burn-in ovens become overwhelming. (3) Atomic-scale effects can demand new "soft" defect criteria, such as for non-catastrophic gate oxide breakdown or highly resistive vias. In general, automatic insertion of robustness into the design will become a priority as systems become too large to be functionally tested at manufacturing exit. Potential solutions include automatic introduction of redundant logic and on-chip reconfigurability for fault tolerance, development of adaptive and self-correcting or self-healing circuits, and software-based fault-tolerance.

# **DETAILED DESIGN TECHNOLOGY CHALLENGES**

The remainder of this chapter gives an overview of design methodology, followed by quantified challenges and potential solutions in five main areas of DT. As noted above, most challenges map to SOC, reflecting today's EDA technology and market segmentation.

## **DESIGN METHODOLOGY**

The process of designing and implementing a chip requires a large collection of *techniques*, or *tools*, and an effective *methodology* by which a designer's input predictably leads to a manufacturable product.<sup>3</sup> While considerable attention is given to the tools needed, the equally important subject of design methodology is often neglected. Each technology generation requires designers to consider more issues; hence, new analysis methods and tools must be developed to evaluate new phenomena and aid the designer in making critical design decisions. An even greater challenge is to determine the most effective sequence in which issues should be considered and design decisions made, so as to minimize iterations.

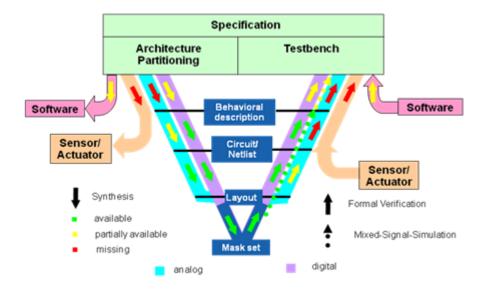

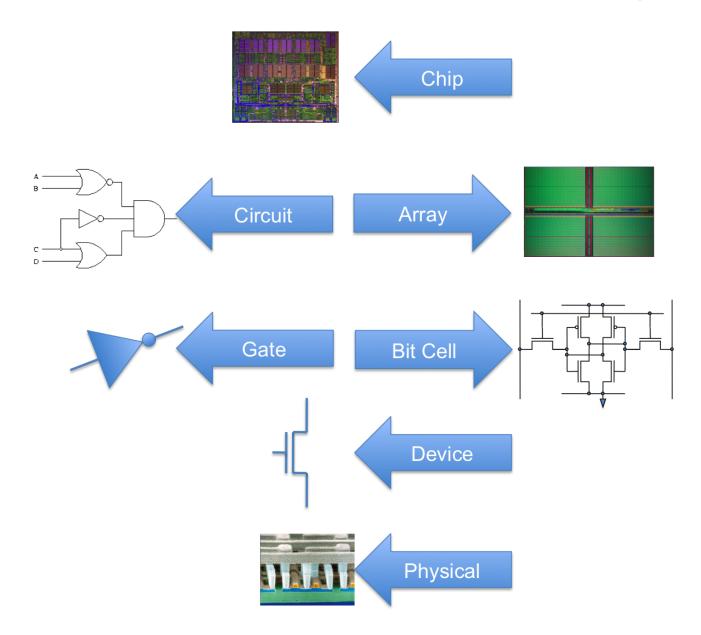

With the transition from microelectronics to nanoelectronics along "More Moore," "More than Moore," and "Beyond CMOS" trajectories come inevitable paradigm shifts in the design of silicon systems. These affect all levels of the design process, and require enormous effort toward new methodologies and tools. DT must enable the creation of highly complex yet cost-efficient silicon system solutions, while exploiting all available opportunities afforded by nanoelectronics. For innovative applications (see the *System Drivers Chapter* for more details) to become affordable, daunting EDA challenges must be overcome. Shrinking of silicon devices and related fabrication processes has been the foundation for ever more powerful integrated silicon solutions that permeate daily life. Delivery of such silicon solutions has relied on the availability of EDA and design technologies that smoothly transform specification data into manufacturing-ready layout data, and perform necessary verifications at different levels of abstraction (see Figure DESN2). However, the continued availability of such design technologies can no longer be taken for granted.

Cost and time-to-market of new SOCs requires DT that spans all parts of a complex design process (Figure DESN2) which consists of two main elements: the implementation path (left) and the verification path (right). The figure shows the so-called V-Cycle of a design system architecture integrating both "More Moore" and "More than Moore" design aspects. The arrows indicate available (green) and partially available (yellow) elements of a state of the art design system environment. Future requirements for EDA are indicated in red.

<sup>&</sup>lt;sup>3</sup> Design methodology is developed jointly by designers and design technologists; it is the sequence of steps by which a design process will reliably produce a design "as close as possible" to the design target while maintaining feasibility with respect to constraints. Design <u>methodology</u> is distinct from design <u>techniques</u>, which pertain to implementation of the steps that comprise a methodology and are discussed in the context of their respective DT areas. All known design methodologies combine 1) enforcement of system specifications and constraints via top-down planning and search, with 2) bottom-up propagation of constraints that stem from physical laws, limits of design and manufacturing technology, and system cost limits.

Figure DESN2 The V-Cycle for Design System Architecture<sup>4</sup>

A system specification undergoes stepwise refinement from architecture down to mask set. The idea of SOC design is to explore the system in initial stages; then, while transforming the system-level description to more detailed levels (behavioral, circuit/netlist, layout and mask), a verification methodology must "guard", i.e., prove correctness of, each incremental refinement step. Beyond the SOC's components and behavior, system software and sensors/actuators must also be handled by future implementation and verification procedures (yellow and red). The digital design path (purple) of the design system will require tools and methodologies above the behavioral abstraction level (yellow). The analog design path is even more challenging (indicated by several red arrows) because complete solutions are rarely found at all level of abstractions. As a result, an automated analog design process (light blue) is still an open challenge in today's design environments. To summarize, future requirements are twofold. 1) More than Moore scaling requires the integration of aspects outside the traditional SOC flow, notably software on the one hand and sensors and actuators on the other, all marked in yellow and red. 2) The future holds new requirements for the SOC design flow, notably tool support for higher abstraction levels in both digital and analog flows. This will entail behavioral synthesis from higher-level specifications on the left side, as well as the corresponding abstract verification steps on the right hand side, all marked in red. The analog and mixed-signal flow additionally requires tools for analog circuit synthesis and automated analog verification on all design levels.

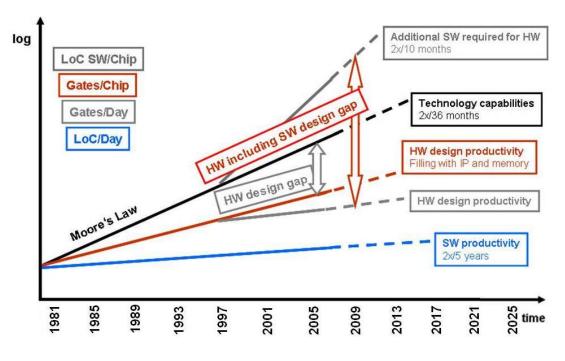

The transition to nanoscale technologies causes all design steps from specification to fabrication to not only become seriously interdependent, but also closely linked to the IC's eventual yield and reliability. Hence, SOC design productivity cannot straightforwardly follow the pace of nanoelectronics technology innovation as it is characterized by Moore's Law (see Figure DESN3). To drastically increase design productivity, an additional level of abstraction – the so-called System Level – has been introduced, with associated system-level challenges and solutions as given in the next section.

## SYSTEM-LEVEL DESIGN

For decades, designers have reasoned about systems at various levels of abstraction (block diagrams, incomplete state charts, program models, etc.) with little support from design automation tools. This situation must change in the near future if necessary advances in productivity are to be achieved. To simplify the specification, verification and implementation of systems including hardware and software, and to enable more efficient design space exploration, a new level of abstraction is needed above the familiar register-transfer level.

<sup>&</sup>lt;sup>4</sup> Elements of this discussion were initially developed as part of a recent update of the Strategic Research Agenda (SRA) within the European Nanoelectronics Initiative Advisory Council (ENIAC) Chapter on Design Automation. Figure DESN2 shows status of the EDA design flow from an automotive point of view, but is general enough to demonstrate the future EDA requirements. The figure was developed by Peter van Staa (Bosch).

Figure DESN3 Hardware and Software Design Gaps versus Time<sup>5</sup>

In system-level design<sup>6</sup>, methodological aspects are rapidly becoming much harder than tools aspects: enormous system complexity can be realized on a single die, but exploiting this potential reliably and cost-effectively will require a roughly  $50\times$  increase in design productivity over what is possible today. Silicon complexities imply that reliable and available systems must be built out of heterogeneous, unreliable device and interconnect components. Global synchronization becomes prohibitively costly due to process variability and power dissipation, and cross-chip signaling can no longer be achieved in a single clock cycle. Thus, system design must comprehend networking and distributed computation metaphors (for example, with communication structures designed first, and functional blocks then integrated into the communication backbone), as well as interactions between functional and interconnect pipelining. System complexities dramatically increase with the amount of software in embedded systems and the rapid adoption of multi-core SOC architectures. Not only is software dominating overall design effort as shown in Figure DESN3, but hardware dependent software that is tightly coupled to hardware and required functionality must be eventually handled by an SOC integration and verification process that is still hardware-centric today.

In this 2011 edition of the ITRS roadmap, the challenges in system-level design remain largely the same as in previous editions, this fact itself being evidence of the enormous complexity of these challenges. For instance, although behavioral synthesis is essential to system-level design, efficient behavioral synthesis is not yet realized today, despite having been a research topic for more than a decade, and despite recent advances driven by C- and SystemC-based synthesis and transaction level modeling (TLM) technologies. Also, while the current SOC design process is still largely "best effort" driven, an inevitable new direction is that of post-silicon self-healing, self-configuration and error correction. DT will play an enabling role in linking application requirements derived from societal and market needs to their eventual cost-

<sup>&</sup>lt;sup>5</sup> This figure shows the demand for software which is currently doubling every 10 months, the capability of technology which is currently doubling every 36 months, as well as the productivity of hardware and software design. Hardware design productivity has been improved in recent years by filling the silicon with multi-core components and memory, thus providing functionality only with additional software; on the other hand, productivity especially for hardware-dependent software is far behind and doubles only every 5 years. The red arrow summarizes the new design gap including both hardware and software. This ITRS version includes therefore for the first time additional figures for illustrating these new software requirements. This material was introduced in the 2007 ITRS edition.

<sup>&</sup>lt;sup>6</sup> At the system level, silicon resources are defined in terms of abstract functions and blocks; design targets include software (embedded code in highlevel and assembly language, configuration data, etc.) and hardware (cores, hardwired circuits, busses, reconfigurable cells). "Hardware" (HW) corresponds to implemented circuit elements, and "software" (SW) corresponds to logical abstractions (instructions) of functions performed by hardware. Behavior and architecture are independent degrees of design freedom, with software and hardware being two components of architecture. The aggregate of behaviors defines the system function, while the aggregate of architecture blocks defines a system platform. Platform mapping from system functionality onto system architecture is at the heart of system-level design, and becomes more difficult with increased system complexity and heterogeneity (whether architectural or functional).

effective system implementation in the "More Moore" and "More than Moore" domains. Table DESN2 gives quantitative requirements for system-level design in future technology generations, including new requirements for the relative impact on power reduction of system-level design versus lower-level design.

Table DESN2a

Near-term System-Level Design Technology Requirements

Table DESN2b Long-term System-Level Design Technology Requirements

Figure DESN4 specifies solutions for system-level design in their corresponding time frames, and Table DESN3 explains how requirements correspond to solutions.

| First Year of IC Production                              | 2011 | 2012 | 2013 | 2014 | 2015 | 2016 | 2017 | 2018 | 2019 | 2020 | 2021 | 2022 | 2023 | 2024 | 2025 | 2026 |

|----------------------------------------------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| System-level component reuse                             |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Chip-package co-design<br>methods                        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Improved system-level power<br>estimation techniques     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| On-chip network design<br>methods                        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Mixed-Signal/RF verification                             |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Automated interface synthesis                            |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| HW-SW co-design and<br>verification                      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Multi-fabric implementation<br>planning (AMS, RF, MEMs,) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Parallel processing                                      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Intelligent testbench                                    |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Concurrent SW infrastructure                             |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Heterogeneous parallel<br>processing                     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Transactional memory                                     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| System design automation (SDA)                           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Executable specification                                 |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

This legend indicates the time during which research, development, and qualification/pre-production should be taking place for the solution.

Research Required Development Underway Qualification / Pre-Production Continuous Improvement

Figure DESN4 System-Level Design Potential Solutions

| Table DESN3 | Correspondence betw | een System-Level Design | Requirements and Solutions |

|-------------|---------------------|-------------------------|----------------------------|

|-------------|---------------------|-------------------------|----------------------------|

| Requirement                                                                           | Solution                                              | Explanation of the Correspondence                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design block reuse                                                                    | System-level component reuse                          | The larger and more complex the components that can be reused,<br>the greater the expected overall design reuse                                                                                                                                                                                                                                        |

|                                                                                       | On-chip network design methods                        | Standardized communication structures and interfaces support<br>reuse: IPs with standardized interfaces can be easily integrated and<br>exchanged, and communication structures reused                                                                                                                                                                 |

| Available platforms                                                                   | Multi-fabric implementation planning (AMS, RF, MEMS,) | Enables integration of different fabrics on same die or in same<br>package (SIP); hence, enables reduced number of platforms                                                                                                                                                                                                                           |

| Platforms supported                                                                   | Automated interface synthesis                         | Automated interface synthesis is one building block to an integrated synthesis flow for whole platforms                                                                                                                                                                                                                                                |

|                                                                                       | Automated HW-SW codesign and verification             | Required for integrated, platform-based system development                                                                                                                                                                                                                                                                                             |

| Accuracy of high level estimates                                                      | Improved system-level power estimation techniques     | System-level power estimation needs to match progress in high-<br>level area and performance estimation                                                                                                                                                                                                                                                |

|                                                                                       | Chip-package codesign methods                         | Packaging effects, e.g., on timing, must be accounted for in higher-<br>level estimations                                                                                                                                                                                                                                                              |

| SOC reconfigurability                                                                 | On-chip network design methods                        | To provide flexible, reconfigurable communication structures                                                                                                                                                                                                                                                                                           |

| Analog automation                                                                     | Multi-fabric implementation planning (AMS, RF, MEMS,) | Multi-fabric implementation planning for AMS and RF components are a building block to analog automation                                                                                                                                                                                                                                               |

| Modeling methodology, description<br>languages, simulation environments               | Mixed-Signal/RF verification                          | As in digital design, verification is an increasingly critical and<br>time-consuming activity in the design flow                                                                                                                                                                                                                                       |

| HW offers multi-core systems that<br>have to be exploited by SW                       | Parallel Processing                                   | Due to thermal and power limitations further performance increases have to be realized with multi-core systems.                                                                                                                                                                                                                                        |

| Reduce SW verification effort                                                         | Intelligent Testbench                                 | SW simulation, formal verification and automated testbenches for<br>SW will reduce the verification effort for embedded software and<br>enhance quality                                                                                                                                                                                                |

| Productivity increase required for SW<br>since SW cost >> 50% of total system<br>cost | Concurrent Software Infrastructure                    | A set of tools that allow concurrent software development and debug                                                                                                                                                                                                                                                                                    |

| Increase SW execution performance                                                     | Heterogeneous Parallel Processing                     | Parallel processing using different application-specific processors<br>for each of the separate functions in the system                                                                                                                                                                                                                                |

| SW Productivity increase required                                                     | Transactional Memory                                  | A concurrency control mechanism analogous to database<br>transactions for controlling access to shared memory in concurrent<br>computing; an alternative to lock-based synchronization                                                                                                                                                                 |

| Productivity increase required for<br>HW/SW codesign                                  | System Design Automation (SDA)                        | True system-level design including electronic hardware and software, mechanical, bio, opto, chemical and fluids domains                                                                                                                                                                                                                                |

| Reduce verification effort                                                            | Executable Specification                              | Specifications written in a formal language allow automated<br>verification process starting early in the design process and at high<br>abstraction levels without the need to code several new verification<br>models; this enables an integrated design flow from specification to<br>completed system that can be completely validated at each step |

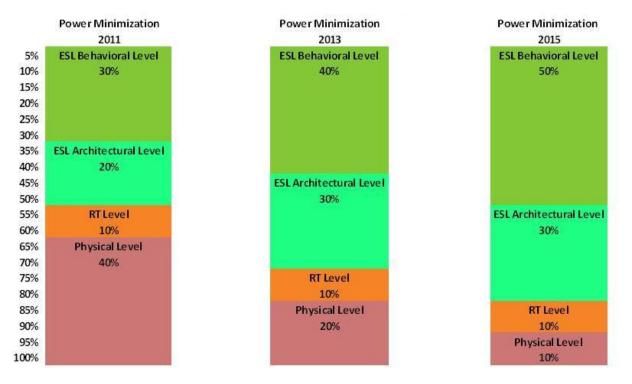

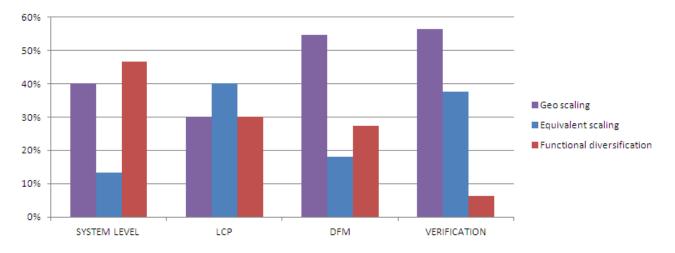

Figure DESN5 gives a roadmap for the increasing role of system-level design in achieving required system power minimization. In the figure, percentage values indicate the fraction of power reduction (measured in watts or microwatts) that must be borne by the given phases of system design in future technology nodes. This trend is also reflected in the new Appendix III: DT-Based Reductions of Power Consumption, where most of the innovations are related to behavioral and architecture levels.

Figure DESN5 Evolving Role of Design Phases in Overall System Power Minimization

## LOGICAL, CIRCUIT AND PHYSICAL DESIGN

In the traditional view of IC implementation, *logical design* is the process of mapping from the system-level design handoff (currently at the register-transfer level) to a gate-level representation that is suitable for input to physical design. *Circuit design* addresses creation of device and interconnect topologies (standard cells, full-custom analog, etc.) that achieve prescribed electrical and physical properties while remaining feasible with respect to process- and manufacturability-induced constraints. *Physical design* addresses aspects of chip implementation (floorplanning, placement, routing, extraction, performance analysis) related to the correct spatial embedding of devices and interconnects. The output of physical design is the handoff ("tapeout") to manufacturing (currently centered around a generalized data stream (GDSII) file), along with verifications of correctness (design rules, layout versus schematic, etc.) and constraints (timing, power, reliability, etc.). Together, logical, circuit and physical design comprise the *implementation* layer of DT that supports system-level design.

Design productivity requires system-level signoff into reliable, predictable implementation fabrics. However, silicon complexity makes it difficult to estimate and abstract the effects of physics and embedding on eventual design quality (timing, power, signal integrity, reliability, manufacturability, etc.). To avoid excessive guardbanding due to poor estimates, logical design and eventually system-level design must become more closely linked with physical design. Thus, the recent paradigm of hierarchical, top-down, layout-based implementation planning supported by a tightly integrated, incremental static (power, timing, noise) analysis "backplane" is likely to persist. Future successful implementation DT will depend heavily on methodology choices to juggle process/device abstraction, constraint manipulation, analyses, and optimizations in the face of exploding complexities and emerging concerns such as error-tolerance, variability and cost.

Current hardware design automation practices must evolve to handle the challenges and opportunities of finer-featured fabrication processes. Methodologies premised on the principle of separation of concerns – in which a complex design flow is serialized into a sequence of loosely-coupled, manageable steps – are growing long in the tooth. To the extent that decisions made in early stages of the design flow become binding constraints on later stages, such serialization potentially yields less-optimal designs than a methodology that simultaneously considers and co-optimizes all design aspects. Due to the practical difficulty of concurrent optimization of all design parameters, such serialization is deemed acceptable as

long as the constraints that are fed forward can be met. The methodology breaks down, however, when these constraints become infeasible; the typical action in such cases is to iterate, revisiting earlier design stages to identify and change problematic decisions. Such iteration has become particularly necessary between the logical and physical synthesis steps due to the inability of layout synthesis to satisfy timing requirements, that is, achieve timing closure. (Closure with respect to manufacturability and robustness checks is another looming source of expensive iterations.) Ideally, the time-wasting iteration between logic and layout synthesis (or, between layout synthesis and manufacturability verification) in today's design methodologies could be eliminated by fusing such stages – e.g., to simultaneously optimize the logical and layout structure of a circuit. But, as technology scales and previously ignorable physical or statistical effects become more significant, such optimizations are less effective due to growing inaccuracy of optimization targets or objective functions. Such inaccuracies may lead to timing-related and electrical problems that may not be apparent until masks are produced. To correct such problems, new engineering change order (ECO) techniques that work on the post-synthesis masks may be needed.

#### LOGICAL, CIRCUIT, AND PHYSICAL DESIGN REQUIREMENTS

Each technology requirement for logical, circuit and physical design is either a workaround that addresses effects of a given technology (i.e., a *control requirement*), or a desired capability for a given time frame and technology (i.e., an *objective requirement*). Table DESN4 gives numerical targets for each requirement.

## Table DESN4 Logical/Circuit/Physical Design Technology Requirements

Explanations of the technology requirements are as follows.