# INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS

# 2013 Edition

# METROLOGY

THE ITRS IS DEVISED AND INTENDED FOR TECHNOLOGY ASSESSMENT ONLY AND IS WITHOUT REGARD TO ANY COMMERCIAL CONSIDERATIONS PERTAINING TO INDIVIDUAL PRODUCTS OR EQUIPMENT.

## **Table of Contents**

| Me | trolog | у                                                              | 1    |

|----|--------|----------------------------------------------------------------|------|

| 1. | . In   | troduction and Scope                                           | 1    |

|    | 1.1.   | Introduction                                                   |      |

|    | 1.2.   | Scope                                                          |      |

|    | 1.3.   | Infrastructure Needs                                           | 3    |

| 2. | . Di   | fficult Challenges                                             | 3    |

|    | 2.1.   | Difficult Challenges                                           | 3    |

| 3. | . M    | icroscopy                                                      | 5    |

| 4  | . Lit  | hography Metrology                                             | 6    |

|    | 4.1.   | Line Roughness                                                 | 8    |

|    | 4.2.   | Measurement Uncertainty                                        | 9    |

|    | 4.3.   | Explanation Of Uncertainty In Table Met3                       | .11  |

| 5  | . Fr   | ont End Processes Metrology                                    | .13  |

|    | 5.1.   | Starting Materials                                             | .13  |

|    | 5.2.   | Surface Preparation                                            | .13  |

|    | 5.3.   | Thermal/thin films                                             | .14  |

|    | 5.4.   | Strained Si Processes                                          | .14  |

|    | 5.5.   | FERAM                                                          | .15  |

|    | 5.6.   | Doping Technology                                              | .16  |

| 6  | . 30   | D Interconnect Metrology                                       | .18  |

|    | 6.1.   | Bonding Overlay                                                | .18  |

|    | 6.2.   | Bonded Interface Void Detection                                | .19  |

|    | 6.3.   | Bonded Interface Defect Identification                         | .19  |

|    | 6.4.   | Bonded Interface Defect Review                                 | .19  |

|    | 6.5.   | Edge Bevel Defects                                             | .19  |

|    | 6.6.   | Bond Strength Uniformity                                       |      |

|    | 6.7.   | Bonded Wafer Pair Thickness                                    |      |

|    | 6.8.   | TSV Etch Depth                                                 | .20  |

|    | 6.9.   | TSV Etch Profile                                               | .20  |

|    | 6.10.  | TSV Liner, Barrier, Seed Thickness                             |      |

|    | 6.11.  | TSV Voids                                                      | .21  |

|    | 6.12.  | Shape and Stress                                               |      |

|    | 6.13.  | 3D Metrology for Copper nail and Pillars                       | .21  |

| 7. | . In   | terconnect Metrology                                           |      |

|    | 7.1.   | CU-LOW K Metallization Issues and Metrology Needs              | .22  |

|    | 7.2.   | Low κ Dielectrics Issues and Metrology Needs                   | .23  |

| 8. |        | aterials And Contamination Characterization                    |      |

|    | 8.1.   | Materials and Contamination in Strain-Based Devices            | .27  |

| 9. | . M    | etrology for Emerging Research Materials and Devices           | .29  |

|    | 9.1.   | Update on Advances in Graphene Metrology                       | .29  |

|    | 9.2.   | Update on Advances in Memristor Metrology                      | .30  |

|    | 9.3.   | Comment on the Impact of Nanoscale Dimensions on Metrology     |      |

|    | 9.4.   | 3D Atomic Imaging and Spectroscopy                             |      |

|    | 9.5.   | Other Microscopy Needs including Scanning Probe Microscopy     |      |

|    | 9.6.   | Optical Properties of Nanomaterials                            |      |

|    | 9.7.   | Electrical Characterization for Emerging Materials and Devices | . 32 |

| 10 | 0.     | Reference Materials                                            | .33  |

| 11.   | 3D Nanometrology Needs and Challenges           | . 34 |

|-------|-------------------------------------------------|------|

|       | 3D Nanoscale Characterisation of Single Devices |      |

| 11.2. | Trends in Nanoscale Tomography                  | 35   |

| 11.3. | Combined Metrology                              | 36   |

|       | In-Lab. versus In-Fab                           |      |

| 12.   | Reference Measurement System                    | . 37 |

| 13.   | References                                      | . 38 |

## List of Figures

| Figure MET1 | Lithography Metrology Potential Solutions   | 12 |

|-------------|---------------------------------------------|----|

| Figure MET2 | Review of Stress/Strain Measurement Methods | 15 |

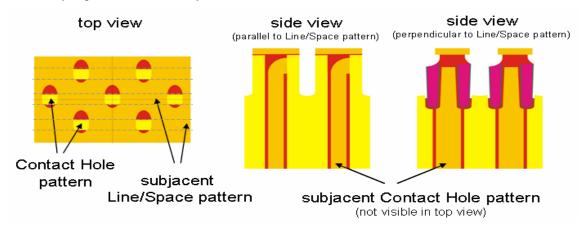

| Figure MET3 | 3D Metrology Requirements                   | 15 |

| Figure MET4 | FEP Metrology Potential Solutions           | 17 |

| Figure MET5 | Interconnect Metrology Potential Solutions  | 25 |

## List of Tables

| Table MET1 | Metrology Difficult Challenges                        | . 4 |

|------------|-------------------------------------------------------|-----|

| Table MET2 | Metrology Technology Requirements                     | . 5 |

| Table MET3 | Lithography Metrology (Wafer) Technology Requirements | 11  |

| Table MET4 | ITRS 3D Interconnect TSV Roadmap                      | 18  |

# METROLOGY

## **1. INTRODUCTION AND SCOPE**

#### **1.1.INTRODUCTION**

Metrology is defined as the science of measurement. The ITRS Metrology Roadmap describes new challenges facing metrology and describes a pathway for research and development of metrology with the goal of extending CMOS and accelerating Beyond CMOS. Metrology also provides the measurement capability necessary for cost-effective manufacturing. As such, the metrology chapter of the ITRS focuses on difficult measurement needs, metrology tool development, and standards.

Over the past ten years, device and integrated circuit technology has rapidly evolved toward the use of complex 3D structures fabricated using new materials and processes with ever decreasing dimensions. The 3D nanoscale nature of these structures provides considerable challenges for all areas of metrology. Several examples of new process technology help describe the new challenges facing metrology. Research into new patterning processes covers the use of directed self-assembly of block copolymers, extreme UV lithography, and 3X and 4X multiple patterning. All of these methods result in different challenges for measurement of critical dimensions (CD), overlay, and defectivity. FinFET transistors are now the dominant microprocessor device architecture, and the challenges facing Front End Processes metrology are control of the fabrication processes for memory structures which are among the most complex 3D device structures. On-chip and off-chip interconnect materials continue to evolve and interconnect metrology challenges continues to include process control for 3D interconnect. Research into a replacement for copper interconnect is an example of a new material that could change metrology methods for interconnect. Some new devices described in previous Emerging Research Devices roadmaps have moved closer to acceptance as new device structures are discovered and evaluated. The metrology challenges found in Emerging Research Materials include characterization of 2D materials such as graphene and other new materials as well as electrical characterization at the nano-level.

The roadmap for feature size reduction drives the timeline for metrology solutions for new materials, process, and structures. Metrology methods must routinely measure near and at atomic scale dimensions which require a thorough understanding of nano-scale materials properties and of the physics involved in making the measurement. Metrology development must be done in the context of these issues. Metrology enables tool improvement, ramping in pilot lines and factory start-ups, and improvement of yield in mature factories. Metrology can reduce the cost of manufacturing and the time-to-market for new products through better characterization of process tools and processes. The increasing diversity of chip types will spread already limited metrology resources over a wider range of challenges. The metrology community including suppliers, chip manufacturers, consortia, and research institutions must provide cooperative research, development, and prototyping in order to meet the ITRS timeline. The lack of certainty in the structures and materials of future technology generations makes the definition of future metrology needs less clear than in the past.

Moreover, it is entirely possible that different materials will be used by different manufacturers at a given technology generation, potentially requiring different metrologies. In the near term, advances in electrical and physical metrology for high- and low- $\kappa$  dielectric films must continue. The strong interest in extreme ultra violet (EUV) Lithography is driving the need for new mask metrology. The requirement for technology for measurement of devices on ultra-thin and possibly strained silicon on insulator comes from the best available information that is discussed in the *Front End Processes* Roadmap. The increasing emphasis on active area measurements instead of test structures in scribe (kerf) lines places new demands on metrology. Measurement of relevant properties, such as stress or strain, in a nano-sized, buried area such as the channel of a small dimension gate is a difficult task. Often, one must measure a film or structure property at the surface and use modeling to determine the resultant property of a buried layer. Long-term needs at the sub-12 nm technology generation are difficult to address due to the lack of clarity of device design and interconnect technology. The selection of a replacement for copper interconnect remains a research challenge. Although materials characterization and some existing inline metrology apply to new device and interconnect structures, development of manufacturing capable metrology requires a more certain knowledge of materials, devices, and interconnect structures. The 2013 ITRS also includes the addition of a MEMS chapter.

Metrology tool development requires access to new materials and structures if it is to be successful. It requires state-ofthe-art capabilities to be made available for fabrication of necessary standards and development of metrology methodologies in advance of production. The pace of feature size reduction and the introduction of new materials and structures challenge existing measurement capability. In some instances, existing methods can be extended for several technology generations. In other cases, necessary measurements may be done with inadequate equipment. Long-term research into nano-devices may provide both new measurement methods and potential test vehicles for metrology. A greater attention to expanding close ties between metrology development and process development is needed. When the metrology is well matched to the processes and process tools, ramping times for pilot lines and factories are reduced. An appropriate combination of well-engineered tools and appropriate metrology is necessary to maximize productivity while maintaining acceptable cost of ownership.

The fundamental challenge for factory metrology will be the measurement and control of atomic dimensions while maintaining profitable high volume manufacturing. In manufacturing, metrology is connected to factory-wide automation that includes database and intelligent information from data capability. Off-line materials characterization is also evolving toward compatibility with factory-wide automation. All areas of measurement technology (especially those covered in the *Yield Enhancement chapter*) are being combined with computer integrated manufacturing (CIM) and data management systems for information-based process control. Although integrated metrology still needs a universal definition, it has become the term associated with the slow migration from offline to inline and *in situ* measurements. The proper combination of offline, inline, and *in situ* measurements will enable advanced process control and rapid yield learning.

The expected trend involves the combined use of modeling with measurement of features at the wafer surface. *The Metrology roadmap has repeated the call for a proactive research, development, and supplier base for many years.* The relationship between metrology and process technology development needs fundamental restructuring. In the past the challenge has been to develop metrology ahead of target process technology. Today we face major uncertainty from unresolved choices of fundamentally new materials and radically different device designs. *Understanding the interaction between metrology data and information and optimum feed-back, feed forward, and real-time process control are key to restructuring the relationship between metrology and process technology.* A new section has been added to the Metrology Roadmap that covers metrology needs for 3D Nanometrology.

#### **1.2. SCOPE**

The metrology topics covered in the 2013 *Metrology* roadmap are microscopy; critical dimension (CD) and overlay; film thickness and profile; materials and contamination analysis; 3D metrology; emerging research materials and devices; and reference materials. These topics are reported in the following sections in this chapter: Microscopy; Lithography Metrology; Front End Processes Metrology; 3D Interconnect Metrology; Traditional Interconnect Metrology; Materials and Contamination Characterization; Metrology for Emerging Research Materials Devices; Reference Materials; 3D nanometrology needs and challenges; and Reference Measurement Systems.

International cooperation in the development of new metrology technology and standards will be required. Both metrology and process research and development organizations must work together with the industry including both the supplier and IC manufacturer. Earlier cooperation between IC manufacturers and metrology suppliers will provide technology roadmaps that maximize the effectiveness of measurement equipment. Research institutes focusing on metrology, process, and standards; standards organizations; metrology tool suppliers; and the university community should continue to cooperate on standardization and improvement of methods and on production of reference materials. Despite the existence of standardized definitions and procedures for metrics, individualized implementation of metrics such as measurement precision to tolerance (P/T) ratio is typical. The P/T ratio is used to evaluate automated measurement capability for use in statistical process control and relates the measurement variation (precision) of the metrology cluster to the product specification limits. Determination of measurement tool variations is sometimes carried out using reference materials that are not representative of the product or process of interest. Thus, the measurement tool precision information may not reflect measurement-tool induced variations on product wafers. It is also possible that the sensitivity of the instrument could be insufficient to detect small but unacceptable process variations. There is a need for metrics that accurately describe the resolution capability of metrology tools for use in statistical process control. The inverse of the measurement precision-to-process variability is sometimes called the signal-to-noise ratio or the discrimination ratio. However, because the type of resolution depends on the process, specific metrics may be required (e.g. thickness and width require spatial resolution while levels of metallic contaminants on the surface require atomic percent resolution). There is a new need for a standardized approach to determination of precision when the metrology tool provides discrete instead of continuous data. This situation occurs, for example, when significant differences are smaller than the instrument resolution.

The principles of integrated metrology can be applied to stand-alone and sensor-based metrology itself. Factors that impact tool calibration and measurement precision such as small changes in ambient temperature and humidity could be monitored and used to improve metrology tool performance and thus improve statistical process control.

Wafer manufacturers, process tool suppliers, pilot lines, and factory start-ups all have different timing and measurement requirements. The need for a shorter ramp-up time for pilot lines means that characterization of tools and processes prior to pilot line startup must improve. However, as the process matures, the need for metrology should decrease. As device dimensions shrink, the challenge for physical metrology will be to keep pace with inline electrical testing that provides critical electrical performance data.

#### **1.3. INFRASTRUCTURE NEEDS**

A healthy industry infrastructure is required if suppliers are to provide cost-effective metrology tools, sensors, controllers, and reference materials. New research and development will be required if opportunities such as MEMS-based metrology and nanotechnology are to make the transition from R&D to commercialized products. Many metrology suppliers are small companies that find the cost of providing new tools for leading-edge activities prohibitive. Initial sales of metrology tools are to tool and process developers. Sustained, high-volume sales of the same metrology equipment to chip manufacturers do not occur until several years later. The present infrastructure cannot support this delayed return on investment. Funding that meets the investment requirements of the supplier community is needed to take new technology from proof of concept to prototype systems and finally to volume sales.

## 2. DIFFICULT CHALLENGES

Metrology requirements continue to be driven by advanced lithography processes, new materials, and Beyond CMOS materials, structures, and devices. The push for EUV Lithography is driving the development of new metrology equipment for masks. Existing CD metrology is approaching its limits and requires significant advances to keep pace with the needs of patterning. Another key challenge to CD metrology is tool matching. Near term precision (measurement uncertainty) requirements for the next few years can be met using single tools. Overlay metrology capability lags behind the need for improved overlay control. Front end processes continue to drive metrology to provide measurements for new channel materials including III-V film stacks, higher dielectric constant materials, dual work function metal gates, and new ultra shallow junction doping processes. 3D device structures such as FinFETs place significantly more difficult requirements on dimensional and doping metrology. The need for porosity control for low k materials has driven a renewed interest in porosity measurements. 3D interconnect metrology requirements are largely driven by the activity in through silicon vias (TSV) R&D. Bonded wafer overlay control for next generation. Potential solutions for bonded wafer overlay are now available. For Beyond CMOS R&D, many areas of graphene metrology have advanced but putting them into volume manufacturing will require challenging R&D. The need for understanding large area graphene uniformity is driving both physical and electrical metrology. In addition, metrology R&D is working with other Beyond CMOS materials.

#### 2.1. DIFFICULT CHALLENGES

Many short-term metrology challenges listed below will continue beyond the 12 nm ½ pitch Metrology needs after 2019 will be affected by unknown new materials and processes. Thus, it is difficult to identify all future metrology needs. Shrinking feature sizes, tighter control of device electrical parameters, such as threshold voltage and leakage current, and new interconnect technology such as 3D interconnect will provide the main challenges for physical metrology methods. To achieve desired device scaling, metrology tools must be capable of measurement of properties on atomic distances. Table MET1 presents the ten major challenges for metrology. Table MET2 presents the technology requirements for Metrology.

| Table MET1                                                                                                                                                                                                                                                                                                                     | Metrology Difficult Challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Difficult Challenges $\geq 12 \text{ nm}$                                                                                                                                                                                                                                                                                      | Summary of Issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Factory level and company wide metrology integration<br>for real-time <i>in situ</i> , integrated, and inline metrology<br>tools; continued development of robust sensors and<br>process controllers; and data management that allows<br>integration of add-on sensors. Reduction of scrap,<br>product quality and cycle time. | Standards for process controllers and data management must be agreed upon.<br>Conversion of massive quantities of raw data to information useful for enhancing the yield<br>of a semiconductor manufacturing process. Better sensors must be developed for trench<br>etch end point, and ion species/energy/dosage (current). Augmenting existing metrology<br>with virtual metrology to support emerging capabilities such as smart metrology<br>(predicting when and how much to measure), movement to more granular control (lot<br>based to wafer based), and reduce scrap through prediction of quality for every wafer.<br>Standards are needed to support the quality of the data for virtual metrology. |

| Starting materials metrology and manufacturing<br>metrology are impacted by the introduction of new<br>substrates based on SOI, III-V, GeOI, etc. Impurity<br>detection (especially particles) at levels of interest for<br>starting materials and reduced edge exclusion for<br>metrology tools.                              | Existing capabilities will not meet Roadmap specifications. Very small particles must be detected and properly sized. Capability for SOI, III-V, GeOI wafers needs enhancement. Challenges come from the extra optical reflection in SOI and the surface quality. CD, film thickness, and defect detection are impacted by thin SOI optical properties and charging by electron and ion beams.                                                                                                                                                                                                                                                                                                                  |

| Control of new process technology such as Directed Self<br>Assembly Lithography, complicated 3D structures such<br>as FinFET & MuGFET transistors, capacitors and<br>contacts for memory, and 3D Interconnect are not ready<br>for their rapid introduction.                                                                   | Although there have been significant advances in off-line characterization of FinFET structures, the recent announcement that a FinFET transistor will be used in manufacturing at the 12 nm 1/2 pitch has placed renewed emphasis on the near term need for in-line metrology for dimensional, compositional, and doping measurements. The materials properties of block co-polymers result in new challenges for lithography metrology. 3D Interconnect comprises a number of different approaches. New process control needs are not yet established. For example, 3D (critical dimension (CD) and depth) measurements will be required for trench structures including capacitors, devices, and contacts.   |

| Measurement of complex material stacks and interfacial<br>properties including physical and electrical properties.                                                                                                                                                                                                             | Reference materials and standard measurement methodology for new high- $\kappa$ gate and capacitor dielectrics with engineered thin films and interface layers as well as interconnect barrier and low- $\kappa$ dielectric layers, and other process needs. Optical measurement of gate and capacitor dielectric averages over too large an area and needs to characterize interfacial layers. Carrier mobility characterization will be needed for stacks with strained silicon and SOI, III-V, GeOI, and other substrates, or for measurement of barrier layers. Metal gate work function characterization is another pressing need.                                                                         |

| Measurement test structures and reference materials.                                                                                                                                                                                                                                                                           | The area available for test structures is being reduced, especially in the scribe lines.<br>Measurements on test structures located in scribe lines may not correlate with in-die<br>performance. Overlay and other test structures are sensitive to process variation, and test<br>structure design must be improved to ensure correlation between measurements in the<br>scribe line and on chip properties. Standards institutions need rapid access to state of the art<br>development and manufacturing capability to fabricate relevant reference materials.                                                                                                                                              |

| Difficult Challenges < 12 nm                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Nondestructive, production worthy wafer and mask-level<br>metrology for CD measurement for 3D structures,<br>overlay, defect detection, and analysis                                                                                                                                                                           | Surface charging and contamination interfere with electron beam imaging. CD measurements must account for overall feature profile. It is important to have both imaging and scattering techniques available for any given process control situation. Focus, exposure, and etch bias control will require better precision and 3D capability.                                                                                                                                                                                                                                                                                                                                                                    |

| New strategy for in-die metrology must reflect across chip and across wafer variation.                                                                                                                                                                                                                                         | Correlation of test structure variations with in-die properties is becoming more difficult<br>as devices shrink. Sampling plan optimization is key to solving these issues.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Statistical limits of sub-12 nm process control                                                                                                                                                                                                                                                                                | Controlling processes where the natural stochastic variation limits metrology will be difficult. Examples are low-dose implant, thin-gate dielectrics, surface, sidewall and edge roughness of very small structures. Complementary, and hybrid metrology combined with state of the art statistical analyses would be required to reduce the measurement uncertainty.                                                                                                                                                                                                                                                                                                                                          |

| Structural and elemental analysis at device dimensions<br>and measurements for <i>beyond CMOS, and emerging</i><br><i>materials and devices.</i>                                                                                                                                                                               | Materials characterization and metrology methods are needed for control of interfacial layers, dopant positions, defects, and atomic concentrations relative to device dimensions. One example is 3D dopant profiling. Measurements for self-assembling processes are also required.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Determination of manufacturing metrology when device<br>and interconnect technology remain undefined.                                                                                                                                                                                                                          | The replacement devices for the transistor and structure and materials replacement for<br>copper interconnect are being researched.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Directed Self Assembly (DSA)                                                                                                                                                                                                                                                                                                   | Key measurands such as size, location, and alignment need to be better defined. Some<br>of the measurands are also material and system dependent. Many of the materials are<br>similar enough that identifying a property with the required contrast may be difficult. A<br>key question seems to be if we can detect low densities of surface and buried defects.                                                                                                                                                                                                                                                                                                                                              |

| Mask Defects                                                                                                                                                                                                                                                                                                                   | Mask defects, especially for EUV will continue to be a challenge. These include non-<br>visible defects, film thickness non-uniformity, phase separation, and reflectivity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## Table MET1 Metrology Difficult Challenges

#### Table MET2Metrology Technology Requirements

### 3. MICROSCOPY

Microscopy is used in most of the core technology processes where two-dimensional distributions, that is digital images of the shape and appearance of integrated circuit (IC) features, reveal important information. Usually, imaging is the first, but many times the only step in the "being able to see it, measure it, and control it" chain. Microscopes typically employ light, electron beam, or scanned probe methods. Beyond imaging, online microscopy applications include CD and overlay measurements along with detection, review, and automatic classification of defects and particles. Because of the high value and quantity of wafers, the need for rapid, non-destructive, inline imaging and measurement is growing. Due to the changing aspect ratios of IC features, besides the traditional lateral feature size (for example, linewidth measurement) full three-dimensional shape measurements are gaining importance and should be available inline. Development of new metrology methods that use and take the full advantage of advanced digital image processing and analysis techniques, telepresence, and networked measurement based on these methods must serve the technologists better, giving fast detailed, adequate information on the processes in ways that help to establish process control in a more automated manner.

*Electron Microscopy*—There are many different microscopy methods that use electron beams as sources of illumination. These include scanning electron microscopy, transmission electron microscopy, scanning transmission electron microscopy, electron holography, and low-energy electron microscopy. Scanning electron microscopy and electron holography are discussed below, and transmission electron microscopy, scanning transmission electron microscopy, and low-energy electron microscopy, scanning transmission electron microscopy, and low-energy electron microscopy are discussed in the section on Materials and Contamination Characterization.

Scanning Electron Microscopy (SEM)—continues to provide at-line and inline imaging for characterization of crosssectional samples, particle and defect analysis, inline defect imaging (defect review), and CD measurements. Improvements are needed for effective CD and defect review (and SEM detection in pilot lines) at or beyond the 22 nm generation. New inline SEM technology, such as the use of ultra-low-energy electron beams (< 250 eV) and high energy SEM (10keV-200keV) may be required for overcoming image degradation due to charging, contamination, and radiation damage of the sample surface, while maintaining adequate resolution and depth of field. Improving the resolution of the SEM by the reduction of spherical aberration leads to an unacceptably small depth of field and SEM imaging with several focus steps and/or use of algorithms that take the beam shape into account might be needed. Aberration correction lens technology has migrated from transmission electron microscopy to SEM providing a significant increase in capability. Other non-traditional SEM imaging techniques, such as the implementation of nano-tips and electron holography, need further development to be production-worthy methodologies. A new alternative path could be high-pressure or environmental microscopy, which opens the possibility for higher accelerating voltage, high-resolution imaging, and metrology. Binary and phase-shifting chromium-on-quartz optical photomasks have been successfully investigated with this mode of high-resolution scanning electron microscopy. It has been found that the gaseous sample environment minimizes sample charging and contamination. This methodology also holds promise for the inspection, imaging, and metrology of wafers.

Data analysis methods that adhere to the physics of the measurement and use all information collected, have been demonstrated to be better than arbitrary methods. Measured and modeled image and fast and accurate comparative techniques are likely to gain importance in SEM dimensional metrology. A better understanding of the relationship between the physical object and the waveform analyzed by the instrument is expected to improve CD measurement. Sample damage, which arises from direct ionization damage of the sample and deposition of charge in gate structures, may set fundamental limits on the utility of all microscopies relying on charged particle beams. Shrinkage, another form of damage often caused by electron beams on polymer layers, including photoresists, is now better understood and in many cases can now be predicted and compensated for in CD measurement values.<sup>1</sup>

Determination of the real 3D shape for sub-90 nm contacts/vias, transistor gates, interconnect lines, or damascene trenches will require continuing advances in existing microscopy and sample preparation methods. Fully automated cross-sectioning by FIB and semi-automated lift-out for imaging in a TEM or a STEM has been successfully demonstrated.

*He Ion Microscopy (HIM)*—has been proposed as a means of overcoming the issues associated with the spread in effect probe size due to the interaction of finely focused electron beams and the sample. Potential applications of this technology include CD, defect review, and nanotechnology. Sub-1nm resolution by HIM has been achieved, but sample interaction

questions are as yet unanswered. For IC manufacturing metrology, current thoughts are that HIM needs to be able to fill a key gap, the imaging of high aspect ratio etched contact holes and trenches without causing too much damage, to secure its place as an in-line workhorse wafer metrology solution.

*Scanning Probe Microscopy (SPM)*—may be used to calibrate CD-SEM measurements. Scanning probe microscopes, such as the atomic force microscope (AFM), offer 3D measurements that are insensitive to the material scanned. Flexing of the probe degrades measurements when the probe is too slender. The probe shape and aspect ratio must, therefore, be appropriate for the probe material used and the forces encountered. High stiffness probe materials, such as short carbon nano-tubes, may alleviate this problem. Other types of scanning probe microscopy are discussed in the metrology for Emerging Research Materials and Devices section.

*Far-field Optical Microscopy*—is limited by the wavelength of light. Deep ultraviolet sources and near-field microscopy arebeing developed to overcome these limitations. Improved software allowing automatic classification of defects isneeded. Optical microscopes will continue to have application in the inspection of large features, such as solder bump arrays for multi-chip modules. Also, other new experimental optical applications that move beyond direct measurement from images have the potential to detect smaller features either for measurements or for process excursion flagging, but more work is needed to understand if they have a place for in-line metrology.<sup>2,3</sup>

For *defect detection*—each technology has limitations. A defect is defined as any physical, electrical, or parametric deviation capable of affecting yield. Existing SEMs and SPMs are considered too slow for the efficient detection of defects too small for optical microscopes. High-speed scanning has been demonstrated with arrayed SPMs, (that might be faster than SEMs) but issues associated with probe lifetime, uniformity, characterization, and wear need to be addressed. This technology should be pursued both by expanding the size of the array and in developing additional operational modes. Arrayed micro-column SEMs have been proposed as a method of improving SEM throughput and operation of a single micro-SEM has been demonstrated. Research is needed into the limits of electrostatic and magnetic lens designs.

## 4. LITHOGRAPHY METROLOGY

Lithography metrology continues to be challenged by rapid advancement of patterning technology. New materials in all process areas add to the challenges faced by Lithography metrology. A proper control of the variation in transistor gate length starts with mask metrology. Although the overall features on a mask are four times larger than as printed, phase shift and optical proximity correction features are roughly half the size of the printed structures. Indeed, larger values for mask error factor (MEF) might require a tighter process control at mask level, too; hence, a more accurate and precise metrology has to be developed. Mask metrology includes measurements that determine that the phase of the light correctly printed. Both on-wafer measurement of CD and overlay are also becoming more challenging. CD control for transistor gate length continues to be a critical part of manufacturing ICs with increasing clock speeds. The metrology needs for process control and dispositioning of product continue to drive improvements in measurement uncertainty. Acceleration of research and development activities for CD and overlay measurement are essential if we are to provide viable metrology for future technology generations. All of these issues require improved methods for evaluation of measurement capability. (Refer to the *Lithography chapter*.)

On-product monitors of effective dose and focus extend utility of conventional microscopy-based CD metrology systems in process control applications. The same system can output CD and overlay measurements, as well as lithography process monitors. Process control capability and efficiency of such metrology are improving. The infrastructure to support such new applications is generally available. Monitors of effective dose and focus for lithography process control have also been developed for conventional optical metrology systems, such as used in overlay metrology. Similar capabilities, in addition to CD, sidewall, and height metrology, are now emerging in scatterometry. In all cases, rather than measure CD for the purpose of process control, with every feature's CD being a complex function of both dose and focus, these systems output measurements of process parameters themselves, with metrology errors as low as 1% (3  $\sigma$ ) for dose and ~10 nm (3  $\sigma$ ) for focus. Today's process monitor performance levels boast P/T = 0.1 for lithography process window with 15% for dose and 200 nm for focus, enabling further reduction of k<sub>1</sub> in high volume manufacturing and extending the utility of optical microlithography. While the demands on metrology systems' stability and matching are likely to increase, work in this area has already initiated the development of tighter control and matching, being a pre-requisite of accurate CD metrology, not just of process control applications and dedicated process monitors.

Capable and efficient direct process monitor-based lithography process control has the potential to overcome technology limitations of conventional CD metrology. The ongoing change of lithography process control methodology can be accelerated by industry collaboration to define the expectations in direct process control, with tests of performance and standards for both new metrology applications and applications environment. This change will, likely, result in the

lithography metrology where capable and efficient means of process control are supplemented by, and are differentiated from, superior CD metrology proper. New levels of absolute accuracy are required to meet measurement requirements for next generation technology especially in the areas of CD metrology for calibration and verification of compliance for advanced mask designs (for example, 1-D and 2-D/3-D CD metrology through pitch and layouts, in presence of optical proximity correction (OPC) and RET, at various printing conditions).

Often, special test structures are measured during manufacturing. When this is the case, active device dimensions are not measured. CD-SEM continues to be used for wafer and mask measurement of lines and via/contact. A considerable effort has been aimed at overcoming electron beam damage to photoresist used by 193 nm exposuress and that will continue when alternative lithography techniques, like EUV, are introduced; as discussed above in the microscopy section, these efforts are starting to yield real results. Stack materials, surface condition, line shape, and even layout in the line vicinity may affect CD-SEM waveform and, therefore, extracted line CD. These effects, unless they are accurately modeled and corrected, increase measurement variation and total uncertainty of CD-SEM measurements. Developments in electron beam source technology that improve resolution and precision are being tested. CD-SEM is facing an issue with poor depth of field unless a new approach to SEM-based CD measurement is found. High-voltage CD-SEM and low loss detectors have been proposed as means of extending CD-SEM.

To be able to make statistically sound SEM measurements it is essential to collect the right kind and amount of information. The collection of excess information leads to loss of throughput, and by the contrary, collection of not enough or of the wrong type of information leads to loss of process control. It is important to develop metrology methods that reveal and express the needed information with the indication of the validity of the measurements. Larger usable image field-of-view at image resolution-level pixel density allows for much greater utilization of multiple feature measurement (MFM) applications for increased information per unit time, and thus improved validity of measurement results, through increased sampling without throughput penalty.

For CD-SEMs, Design-Based Metrology (DBM) applications, which include automatic recipe setup from design information, allow for practical use of SEMs for large-scale verification of design intent, through the collection of feature 2D contour shape information and comparison to GDS files. DBM applications are becoming very important for development and verification of lithographic OPC, as the number of measurements for successfully developing OPC is expected to grow exponentially with technology generation. Also, DBM applications for Double Patterning are being explored. This is a major role where metrology interfaces with the Design for Manufacturing (DFM) community. Also, collecting and applying CD information from reticle measurements for comparison to wafer CD measurements is an important application in some cases, and would be most efficient if done through contours.

However, much work remains to be done in defining contour error source testing methodologies, contour reference metrology, and SEM modeling for contours. Contour fidelity is a prevailing challenge and an area where improvements in the state of the art could yield value to the industry. Gaps or missing segments in contours can occur for reasons related to both the sample and metrology tool. Major contributors are weak signal and breaks along edges parallel to the (fast) scan axis and contrast variation along the contour, which could be due to underlying variations in the structure (e.g., changes in sidewall angle or reentrance) or instrumental artifacts, such as edge proximity effects in an scanning electron microscope (SEM). In some cases, breaks in the contour are inherent when referencing one level to another (e.g., poly over active). This subject of contour integrity is closely related to the accuracy of contour extraction. Contour extraction algorithms employ 2-D image processing and thus function differently than conventional single-measurand CD extraction algorithms, which are applied to individual line scans. There are known significant differences specifically with regard to edge detection and the inherent degree of signal averaging. Sampling can also have a large impact, as averaging as few as five contours can significantly improve precision and, due to averaging out local roughness effects in discrete features, also improve agreement between extracted contours and simulation.

Attention must also be paid to the requirements for registration between the SEM contours and the design for successful OPC. Models must be able to compensate for rotational and lateral offsets between the SEM contour and the design, as well as for potential field distortions. This relates somewhat to the question of metrology accuracy versus production accuracy. The extent to which it is acceptable to remove metrology errors when matching contours to the design is not agreed upon. For example, a uniform magnification error removed by stretching the contour could be less problematic than non-linearity across the SEM field of view.

Another area in which useful improvements could be made in contour metrology accuracy lies in the statistical sophistication of the contour extraction and modeling software, for example, the inclusion of a 95 % confidence interval for the extracted contour. It should be noted that the final metrics in measuring contours should be compatible with the same conventional linewidth metrics used in this roadmap.

#### 8 Metrology

Scatterometry has moved into manufacturing, and does provide line shape metrology. Scatterometry refers to both single wavelength—multi angle optical scattering and to multi-wavelength—single angle methods. Recent advances have resulted in the ability to determine CD and line shape without the aid of a library of simulated results. Scatterometry has already been shown to provide a tighter distribution of key transistor electrical properties when used in an advanced process control mode. One next step is the development of scatterometry for contact and via structures, and for features with complexity which require many parameters to model. Scatterometry models assume uniform optical property of line and background materials. Surface anomalies and non-uniform dopant distribution may affect scatterometry results. Therefore, scatterometry models need calibration and periodic verification. Lithography and etch microloading effects may noticeably affect line CD. Since scatterometry makes measurements on special test structures, other CD metrology techniques (such as SEM, AFM, or TEM) need to be employed to establish correlation between CD of the scatterometry structure and CDs of the circuit. Scatterometry needs to be capable of measuring smaller test structures while improving measurement precision. The increasing usage of double patterning may create some issues in measurement of double-patterned features, as many more parameters must be measured and controlled, potentially including two statistically distinct CD, sidewall, roughness, and pitch (overlay) populations. In some schemes, an antireflective coatings (ARC) may prevent the UV light from penetrating deeper layers.

New CD measurement methods have been proposed, and it seems likely the first opportunity for them to move into manufacturing is at the 16 nm DRAM half pitch. The 22 nm half pitch is already well into the development stage and beta equipment is available for all process areas. The new potential solutions include the He ion microscope (discussed in the microscopy section) and small angle x-ray scattering (CD-SAXS). Using transmission measurements and a grating structure, CD-SAXS has shown the ability to measure average CD, sidewall roughness, and CD variation from an individual line in a grating structure, and for more complex lines through multiple layers.

The use of "feed forward" control concepts must be extended to lithography metrology taking data at least from resist and mask measurements and controlling subsequent processing, such as etch, to improve product performance. "Feed back" controlling strategy is required as well to set properly process parameter setup from a huge amount of previously collected data. The use of overlay measurement equipment for CD control has also been reported. This method is based on the fact that the change in line width also affects the length of the photoresist lines that can then be measured using the optical microscope of the overlay system. A special test structure with arrays of line and arrays of spaces is required.

CD-AFM measurements can be used to verify line shape and calibrating CD or contour measurements. New probe tip technology and 3-D tiltable cantilever is required if CD-AFM is to be applied to dense line measurement below 50 nm. Focus–Exposure correlation studies (especially for contact/via) can be using all of the above methods as well as by the dual column FIB (SEM plus Focused Ion Beam) where there is an immediate correlation with line shape. Electron holography has been proposed as a long term CD measurement technology.

At some upcoming technology node, some say 16 nm, the bulk of logic manufacturing will leave the simpler realm of planar devices and move to non-planar architectures such as FinFETs, and a similar transition for memory architecture is already imminent. This will cause many new issues to metrology, where the main variables for process control may not be the bottoms of profiles. Thus, truly 3D metrology with great sensitivity will be required.

#### **4.1. LINE ROUGHNESS**

Line edge roughness (LER) is an important part of lithography process control, and line width roughness (LWR) is an important part of etch process control. The Lithography Roadmap provides metrics for both LER and LWR. LWR correlates to an increase in transistor leakage current but not to changes in drive current. LER and LWR are determined per the SEMI standard definition. It is important to note that the precision requirements for LER and LWR are several years ahead of those required for CD as indicated below. CD-SEM and lithography process simulation systems have software that determines LER and LWR, but not all systems yet adhere to the SEMI standard for LER and LWR measurement.

LER/LWR is evaluated by two methods: spectral analysis and measurement of LER/LWR amplitude/degree (generally, 3  $\sigma$  of residuals from average position or average CD). Fourier spectrum of LER/LWR is becoming popular in R&D; however, 3  $\sigma$  is still the most useful index for practical in-line metrology. In evaluating LER/LWR, length of the inspected edge, L, and sampling interval of edge-detection,  $\Delta y$ , are the most important measurement parameters because 3  $\sigma$  strongly depends upon these values.

The recommended LER/LWR metric is thus defined as the  $3\sigma$  of residuals measured along 2-  $\mu$  m-long line for the present; however, transistor performance could be more sensitive against in-gate roughness in the future. In that case, a

new index for in-gate roughness (such as high-frequency LWR) should be additionally defined. To evaluate LWR-caused gate-CD variation separately, low-frequency LWR index should also be defined.

Another important factor in measurement of LWR/LER on imaging tools is edge detection noise. This noise has the effect of adding a positive bias to any roughness measurement. This is shown by the equation  $LWR_{meas2} = LWR_{actual2} + \sigma_{\epsilon2}$  where LWR<sub>meas</sub> is the measured value, LWR<sub>actual</sub> is the actual roughness of the target, and  $\sigma_{\epsilon}$  is the noise term, defined as the reproducibility of locating an edge along one single sampling point. The size of  $\sigma_{\epsilon}$  has been measured to be on the order of 2 nm, which means that at future technology generations this measurement artifact could mask the actual roughness to be measured. A methodology has been demonstrated to remove this noise term, leading to an unbiased estimation of the roughness. Use of this is deemed very important to ensuring accuracy of roughness measurement in the future, and should be a key ingredient in allowing for intercomparison of data across the litho-metrology community. It should be noted that LWR metrology becomes more challenging when the resolution of the metrology tool becomes close to the LWR requirement. At the 10 nm node the LWR required is 1.0 nm. Current CD-SEM equipment has comparable resolution performance.

#### **4.2. MEASUREMENT UNCERTAINTY**

Critical dimension measurement capability does not meet uncertainty requirements that include measurement variation from individual tool reproducibility, tool-to-tool matching and sample-to-sample measurement bias variation. Precision is defined by SEMI as a multiple of reproducibility. Reproducibility includes repeatability, variation from reloading the wafer, and long-term drift. In practice, reproducibility is determined by repeated measurements on the same sample and target over an extended period of time.

There is no single metrology method or technique that can deliver all needed information. Therefore, in order to be able to compare the results of various dimensional metrology tools and methods meaningfully, parameters beyond repeatability and precision need to be addressed. Each measurement application requires consideration of the need for relative accuracy (sensitivity to CD variation and insensitivity to secondary characteristic variation), absolute accuracy (traceability to absolute length scale), LER and sampling, and the destructive nature of the measurement.

Although the precision requirements for CD measurement in the ITRS have always included the effects of line shape and materials variation, repeated measurements on the same sample would never detect measurement uncertainty related to sample-to-sample bias variation. Therefore, with the current methodology the measurement uncertainty associated with variation of line shape, material, layout, or any other parameters will not be included in the precision. Typically, reference materials for CD process control are specially selected optimum or "golden" wafers from each process level. Thus, industry practice is to define measurement precision as reproducibility of the measurement for each process level. The measurement bias is not detected. This approach misses measurement bias variation component of measurement uncertainty. In light of this, a metric, total measurement uncertainty (TMU) can be used. The TMU is determined using a technology representative set of samples that accounts for variations in measurement bias associated with each process level. This idea can be extended to use with a production fleet of tools through another metric Fleet Matching Precision (FMP). These metrics assume accuracy for all tools, and that a fleet of tools behave as well as a single tool would be required. It should be noted that other metrics for accuracy and matching are also available.

It would be ideal to have all metrology tools properly characterized for measurement uncertainty including a breakout of the leading contributors to this uncertainty. It is recommended to use internationally accepted methods to state measurement uncertainty. This knowledge would help to make the most of all metrology tools, and it would prevent situations in which the measured results do not provide the required information. Finally, once the largest contributors to measurement errors are known, a faster development of better instruments could take place. It is now recommended to state the measurement uncertainty of various dimensional metrology tools according to internationally accepted methods and to identify (quantify) the leading contributors. Another possibility is the combination of information from multiple metrology techniques into "hybrid metrology", where separate, different dimensional metrology tools not only are calibrated together but can either communicate to each other to share extra information to improve each other's uncertainties and rectify inter-variable correlations.<sup>4</sup>

Calibration of inline CD metrology equipment requires careful implementation of the calibration measurement equipment referred to as reference metrology. For example, laboratory based TEM or CD-AFM must have precision that matches or exceeds inline CD and have to be frequently calibrated. Reference materials used during manufacturing must be representative to the actual process level and structure and reflect the pertinent process variations to be evaluated by the tool under test. Reports of this approach already exist.

CD measurement has been extended to line shape control. Tilt beam CD-SEM, comparison of line scan intensity variation versus line scans from a golden wafer, scatterometry, CD-AFM, dual beam (electron and gallium ion beam systems) and triple beam (electron, Gallium ion beam and Argon ion beam systems) have all been applied to line shape measurement. Sidewall angle has been proposed as the key process variable. Already, photoresist lines have shapes that are not well described by a single planar description of the sidewall. Line edge and line width roughness along a line, vertical line edge roughness, and rounded top shapes are important considerations in process control. As mentioned above, precision values change with each process level. This adds to the difficulty in determining etch bias (the difference in CD before and after etch). Electrical CD measurements provide a monitoring of gate and interconnect line width, but only after the point where reworking the wafers is no longer possible and does not allow a real-time correction of process parameter. Electric CD measurements are limited in their applicability to conducting samples.

Mask metrology is moving beyond the present optical technology. Binary and phase-shifting chromium on quartz optical photomasks have been successfully investigated with high-pressure/environmental scanning electron microscopy. Environmental SEM instrumentation equipped with high-resolution, high-signal, field emission technology in conjunction with large chamber and sample transfer capabilities are in use in the semiconductor industry for mask CD. The high-pressure SEM methodology employs a gaseous environment to help to compensate for the charge build-up that occurs under irradiation with the electron beam. Although potentially very desirable for the charge neutralization, this methodology has not been seriously employed in photomask or wafer metrology until now. This is a new application of this technology to this area, and it shows great promise in the inspection, imaging, and metrology of photomasks in a charge-free operational mode. This methodology also holds the potential of similar implications for wafer metrology. For accurate metrology, high-pressure SEM methodology also affords a path that minimizes, if not eliminates, the need for charge modeling.

Lithography metrology consists not only of overlay and CD metrology, but also includes the process control and characterization of materials needed for lithography process, especially photoresists, phase shifters, and ARCs. As these lithography materials become more complex, the materials characterization associated with them also increases in difficulty. Additionally, most non-lithography materials used in the wafer fabrication process (gate oxides, metals, low- $\kappa$  dielectrics, SOI substrates) enter the lithography process indirectly, since their optical properties affect the reflection of light at a given wavelength. Even a small variation in process conditions for a layer not normally considered critical to the lithography process (such as the thickness of the buried oxide in SOI wafers) can change the dimensions or shapes of the printed feature, if this process change affected the optical response of the layer.

As a minimum, the complex refractive index (refractive index n and extinction coefficient  $\kappa$ ) of all layers needs to be known at the lithography wavelength. Literature data for such properties are usually not available or obsolete and not reliable (derived from obsolete reflectance measurements on materials of unknown quality followed by Kramers-Kronig transform). In ideal cases, n and  $\kappa$  can be measured inline using spectroscopic ellipsometry at the exposure wavelength. Especially below 193 nm, such measurements are very difficult and usually performed outside of the fab by engineering personnel. EUV optical properties can only be determined using specialized light sources (such as a synchrotron or a EUV source for a EUV litho tool). Therefore, materials composition is often used as a figure of merit, when direct measurement of the optical properties is not practical. But even two materials with the same composition can have different optical properties (take amorphous and crystalline Si as an example).

Additional complications in the determination of the optical properties of a material arise from surface roughness, interfacial layers, birefringence, or optical anisotropy (often seen in photoresists or other organic layers responding to stress), or depth-dependent composition. For some materials for a wafer fab, it is impossible to determine the optical properties of such material, since the inverse problem of fitting the optical constants from the ellipsometric angles is underdetermined. Therefore, physical materials characterization must accompany the determination of optical properties, since physical characteristics, materials properties, and optical constants are all inter-related.

Overlay measurements are challenged by phase shift masks (PSM) and OPC masks, and the use of different exposure tools and/or techniques for different process layers will compound the difficulty. Future overlay metrology requirements, along with problems caused by low contrast levels, will drive the development of new optical or SEM methods along with SPM. The need for new target structures has been suggested as a means of overcoming the issues associated with phase shift mask and OPC alignment errors not detectable with traditional targets. Overlay for on-chip interconnect will continue to be challenging. The use of chemical mechanical polishing for planarization degrades target structures. Thus as requirements for tighter overlay control are introduced, the line edge of overlay targets in interconnect are roughened. The low- $\kappa$  materials used as insulators will continue to make overlay more difficult especially as porous low  $\kappa$  move into manufacturing.

The dramatic tightening of the overlay budget up to 20% [or 25%] of the device half-pitch, required for advanced applications in DRAM and NVM, calls for a faster introduction of alternative measuring solutions, like high-voltage SEM and scatterometry techniques, which are still far from being mature enough today, and may require breakthroughs also in metrology integration. The introduction of EUV lithography requires further development in the area of EUV mask metrology and EUV Aerial Image Measurements Systems (EUV AIMS).

#### **4.3. EXPLANATION OF UNCERTAINTY IN TABLE MET3**

The preceding concepts are summarized by the following consideration for the precision of patterning metrology: the definition for precision critically depends on the application. Given the application and the metrology instrument, a sampling plan needs to be defined. The precision specification needs to be interpreted in light of application, instrument, and sampling plan. The application defines the accuracy, single tool precision, and matching requirements. In some applications, the relative accuracy and single tool precision are paramount. In some applications, tool matching and single tool precision are paramount. In some applications, to provide the needed measurement; rather the average of multiple measurement events constitute the critical measurement episode; in this case the precision should be interpreted as the uncertainty requirement of the average. The precision numbers in the tables are changed to uncertainty numbers. The relation to precision and uncertainty ( $\sigma$ ) is given in formula (1).

$$\sigma^{2} = \sigma_{\rm P}^2 + \sigma_{\rm M}^2 + \sigma_{\rm S}^2 + \sigma_{\rm other}^2$$

(1)

Uncertainty ( $\sigma$ ) contains the following components:  $\sigma_{P}$  (Precision),  $\sigma_{M}$  (Matching),  $\sigma_{s}$  (Sample variation) and  $\sigma_{other}$  (inaccuracy and other effects). We assume normal distributions where each factor is independent and only random variations occur.<sup>5</sup>

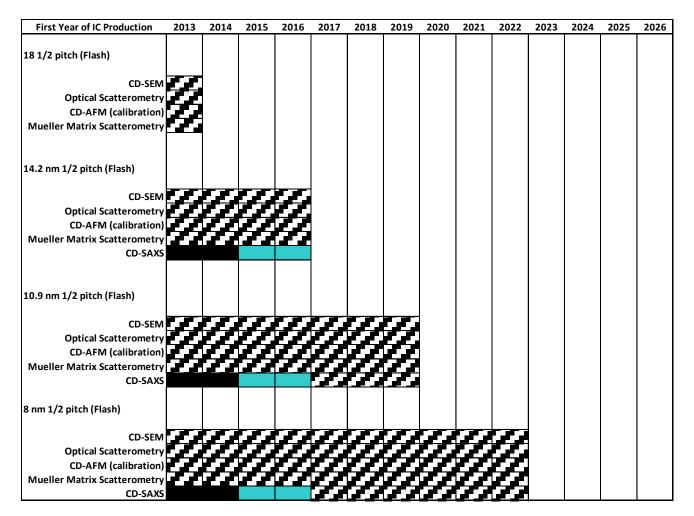

Table MET3

Lithography Metrology (Wafer) Technology Requirements

#### 12 Metrology

This legend indicates the time during which research, development, and qualification/prer-production should be taking place for the solution.

Lithography Metrology Potential Solutions

## 5. FRONT END PROCESSES METROLOGY

The industry continues to find means of extending CMOS. FinFET transistors have moved into volume manufacture and a considerable Research and Development effort is expected to extend Fin based transistors into future technology generations. Future CMOS will be both planar and non-planar. High  $\kappa$  and metal gate research and development efforts are aimed at increasing  $\kappa$ . Mobility enhancement through local stress remains a key means of scaling transistors. New channel materials will further enhance mobility. FinFET and planar transistors use high  $\kappa$  and metal gate while increases in mobility will be achieved using different technology than that used for planar CMOS. The metrology community continues research and development to fill these measurement needs. It is important to note that characterization and metrology must be tailored to the specific process used to fabricate the transistor. In this section the specific metrology needs for starting materials, surface preparation, thermal/thin films, doping technology, and front-end plasma etch technologies are covered. Process integration issues such as variability, the need to control leakage current, and the reduction in threshold voltage and gate delay and their tolerances will interact with the reality of process control ranges for gate dielectric thickness, doping profiles, junctions, and doses to drive metrology needs. Modeling studies of manufacturing tolerances continue to be a critical tool for transistor metrology strategy. Potential solutions are shown in Figure MET4.

The impact of shrinking dimension on FEP metrology is already at the point where research devices and materials exhibit materials properties associated with nano-science. For example the properties of nanowire like shapes such as a FIN in a finFET are quantum confined in two dimensions.

#### 5.1. STARTING MATERIALS

Many of the metrology challenges related to starting materials involve the emerging class of layered materials such as SOI and strained silicon on SOI. The trend toward thinner layers, along with multiple layer interfaces, poses a challenge to most material metrology techniques.

Areas of concern include the following:

- Bulk Ni and Cu measurement on p+, silicon on insulator (SOI), strained silicon (SSi), and strained silicon on insulator (SSOI) wafers

- Measurement of 109–1010 cm-3 Fe (and other bulk metals) in the top Si of thin SOI wafers

- Thickness and uniformity of very thin SOI layers (<20 nm)

- Defectivity of thin layers (e.g., threading dislocations, "HF defects")

- Particle detection (<100 nm) on layered surfaces

Small particle detection continues to be of concern for the future. More information can be found in the Starting Materials section of the *Front End Processes chapter*.

Silicon-On-Insulator (SOI) is entering the mainstream of IC device applications, and this is expected to grow further along the Roadmap. Recent device work has motivated a prediction of an increase in SOI thickness at 22 nm ½ pitch from 7 nm of Si to ~ 10 nm. This is predicted to follow another decrease in thickness for several ½ pitch nodes. This prediction may not follow the FEP roadmap SOI timing. One unmet challenge is the measurement of SOI uniformity inside die-sized areas. Across-wafer uniformity must also be characterized. An expectation has been that the materials specifications for polished silicon substrates would be transferred to SOI specifications. However, the underlying insulator structure in SOI negatively affects many of the metrology capabilities used for polished silicon substrates. Thus, there is some difficulty to measure and control SOI material properties at the level desired. The metrology community has addressed this but some issues remain. For more details on these metrology challenges see the FEP chapter on Starting Materials.

#### **5.2. SURFACE PREPARATION**

*In situ* sensors for particles, chemical composition, and possibly for trace metallics are being introduced to some wet chemical cleaning tools. Particle detection is covered in the *Yield Enhancement chapter*. Particle/defect and metallic/organic contamination analyses are covered in the Materials Characterization Section of the *Metrology* chapter.

#### **5.3. THERMAL/THIN FILMS**