# INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS

## 2003 Edition

## ASSEMBLY AND PACKAGING

THE ITRS IS DEVISED AND INTENDED FOR TECHNOLOGY ASSESSMENT ONLY AND IS WITHOUT REGARD TO ANY COMMERCIAL CONSIDERATIONS PERTAINING TO INDIVIDUAL PRODUCTS OR EQUIPMENT.

## TABLE OF CONTENTS

| Difficult Challenges2Technology Requirements4Package Design Requirements7Thermal Management7Packaging Materials Requirements8Reliability Requirements9MEMS requirements10Optoelectronics Requirements10System-in-a-Package Requirements12Flip Chip Requirements12Flip Chip Requirements14Embedded Passives Requirements16Potential Solutions17Wafer Level Packaging17Wafer Level Interconnect17Ball Grid Array Packages18Flip Density Package Substrates and Printed Wiring Boards (PWBs)19Cross-cut ITWG Issues21Design21Modeling and Simulation21Metrology.21Test22                     | Scope                               | 1  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----|

| Package Design Requirements7Thermal Management7Packaging Materials Requirements8Reliability Requirements9MEMS requirements9MEMS requirements10Optoelectronics Requirements10System-in-a-Package Requirements12Flip Chip Requirements14Embedded Passives Requirements14RF and Mixed-signal Requirements16Potential Solutions17Wafer Level Packaging17Chip-to-Next-Level Interconnect17Ball Grid Array Packages18Fine Pitch BGA /Chip Scale Packages18High Density Package Substrates and Printed Wiring Boards (PWBs)19Cross-cut ITWG Issues21Design21Modeling and Simulation21Metrology21 | Difficult Challenges                | 2  |

| Thermal Management.7Packaging Materials Requirements.8Reliability Requirements.9MEMS requirements.10Optoelectronics Requirements.10System-in-a-Package Requirements.12Flip Chip Requirements.14Embedded Passives Requirements.14RF and Mixed-signal Requirements.16Potential Solutions.17Wafer Level Packaging.17Chip-to-Next-Level Interconnect.17Ball Grid Array Packages.18Fine Pitch BGA /Chip Scale Packages.18High Density Package Substrates and Printed Wiring Boards (PWBs).19Cross-cut ITWG Issues.21Design.21Environment, Safety, and Health.21Metrology.21                    | Technology Requirements             |    |

| Reliability Requirements9MEMS requirements10Optoelectronics Requirements10System-in-a-Package Requirements12Flip Chip Requirements14Embedded Passives Requirements14RF and Mixed-signal Requirements16Potential Solutions17Wafer Level Packaging17Chip-to-Next-Level Interconnect17Ball Grid Array Packages18Fine Pitch BGA /Chip Scale Packages18High Density Package Substrates and Printed Wiring Boards (PWBs)19Cross-cut ITWG Issues21Design21Modeling and Simulation21Metrology.21                                                                                                  |                                     |    |

| MEMS requirements10Optoelectronics Requirements10System-in-a-Package Requirements12Flip Chip Requirements14Embedded Passives Requirements14RF and Mixed-signal Requirements16Potential Solutions17Wafer Level Packaging17Chip-to-Next-Level Interconnect17Ball Grid Array Packages18Fine Pitch BGA /Chip Scale Packages18High Density Package Substrates and Printed Wiring Boards (PWBs)19Cross-cut ITWG Issues21Design21Environment, Safety, and Health21Metrology.21                                                                                                                   | Packaging Materials Requirements    | 8  |

| Optoelectronics Requirements10System-in-a-Package Requirements12Flip Chip Requirements14Embedded Passives Requirements14RF and Mixed-signal Requirements16Potential Solutions17Wafer Level Packaging17Chip-to-Next-Level Interconnect17Ball Grid Array Packages18Fine Pitch BGA /Chip Scale Packages18High Density Package Substrates and Printed Wiring Boards (PWBs)19Cross-cut ITWG Issues21Design21Interconnent, Safety, and Health21Modeling and Simulation21Metrology21                                                                                                             | Reliability Requirements            | 9  |

| System-in-a-Package Requirements12Flip Chip Requirements14Embedded Passives Requirements14RF and Mixed-signal Requirements16Potential Solutions17Wafer Level Packaging17Chip-to-Next-Level Interconnect17Ball Grid Array Packages18Fine Pitch BGA /Chip Scale Packages18High Density Package Substrates and Printed Wiring Boards (PWBs)19Cross-cut ITWG Issues21Design21Environment, Safety, and Health21Metrology21                                                                                                                                                                     | MEMS requirements                   | 10 |

| Flip Chip Requirements14Embedded Passives Requirements14RF and Mixed-signal Requirements16Potential Solutions17Wafer Level Packaging17Chip-to-Next-Level Interconnect17Ball Grid Array Packages18Fine Pitch BGA /Chip Scale Packages18High Density Package Substrates and Printed Wiring Boards (PWBs)19Cross-cut ITWG Issues21Design21Environment, Safety, and Health21Metrology21                                                                                                                                                                                                       | Optoelectronics Requirements        | 10 |

| Flip Chip Requirements14Embedded Passives Requirements14RF and Mixed-signal Requirements16Potential Solutions17Wafer Level Packaging17Chip-to-Next-Level Interconnect17Ball Grid Array Packages18Fine Pitch BGA /Chip Scale Packages18High Density Package Substrates and Printed Wiring Boards (PWBs)19Cross-cut ITWG Issues21Design21Environment, Safety, and Health21Metrology21                                                                                                                                                                                                       | System-in-a-Package Requirements    | 12 |

| RF and Mixed-signal Requirements16Potential Solutions17Wafer Level Packaging17Chip-to-Next-Level Interconnect17Ball Grid Array Packages18Fine Pitch BGA /Chip Scale Packages18High Density Package Substrates and Printed Wiring Boards (PWBs)19Cross-cut ITWG Issues21Design21Modeling and Simulation21Metrology21                                                                                                                                                                                                                                                                       |                                     |    |

| Potential Solutions.17Wafer Level Packaging.17Chip-to-Next-Level Interconnect17Ball Grid Array Packages.18Fine Pitch BGA /Chip Scale Packages18High Density Package Substrates and Printed Wiring Boards (PWBs)19Cross-cut ITWG Issues21Design21Environment, Safety, and Health21Modeling and Simulation21Metrology.21                                                                                                                                                                                                                                                                    | Embedded Passives Requirements      | 14 |

| Wafer Level Packaging.17Chip-to-Next-Level Interconnect17Ball Grid Array Packages.18Fine Pitch BGA /Chip Scale Packages18High Density Package Substrates and Printed Wiring Boards (PWBs)19Cross-cut ITWG Issues21Design21Environment, Safety, and Health21Modeling and Simulation21Metrology.21                                                                                                                                                                                                                                                                                          | RF and Mixed-signal Requirements    | 16 |

| Chip-to-Next-Level Interconnect17Ball Grid Array Packages18Fine Pitch BGA /Chip Scale Packages18High Density Package Substrates and Printed Wiring Boards (PWBs)19Cross-cut ITWG Issues21Design21Environment, Safety, and Health21Modeling and Simulation21Metrology21                                                                                                                                                                                                                                                                                                                    | Potential Solutions                 | 17 |

| Ball Grid Array Packages18Fine Pitch BGA /Chip Scale Packages18High Density Package Substrates and Printed Wiring Boards (PWBs)19Cross-cut ITWG Issues21Design21Environment, Safety, and Health21Modeling and Simulation21Metrology21                                                                                                                                                                                                                                                                                                                                                     | Wafer Level Packaging               | 17 |

| Fine Pitch BGA /Chip Scale Packages       18         High Density Package Substrates and Printed Wiring Boards (PWBs)       19         Cross-cut ITWG Issues       21         Design       21         Environment, Safety, and Health       21         Modeling and Simulation       21         Metrology       21                                                                                                                                                                                                                                                                        | Chip-to-Next-Level Interconnect     | 17 |

| High Density Package Substrates and Printed Wiring Boards (PWBs)       19         Cross-cut ITWG Issues       21         Design       21         Environment, Safety, and Health       21         Modeling and Simulation       21         Metrology       21                                                                                                                                                                                                                                                                                                                             | Ball Grid Array Packages            | 18 |

| Cross-cut ITWG Issues       21         Design       21         Environment, Safety, and Health       21         Modeling and Simulation       21         Metrology       21                                                                                                                                                                                                                                                                                                                                                                                                               | Fine Pitch BGA /Chip Scale Packages | 18 |

| Environment, Safety, and Health                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                     |    |

| Environment, Safety, and Health                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Design                              | 21 |

| Modeling and Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -                                   |    |

| Metrology21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                     |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •                                   |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Test                                |    |

## LIST OF FIGURES

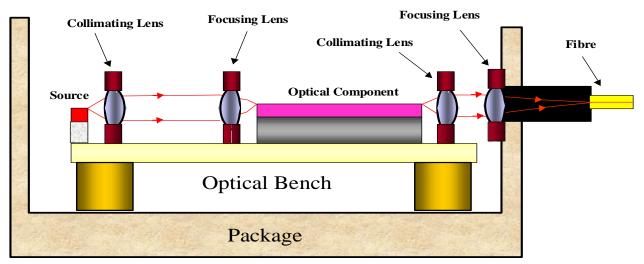

| Figure 72  | Optoelectronics Package Design Illustration              | 10 |

|------------|----------------------------------------------------------|----|

| LIST OF TA | BLES                                                     |    |

| Table 92a  | Assembly and Packaging Difficult Challenges—Near-term    | 2  |

| Table 92b  | Assembly and Packaging Difficult Challenges—Long-term    | 3  |

| Table 93a  | Single-chip Packaging Technology Requirements—Near-term  | 4  |

| Table 93b  | Single-chip Packages Technology Requirements—Long-term   | 6  |

| Table 94   | Materials Challenges                                     | 9  |

| Table 95   | System-in-a-Package Requirements                         | 14 |

| Table 96   | Chip-to-next-level Potential Solutions                   | 18 |

| Table 97   | BGA Potential Solutions                                  |    |

| Table 98   | Single Chip Packages Potential Solutions                 | 19 |

| Table 99   | BGA and FBGA/CSP Package Potential PWB Solutions         | 19 |

| Table 100  | Flip Chip Substrate Top-side Fan-out Potential Solutions | 20 |

|            |                                                          |    |

## ASSEMBLY AND PACKAGING

## SCOPE

There is an increased awareness in the industry that assembly and packaging is an essential and integral part of the semiconductor product. In many market segments packaging technology is now a critical competitive factor, as it affects operating frequency, power, complexity, reliability, and cost. New emerging device technologies and applications are driving the requirements and innovation for assembly and packaging. As a result the technology boundaries between semiconductor technology, packaging technology, and system technologies in electronics are blurring.

Package designs no longer can be developed independently of the chip and system; they must be considered concurrently as part of the overall system design. As a result, a broad range of complex design parameters must be analyzed to optimize the complete system, and trade-offs among chip, package, and system are required. Package design, to effectively address higher performance while reducing cost on a more diversified base of technology, is driving increasing complexity in design process, tools, and the need for more accurate materials information.

To address these shifts in the industry needs, this year's Assembly and Packaging chapter has been expanded and additional focus has been placed on cross-chapter reviews. Many of the most difficult challenges have also been changed to address the needed shifts in research focus. Since the 2002 ITRS Update publication, the scope of the Assembly and Packaging chapter has been expanded to include the following:

- Updates on requirements

- Design

- Materials

- System-in-a-package (SiP)

- Flip chip

- Updates on potential solutions

- Chip-to-next-level interconnect

- Single chip packaging

- BGA and CSP packaging

Many of the Assembly and Packaging roadmap attributes are driven by the electronics products and board/substrate industries, and many of the challenges have system solutions. As a result, the solutions to certain packaging challenges are outside of the scope of this roadmap. To ensure that the needs of the semiconductor community are met, and to better understand system needs, the Assembly and Packaging International Technical Working Group (ITWG) continues to strive for:

- Membership of the TWG to include representatives from electronic systems and board/substrate industries

- Partnerships with organizations developing roadmaps for systems with the National Electronics Manufacturers Initiative (NEMI) and board/substrate industries with the Institute for Interconnecting and Packaging Electronic Circuits (IPC). The scope of these respective roadmaps has been identified and broadened.

- Synchronization of the systems, board/substrate, and packaging roadmaps

The packaging requirements are grouped by four new product categories that were developed based on the changing packaging market. These application areas encompass the majority of the product stream of the semiconductor industry. The technology addressed in the roadmap provides at least 80% of the revenue in each application area (in other words, the revenue center of gravity). The low-cost and hand-held segments have been combined into a single category this year based on the realization that there will not be a significant difference in the cost or major performance requirements in these segments any longer. The memory packaging category has also been eliminated as a separate category. These changes in product sectors will be reviewed with NEMI to develop a revised set of product categories that are common between the roadmaps where possible. These applications areas are:

| Low-cost/Hand-held | <\$500 consumer products, wireless products, disk drives, and displays                        |

|--------------------|-----------------------------------------------------------------------------------------------|

| Cost-performance   | <\$3000 notebooks, desktop personal computers, telecommunications                             |

| High-performance   | >\$3000 high-end workstations, servers, avionics, supercomputers, most demanding requirements |

| Harsh              | Under-the-hood and other hostile environments                                                 |

## **DIFFICULT CHALLENGES**

The most difficult challenges facing the assembly and packaging industry are presented in Table 92. These challenges are intended to provide a mechanism to allow the research community to focus resources in the areas of greatest need.

| Difficult Challenges $\geq 45$ nm/Through 2010                                               | Summary of Issues                                                                                                                                          |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Improved Organic Substrates                                                                  | Tg compatible with Pb free solder processing                                                                                                               |  |  |  |  |  |  |

|                                                                                              | Increased wireability at low cost                                                                                                                          |  |  |  |  |  |  |

|                                                                                              | Improved impedance control and lower dielectric loss to support higher frequency applications                                                              |  |  |  |  |  |  |

|                                                                                              | Improved planarity and low warpage at higher process temperatures                                                                                          |  |  |  |  |  |  |

|                                                                                              | Low-moisture absorption                                                                                                                                    |  |  |  |  |  |  |

|                                                                                              | Low-cost embedded passives                                                                                                                                 |  |  |  |  |  |  |

|                                                                                              | Substrate cost is barrier to flip chip wide spread adoption today                                                                                          |  |  |  |  |  |  |

|                                                                                              | Increased via density in substrate core                                                                                                                    |  |  |  |  |  |  |

|                                                                                              | Alternative plating finish to improve reliability                                                                                                          |  |  |  |  |  |  |

| Improved Underfills for Flip Chip on Organic Substrates                                      | Thermal performance and thermal coupling between parts                                                                                                     |  |  |  |  |  |  |

|                                                                                              | Materials which enable integration of SMT, varying semiconductors, and substrate types reliably                                                            |  |  |  |  |  |  |

|                                                                                              | Thin die, stack die, very large and very small die, passives component integration, SAW, shielding interconnect process                                    |  |  |  |  |  |  |

|                                                                                              | Narrowing gaps                                                                                                                                             |  |  |  |  |  |  |

|                                                                                              | Higher bump densities                                                                                                                                      |  |  |  |  |  |  |

| Coordinated Design Tools and Simulators to address Chip,<br>Package, and Substrate Co-design | Mix signal co-design and simulation environment                                                                                                            |  |  |  |  |  |  |

|                                                                                              | Integrated analysis tools for transient thermal analysis and integrated thermal mechanical analysis                                                        |  |  |  |  |  |  |

|                                                                                              | Electrical (power disturbs, EMI, signal integrity associated with higher frequency/current and lower voltage switching)                                    |  |  |  |  |  |  |

|                                                                                              | Commercial EDA supplier support                                                                                                                            |  |  |  |  |  |  |

|                                                                                              | System level co-design is needed now. EDA support for "native" area array is required to meet the Roadmap projections.                                     |  |  |  |  |  |  |

|                                                                                              | Educational programs required to train engineers in these technologies/requirements.                                                                       |  |  |  |  |  |  |

| Impact of Cu/low κ on Packaging                                                              | Direct wirebond and bump to Cu                                                                                                                             |  |  |  |  |  |  |

|                                                                                              | Bump and underfill technology to assure low-k dielectric integrity                                                                                         |  |  |  |  |  |  |

|                                                                                              | Improved mechanical strength of dielectrics                                                                                                                |  |  |  |  |  |  |

|                                                                                              | Interfacial adhesion                                                                                                                                       |  |  |  |  |  |  |

|                                                                                              | Reliability of first level interconnect with low $\kappa$                                                                                                  |  |  |  |  |  |  |

|                                                                                              | Mechanisms to measure the critical properties need to be developed.                                                                                        |  |  |  |  |  |  |

|                                                                                              | Probing over copper/low $\kappa$ due to damage and bonding over probe mark                                                                                 |  |  |  |  |  |  |

| High Current Density Packages                                                                | Electromigration will become a more limiting factor. It must be addressed through materials changes together with thermal/mechanical reliability modeling. |  |  |  |  |  |  |

|                                                                                              | Whisker growth                                                                                                                                             |  |  |  |  |  |  |

|                                                                                              | Thermal dissipation                                                                                                                                        |  |  |  |  |  |  |

Table 92a Assembly and Packaging Difficult Challenges—Near-term

| Difficult Challenges <45 nm/Beyond 2010                                                                                                                                                             | Summary of Issues                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Package Cost does not follow the Die Cost Reduction Curve                                                                                                                                           | Margin in packaging inadequate to support investment required to reduce cost                                                                                                                                                                                                                                                                                      |

| Small Die with High Pad Count, High Power Density, and/or<br>High Frequency                                                                                                                         | Current density, operating temperature, etc for these devices exceed the capabilities of current assembly and packaging technology                                                                                                                                                                                                                                |

| High Frequency Die                                                                                                                                                                                  | Substrate wiring density to support >20 lines/mm                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                     | Lower loss dielectrics-skin effect above 10 GHz                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                     | "Hot spot" thermal management needs to be addressed before 2007. There is a "brick wall" at five-micron lines and spaces. Design TWG would like to have an upper bound on thermal management capability of future packages.                                                                                                                                       |

| Close Gaps between Substrate Technology and the Chip                                                                                                                                                | Interconnect density scaled to silicon (silicon I/O density increasing faster than the package substrate technology                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                     | Production techniques will require silicon-like production and process technologies after 2005.                                                                                                                                                                                                                                                                   |

| System-level Design Capability to Integrated Chips, Passives,<br>and Substrates                                                                                                                     | Partitioning of system designs and manufacturing across numerous companies<br>will make required optimization for performance, reliability, and cost of<br>complex systems very difficult. Complex standards for information types<br>and management of information quality along with a structure for moving<br>this information will be required. Hardware only |

|                                                                                                                                                                                                     | This is also an issue before 2007.Embedded passives may be integrated into the "bumps" as well as the substrates.                                                                                                                                                                                                                                                 |

| New Device Types (Organic, Nanostructures, Biological) that require New Packaging Technologies                                                                                                      | Organic device packaging requirements not yet define (will chips grow their own packages)                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                     | Biological interfaces will require new interface types                                                                                                                                                                                                                                                                                                            |

| Bumpless area array technologies will be needed during this<br>period. Face to face packages and other 3D packages are<br>examples. High frequency, low power and low profile are<br>driving forces |                                                                                                                                                                                                                                                                                                                                                                   |

| Table 92b | Assembly and Packaging | Difficult Challeng | ges—Long-term |

|-----------|------------------------|--------------------|---------------|

|-----------|------------------------|--------------------|---------------|

## **TECHNOLOGY REQUIREMENTS**

Packaging technology continues to change rapidly. Assembly and packaging needs are driven as much by market application requirements as by silicon technology. Cost will drive technology trade-offs for all market segments. The key single chip package technology requirements have been updated by the domestic and international TWGs as shown in Tables 93a and b.

Although assembly and packaging costs are expected to decrease over time on a cost-per-pin basis, the chip and package pincount is increasing more rapidly than cost-per-pin is decreasing. This explosion in pin count is increasing not only the absolute cost of assembly and packaging on a per-chip basis, but also the substrate and system-level packaging costs. In the low-cost product and cost performance markets, the cost per pin decreases are also expected to flatten out over the next several years. This will drive a faster rate of package cost increase in these segments. To satisfy the requirements for the increasing numbers of pins needed to leverage silicon productivity more fully, the industry must implement affordable new assembly and packaging technologies that will be more independent of pincount.

Pin count will continue to increase in all segments while die sizes are expected to remain constant. This will drive a continuing need for finer off-chip and off-package pitch. The off-chip digital frequency has been increased to match onchip in some high-speed communications applications, which will drive the need for improved package signal integrity. The need for very high-speed digital pins and high frequency RF I/O requirements have also been added to the requirement tables.

Packaging technology that addresses very high-power density has already been developed for high-end applications, but will need to be cost-reduced to enable broader applications.

| Year of Production                          | 2003              | 2004      | 2005      | 2006      | 2007      | 2008      | 2009      |

|---------------------------------------------|-------------------|-----------|-----------|-----------|-----------|-----------|-----------|

| Technology Node                             |                   | hp90      |           |           | hp65      |           |           |

| DRAM <sup>1</sup> / <sub>2</sub> Pitch (nm) | 100               | 90        | 80        | 70        | 65        | 57        | 50        |

| Cost per Pin Minimum for Contract As.       | sembly [1,2] (Cen | ts/Pin)   |           |           |           |           |           |

| Low-cost, hand-held and memory              | 0.30-0.56         | 0.29–.53  | .27–.50   | .26–.48   | .25–.45   | .23–.43   | .22–.41   |

| Cost-performance                            | .75–1.30          | .71–1.24  | .67–1.17  | .64–1.11  | .61–1.05  | .58–1.00  | .55–.96   |

| High-performance                            | 1.98              | 1.88      | 1.78      | 1.69      | 1.61      | 1.52      | 1.45      |

| Harsh                                       | 0.36-3.20         | 0.32-2.88 | 0.29-2.60 | 0.26-2.33 | 0.23-2.11 | 0.21-2.00 | 0.20-1.90 |

| Chip Size $(mm^2)$ [3]                      |                   |           |           |           |           |           |           |

| Low-cost                                    | 100               | 100       | 100       | 100       | 100       | 100       | 100       |

| Cost-performance                            | 140               | 140       | 140       | 140       | 140       | 140       | 140       |

| High-performance                            | 310               | 310       | 310       | 310       | 310       | 310       | 310       |

| Harsh                                       | 100               | 100       | 100       | 100       | 100       | 100       | 100       |

| Maximum Power (Watts/mm <sup>2</sup> ) [4]  |                   |           |           |           |           |           |           |

| Low-cost (Watts) [1]                        | 2.5               | 2.7       | 2.8       | 3         | 3         | 3         | 3         |

| Cost-performance                            | 0.57              | 0.6       | 0.65      | 0.7       | 0.74      | 0.79      | 0.83      |

| High-performance                            | 0.48              | 0.51      | 0.54      | 0.58      | 0.61      | 0.64      | 0.64      |

| Harsh                                       | 0.14              | 0.16      | 0.16      | 0.18      | 0.18      | 0.2       | 0.2       |

| Core Voltage (Volts)                        |                   | •         | •         |           | •         | •         |           |

| Low-cost                                    | 1.2               | 1.2       | 1         | 0.9       | 0.9       | 0.8       | 0.8       |

| Cost-performance                            | 1.2               | 1.2       | 1         | 0.9       | 0.9       | 0.8       | 0.8       |

| High-performance                            | 1.2               | 1.2       | 1         | 0.9       | 0.9       | 0.8       | 0.8       |

| Harsh                                       | 2.5               | 2.5       | 1.2       | 1.2       | 1.2       | 1.2       | 1.2       |

Table 93a Single-chip Packaging Technology Requirements—Near-term

Manufacturable solutions exist, and are being optimized Manufacturable solutions are known Interim solutions are known

Manufacturable solutions are NOT known

| Year of Production                                           | 2003          | 2004       | 2005       | 2006       | 2007       | 2008       | 2009       |

|--------------------------------------------------------------|---------------|------------|------------|------------|------------|------------|------------|

| Technology Node                                              |               | hp90       |            |            | hp65       |            |            |

| DRAM <sup>1</sup> / <sub>2</sub> Pitch (nm)                  | 100           | 90         | 80         | 70         | 65         | 57         | 50         |

| Package Pincount Maximum [5][6]                              | •             | •          | •          | •          |            | •          |            |

| Low-cost                                                     | 112-408       | 122-500    | 134–550    | 144-600    | 160-660    | 180-720    | 180-800    |

| Cost-performance                                             | 500-1452      | 500-1600   | 550-1760   | 550-1936   | 600–2140   | 600–2400   | 660-2800   |

| High-performance                                             | 2400          | 3000       | 3400       | 3800       | 4000       | 4400       | 4600       |

| Harsh                                                        | 450           | 500        | 550        | 600        | 660        | 720        | 780        |

| Minimum Overall Package Profile (mm)                         | •             | •          | •          | •          |            | •          |            |

| Low-cost                                                     | 0.5           | 0.5        | 0.5        | 0.5        | 0.5        | 0.5        | 0.5        |

| Cost-performance                                             | 1             | 0.8        | 0.8        | 0.8        | 0.8        | 0.65       | 0.65       |

| High-performance                                             | N/A           | N/A        | N/A        | N/A        | N/A        | N/A        | N/A        |

| Harsh                                                        | 1             | 0.8        | 0.8        | 0.8        | 0.8        | 0.8        | 0.8        |

| Performance: On-Chip (MHz)[7]                                | •             | •          | •          | •          |            | •          |            |

| Low-cost                                                     | 502/3194      | 552/3514   | 607/3865   | 668/4251   | 735/4676   | 800/5000   | 830/5150   |

| Cost-performance                                             | 3090          | 3990       | 5170       | 5630       | 6740       | _          | _          |

| High-performance                                             | 3090          | 3990       | 5170       | 5630       | 6740       | _          |            |

| Harsh                                                        | 72            | 80         | 88         | 96         | 106        | 116.6      | 128.26     |

| Performance: Chip-to-Board for Peripher                      | al Buses (MHz | [7]        | •          | •          |            | •          |            |

| Low-cost                                                     | 100           | 100        | 100        | 100        | 100        | 100        | 100        |

| Cost-performance (for multi-drop nets)                       | 400           | 533        | 600        | 667        | 733        | 800        | 800        |

| High-performance (for differential-pair point-to-point nets) | 2000          | 2500       | 3125       | 3906       | 4883       | 6103       | 7629       |

| Harsh                                                        | 72            | 80         | 88         | 96         | 106        | 106        | 115        |

| Maximum Junction Temperature                                 | •             | •          | •          | •          |            | •          |            |

| Cost-performance                                             | 90            | 90         | 85         | 85         | 85         | 85         | 85         |

| High-performance                                             | 90            | 90         | 85         | 85         | 85         | 85         | 85         |

| Harsh-complex ICs                                            | 150           | 150        | 150        | 150        | 150        | 150        | 150        |

| Operating Temperature Extreme: Ambient                       | (°C)          |            |            |            |            |            | -          |

| Low-cost                                                     | 55            | 55         | 55         | 55         | 55         | 55         | 55         |

| Cost-performance                                             | 45            | 45         | 45         | 45         | 45         | 45         | 45         |

| High-performance                                             | 45            | 45         | 45         | 45         | 45         | 45         | 45         |

| Harsh-complex ICs                                            | -40 to 125    | -40 to 125 | -40 to 125 | -40 to 125 | -40 to 125 | -40 to 125 | -40 to 125 |

Table 93a

Single-chip Packaging Technology Requirements—Near-term (continued)

Manufacturable solutions exist, and are being optimized

Manufacturable solutions are known

Interim solutions are known

Manufacturable solutions are NOT known

Notes for Tables 93a and 93b:

[1] Cost reduction will slow down as technology matures and economy of scale benefits are reduced.

[2] Cost refers to the average contract assembly cost per pin for each category.

[3] Die sizes for high performance will not increase beyond 310 mm and cost performance die sizes will flatten out as die size approaches 310 mm).

[4] Power will be limited more by system level cooling and test constraints than packaging.

[5] Pin counts will be limited for some applications by system level PWB cost impact.

[6] The pin counts assume the signal to reference pin ratios will vary from 1:4 to 2:1 across different markets segments.

[7] Maximum off-chip frequency will be limited to a small number of pins in many cases combined with a large number of lower frequency pins

Table 93b Single-chip Packages Technology Requirements—Long-term

| Tuble 950 Sin                              |           | -         |           |           | -           |             |

|--------------------------------------------|-----------|-----------|-----------|-----------|-------------|-------------|

| Year of Production                         | 2010      | 2012      | 2013      | 2015      | 2016        | 2018        |

| Technology Node                            | hp45      |           | hp32      |           | hp22        |             |

| DRAM <sup>1/2</sup> Pitch (nm)             | 45        | 35        | 32        | 25        | 22          | 18          |

| Cost (Cents/Pin) [1] [2]                   |           |           |           |           |             |             |

| Low-cost                                   | .22–.41   | 0.22-0.36 | 0.22-0.35 | 0.22-0.31 | 0.22-0.29   | 0.22-0.27   |

| Cost-performance scale at 5%               | 0.52–0.94 | 0.5–.86   | 0.5–.77   | 0.5–0.69  | 0.5–0.65    | 0.5–0.59    |

| High-performance scale at 5%               | 1.37      | 1.23      | 1.17      | 1.05      | 100         | 0.9         |

| Harsh scale at 5%                          | 0.27-1.54 | 0.24–1.38 | 0.22-1.31 | .22–1.17  | 0.22–1.12   | 0.22-1.00   |

| Chip Size (mm <sup>2</sup> )[3]            |           |           |           |           |             |             |

| Low-cost                                   | 100       | 100       | 100       | 100       | 100         | 100         |

| Cost-performance                           | 140       | 140       | 140       | 140       | 140         | 140         |

| High-performance                           | 310       | 310       | 310       | 310       | 310         | 310         |

| Harsh                                      | 100       | 100       | 100       | 100       | 100         | 100         |

| Power Density (Watts/mm <sup>2</sup> ) [4] |           | •         | •         |           | •           | •           |

| Low-cost (Watts)                           | 3         | 3         | 3         | 3         | 3           | 3           |

| Cost-performance                           | 0.85      | 0.89      | 0.98      | —         | 1.08        | —           |

| High-performance                           | 1.55      | 1.71      | 1.78      | —         | 2.05        | —           |

| Harsh                                      | 0.22      | 0.24      | 0.25      | 0.27      | 0.28        | 0.29        |

| Core Voltage (Volts)                       |           |           |           |           |             |             |

| Low-cost                                   | 0.6       | 0.6       | 0.5       | 0.4       | 0.4         | 0.4         |

| Hand-held                                  | 0.5       | 0.5       | 0.4       | 0.4       | 0.4         | 0.4         |

| Cost-performance                           | 0.6       | 0.6       | 0.6       | 0.5       | 0.5         | 0.5         |

| High-performance                           | 0.6       | 0.6       | 0.6       | 0.5       | 0.5         | 0.5         |

| Harsh                                      | 1.2       | 1         | 0.9       | 0.9       | 0.9         | 0.6         |

| Package Pincount [5] [6]                   | ·         |           |           |           |             |             |

| Low-cost scale                             | 208–777   | 249–932   | 270–1011  | 325–1213  | 351–1314    | 421–1576    |

| Cost-performance                           | 780–2782  | 936–3338  | 1014-3616 | 1216-4339 | 1318-4702   | 1581-5642   |

| High-performance                           | 4009      | 4810      | 5335      | 6402      | 7042        | 8450        |

| Harsh                                      | 642       | 706.2     | 812.13    | 933.9495  | 1074.041925 | 1235.148214 |

| Overall Package Profile (mm)               | ·         |           |           |           |             |             |

| Low-cost                                   | 0.3       | 0.3       | 0.3       | 0.3       | 0.3         | 0.3         |

| High-performance                           | N/A       | N/A       | N/A       | N/A       | N/A         | N/A         |

| Harsh                                      | 0.8       | 0.5       | 0.5       | 0.8       | 0.5         | 0.5         |

| Performance: On-Chip (MHz) [7]             | •         | •         | •         | -         |             | •           |

| Low-cost                                   | 956-6079  | —         | 1243-7903 | —         | 1616-10274  | —           |

| Cost-performance                           | 12000     | —         | 19000     | -         | 29000       | —           |

| High-performance                           | 12000     | —         | 19000     | —         | 29000       | —           |

| Harsh                                      | 138       | —         | 179       | _         | 234         | —           |

Manufacturable solutions exist, and are being optimized

Manufacturable solutions are known Interim solutions are known Manufacturable solutions are NOT known

| Year of Production                                       | 2010            | 2012       | 2013       | 2015       | 2016       | 2018       |

|----------------------------------------------------------|-----------------|------------|------------|------------|------------|------------|

| Technology Node                                          | hp45            |            | hp32       |            | hp22       |            |

| DRAM <sup>1</sup> / <sub>2</sub> Pitch (nm)              | 45              | 35         | 32         | 25         | 22         | 18         |

| Performance: Chip-to-Board for Peripheral                | l Buses (MHz)[7 | 7]         |            |            |            |            |

| Low-cost                                                 | 125             | —          | 125        | —          | 150        | —          |

| Cost-performance (multi-drop nets)                       | —               | 800        | —          | 800        | —          | 800        |

| High-performance (differential-pair point-to-point nets) | —               | 14901      | —          | 29103      | —          | 56843      |

| Harsh                                                    | 125             | 125        | 125        | 150        | 150        | 150        |

| Junction Temperature Maximum ( $^{\circ}C$ ) for C       | ost- performanc | e          |            |            |            |            |

| Low-cost                                                 | 125             | 125        | 125        | 125        | 125        | 125        |

| Cost-performance                                         | 85              | 85         | 85         | 85         | 85         | 85         |

| High-performance                                         | 85              | 85         | 85         | 85         | 85         | 85         |

| Harsh                                                    | 150             | 150        | 150        | 150        | 150        | 150        |

| Harsh-complex ICs                                        | 150             | 150        | 150        | 150        | 150        | 150        |

| Operating Temperature Extreme: Ambient (                 | °℃)             |            |            |            |            |            |

| Low-cost                                                 | 55              | 55         | 55         | 55         | 55         | 55         |

| Cost-performance                                         | 45              | 45         | 45         | 45         | 45         | 45         |

| High-performance                                         | 45              | 45         | 45         | 45         | 45         | 45         |

| Harsh                                                    | -40 to 125      | -40 to 125 | -40 to 125 | -40 to 125 | -40 to 125 | -40 to 125 |

| Harsh-complex ICs                                        | -40 to 150      | -40 to 150 | -40 to 150 | -40 to 150 | -40 to 150 | -40 to 150 |

Table 93b

Single Chip Packages Technology Requirements—Long-term (continued)

Manufacturable solutions exist, and are being optimized

Manufacturable solutions are known

Interim solutions are known

Manufacturable solutions are NOT known

## PACKAGE DESIGN REQUIREMENTS

Package design complexity (chip-to-module and chip/module-to-board) and scope are continuously increasing while the market intensifies the demand for design cycle time reduction and high design confidence. Physical, electrical, thermal, mechanical, assembly, and manufacturability considerations, in addition to cost and availability, confront the package designer. The package design process requires continuous improvements in design and analysis tools. The tools for layout, wiring, electrical, mechanical, and thermal design tasks must enhance usability and minimize interface incompatibilities if design cycle reductions are to be realized. The goal is an integrated design system. The scope of this integrated design system must include or be coordinated with chip design so that efficient chip/package co-design is feasible. Ideally, it should be linked to the system design so as to incorporate those requirements and trade-offs.

Differential-pair point-to-point wiring nets are required for high speed, broadband data communications. Data rate and number of such high speed ports will see significant increase in the foreseeable future. The driver-to-receiver power ratio will increase to afford improved attenuation budget, requiring excellent isolation between transmitting and receiving paths.

### THERMAL MANAGEMENT

The task of dissipating the heat from integrated circuits while maintaining acceptable junction temperatures has been a significant challenge for semiconductor and system manufacturers. Power and junction temperature requirements are shown by market segment in Tables 93a and b. These ITRS projections indicate that the thermal management challenge will significantly increase in the future due to increasing power, decreasing junction temperatures, and a continuing need to have cost-effective solutions.

In the hand-held market segment, power availability is limited by battery power. The power dissipation is currently limited by the user (the heat sink is the hand or lap), and cooling is usually accomplished without forced air. Challenges increase from the desire to use higher power devices with the increasing convergence of computing with communication (driving higher performance and power in this market); and with an increasing need for system level cooling (more than one hot device). Solutions could include use of higher thermal conductivity materials, reduction in internal thermal resistance, and potentially in more novel approaches to manage cooling while not discomforting the user. Cooling needs to be an integral part of the product design.

Desktop processors for the cost-performance market have required forced air cooling for the system, and have represented a wide spectrum of electronic products. With area array flip chip, the backside of the chip provides a direct heat path for cooling. The packaging challenge has been to create an interface with the chip that provides very low thermal resistance, is cost effective, reliable, and also enables system level solutions. System cooling design must also be acceptable in this market, with implications to cost, acoustic noise, reliability, and high volume manufacturing. As Tables 93a and b show, power is expected to continue to increase while target junction temperatures decrease. In 2002 this equates to a  $\Delta T$  of 45° (and shrinking over time) with the ambient. At an expected power of 75 Watts (and growing over time), this becomes a significant challenge for acceptable solutions. Some of the key developments and innovations are: more advanced/efficient air-cooling, boundary layer control, engineered surfaces, and cost-effective alternative cooling systems.

Notebook computing products are also in the cost-performance market segment. Although they may not push the highest power levels while on battery operation, they do pose significant cooling requirements based on form factor, weight, and ergonomic issues (maintaining comfortable outer case temperatures for the user). Additional developmental areas would include redirection of internal thermal resistance, engineered surfaces, new novel cooling systems, and solutions that allow multiple and different power levels for the product.

The high-performance market sector has experienced a dramatic increase in power over the different generations. Aircooling has been the preferred option to keep costs within bounds. In addition to managing total chip power requirements in excess of 100 Watts, solutions to manage power density and internal hot spots are necessary. Assuming identical junction and ambient temperatures, the higher power levels in this sector will demand a 40%–50% reduction in junction to ambient thermal resistance compared with the cost-performance segment. Current solutions are already focused on complete integration from the chip through the system, and this approach will need to continue. Significant engineering development will be needed for power increases at each technology generation, with capabilities needed equivalent to closed-loop cooled systems. Solutions must of course also be acceptable to the end-use customers. A major additional challenge will be to ensure that thermal management does not impede the migration path of products from this sector into the cost-performance market.

### **PACKAGING MATERIALS REQUIREMENTS**

Assembly and Packaging involves the package physical design, and the design of materials and manufacturing processes to realize the physical design goals in performance and reliability. Dramatic improvements in materials properties will be required to support the projected technology nodes driven by projected semiconductor requirements in power, frequency and I/O, as well as market requirements in cost, size, weight, and environments. The rapid reduction in wirebond pitch will call for reduction in wire size, capillary, and solutions for wire sweep, electrical signal integrity and bond pad design, all of which will require significant materials improvement, and materials process innovation beyond what are available today.

The projected reduction of flip chip bump pitch from the current 150  $\mu$ m to 100  $\mu$ m in 2009 and thence to 70  $\mu$ m will result in significant reduction in UBM via size as well as bump size and bump height. Materials innovation in solder-UBM structure as well as underfill materials and dispense process will be required to provide high volume manufacturing process and reliable package structure. One important area of concern will be electrical-thermal migration in the solder UBM structure associated with the expected current density increase with small UBM openings. Underfill void and adhesion in the reduced solder bumps gap and spacing between the bumps will pose additional difficult materials challenge.

With the introduction of Cu/low- $\kappa$  materials the on-die dielectric stiffness will be approaching in stiffness to the materials on the package side such as the molding compound or underfill materials. Thermomechanical stresses will be transmitted to the die across the die-package interface. The IC and package is one single physical structure, and it will be necessary to provide the process knowledge, materials database and the design methodology to assure that the materials on both sides of the interface, particularly the chip dielectric and copper interconnect, will be robust under thermal mechanical stress. For example, low modulus underfill materials and molding compound materials may become necessary. With the growing importance of die stacking to the main stream of consumer/handle applications, very thin die from continued reduction of wafer thickness will be called for, providing significant challenge and opportunities to the packaging materials engineer.

Major efforts have been underway to address environmental concerns such as materials and surface finishes for lead free solder assembly and for halogen free materials development and implementation, and they are expected to continue in the coming years. Materials properties like dielectric constant, dielectric loss, and thermal conductivity will be very significant to meet higher frequency and higher power demands. Materials research and development will be needed to meet thermal management challenges such as for thermal interface materials, heat spreaders, and external solutions. Knowledge of packaging materials properties are critically needed for modeling and simulation of electrical, thermal, and reliability performance for package design release and new package development. Methods for accurate characterization of materials properties and materials interface properties for packaging materials in their use environment will be needed. Establishment of materials database to make the materials information available to the community will be very important.

| Materials Challenges   | Issues                                                                                     |

|------------------------|--------------------------------------------------------------------------------------------|

| Wirebond and Capillary | Materials that enable 20 micron pitch without wire sweep and provide good signal integrity |

| Solder Materials       | Solder and UBM the supports 100 micron pitch and high current density                      |

| Underfills             | Ability to support 100 pitch on large die                                                  |

| Thermal Interfaces     | Increased power density                                                                    |

| Materials Properties   | Methodology and characterization database for frequencies above 10 GHz,                    |

| Molding Compound       | Low modulas materials that reduce stress on low-к wafer structures                         |

Table 94 Materials Challenges

## **RELIABILITY REQUIREMENTS**

With the introduction of many new package formats, copper chip interconnect, low- $\kappa$  chip dielectrics, direct chip attach, and area array interconnect there are many new requirements to packaged device reliability. Many of these new materials and package configurations require extensive characterization given the lack of historical reliability data. Extensive use of simulation to help validate and understand reliability performance is also required to assure these technologies are deployed with reasonable risk factors.

Some new package designs, materials, and technologies will not be capable of reliable performance in all market applications. More in-depth knowledge of the relevant failure mechanisms coupled with knowledge of the market use conditions will be required to bring new package technologies to the marketplace. Better definition of environmental requirements for each market segment would facilitate package development tailored to the market needs and help ensure consistent reliability performance among suppliers as well as between suppliers and customers. More research emphasis on physical and thermo-mechanical models of failure mechanisms is needed to support this trend.

Conception and development of tools for rapid electrical and physical fault isolation of package and interconnect technologies is critical. Faster techniques are needed to execute statistically significant studies of material bulk and interface properties. Developing extensions of current fault isolation and package analytical technologies (such as X-ray, acoustic, and Moire) needs to be balanced with development of new technologies for small defect visualization (such as X-ray tomography). Organic chemical interface analysis techniques are growing in importance with the introduction of new organic materials. Low alpha materials need to be considered during the timeframe of the ITRS to reduce errors induced by alpha radiation. Measurement techniques and standards for alpha radiation effects are not adequate to support the increased alpha sensitivity anticipated for advanced technology processes.

Interfacial delamination will continue to be a critical reliability hazard that is worsened by the trend to larger chips and new materials. Standard methods and acceptance criteria for interfacial adhesion are lacking. Fundamental work is needed

to establish adhesion strength and degradation rate versus environmental factors (temperature, relative humidity) as well as a function of interfacial physical (such as roughness, composition) and chemical (van der Waals, dipole, covalent) properties. The CTE mismatch between the chip and the substrate should be reduced to mitigate large chip packagingrelated reliability issues.

New electrostatic discharge (ESD) test methods and equipment are required to comprehend increasing pincount and shrinking interconnect pitch. Improved handling solutions for bare chip and packaged devices will help ESD related reliability issues.

## **MEMS** REQUIREMENTS

MEMS technology has broadly expanded in the last decade to become the standard for many automotive, medical, telecommunications, and consumer electronics applications and the predicted market growth for MEMS technology is very high. One of the major bottlenecks for the continued growth of MEMS products has been packaging technology.

Like standard semiconductor devices, MEMS devices need environment protection, electrical signal integrity, mechanical support, and thermal management. However, in addition, MEMS may require packaging that provides access to chemical or biological environments they interact with. Many of the MEMS applications also demand inert/vacuum inside the package. For example: pressure sensors "media compatible" for the disposable blood pressure application are not "media compatible" for a ten-year automotive application. As a result, even though the functionality of two MEMS could be the same, the differences in environment drive quite different package requirements. To effectively reduce cost, improved manufacturability, and improve reliability standardized technologies need to be develop that can handle this broad range of requirements. MEMS do not require high pin counts, or very fine pad pitches for interconnect.

Some single-chip ceramic, molded, chip scale, and wafer-level packaging technologies have been used successfully to address some of these applications requirements. However, MEMS multichip packages and 3D packaging solutions are still under development.

To meet product performance requirements MEMS devices and packaging designers must consider the interface of structural elements, signal processing and power elements, signal and energy changing elements, material technology, harsh media compatibility, test equipment process and standards, packaging techniques, and processes. While many of these issues are common with semiconductor packaging some are unique to MEMS. CADs systems package design standards and methodologies, packaging assembly attributes, reliability standards and assessment, and interfaces of micro and macro packaging attributes need to be developed to handle these unique design requirements.

### **OPTOELECTRONICS REQUIREMENTS**

Figure 72 Optoelectronics Package Design Illustration

Optoelectronics packaging brings together two realms of component packaging—the traditional electronic packaging with its associated issues (covered elsewhere in this chapter) and the integration of optical components into the optoelectronics package. Figure 72 is an illustration of an optoelectronic design. The electronic packaging issues may be viewed as a special case of multi-chip packaging. I/O counts are typically lower and die sizes are smaller than standard multi-chip modules. The main issue is the high data rates and low signal levels of the converted optical signal. Another challenge is integration of optical functionality into the optoelectronics package. Optical functionality includes passive devices such as array waveguide gratings (AWG), filters, splitters, etc., and active devices including lasers, modulators, detectors, amplifiers, switches, and attenuators. An integral part of the optical-to-electrical and electrical-to-optical conversion is the high data rate, broadband electrical signals. It is desirable to integrate the serializer-deserializer (Serdes) in the optoelectronics package.

The key mechanical issues with optoelectronics packaging is aligning the optical path and maintaining this alignment under all service conditions. Typical systems for higher data rates utilize a 9.3  $\mu$ m diameter fiber core that needs to be aligned to a narrow active device. For example, a detector for 10 Gbps use may have an active area on the order of 25  $\mu$ m. The transmitter (laser) alignment tolerances are even more stringent with the mode size of the order of 10  $\mu$ m and a mode shape that would need to be converted to match the fiber mode. This may require additional optics (lenses) between the laser diode and the fiber. Each added optic adds to the alignment complexity and increases the loss. These interfaces can be a large source of attenuation greatly impacting the system loss budget. Hermetic packaging is used to keep the optical pathway clear of contamination. Contamination in the pathway leads to additional loss and can damage the optical surfaces through absorption-generated heat or focusing of the optical beam. Cost reduction, especially for Metro applications, including broadband services delivery to small businesses, schools and homes, is driving the need to develop a non-hermetic approach. Fiber feed-throughs in the hermetic package add a great deal of complexity and cost. Care needs to be taken in mounting the optical components due to strain-induced birefringence. This effect can cause wavefront distortion and scattering.

The main issue in assembly is how to automate the alignment process, including automatic fiber handling and placement, to reduce costs. A self-aligning structure, which can be assembled without concern regarding changing alignments, is needed. A standardized approach to packaging and alignment would ease the development of automation equipment. Currently, only a few high-volume manufacturers are automating their processes. Simple issues such as how to handle fiber pigtails through an automation process need to be addressed as well as standardized carriers and systems.

A better understanding of the materials properties and careful selection of assembly materials are necessary to successfully engineer optoelectronics packages. The optoelectronics package may contain substrates as diverse as silicon, AlGaAs, InP, Polymer, or SiGe in various combinations in one package. An understanding of the thermomechanical effects and material interactions will be necessary for the fabrication of reliable packages. Viscoelastic properties of the mounting adhesives will be necessary to understand the environmental stressing behavior of fiber alignment mountings.

Integrated design capabilities will need to be developed for optoelectronics packaging. Design systems that encompass the optical, electrical, thermal, and mechanical requirements of these packaged systems are needed.

Thermal management requirements in optoelectronic packaging are more stringent than in their electronic counterparts. Whereas thermal management in standard electronics is primarily for reliability concerns, in optoelectronics many devices have temperature sensitivity to their operating parameters, such as wavelength. Indeed, it is common to use temperature tuning of the optical devices in order to operate on a specific wavelength on the ITU grid. This leads to a need for integration of thermo-electric (Peltier) coolers into the package and an adequate method for dissipating the waste heat. Future devices will be densely packed and operate at very high rates (10 Gbps, 40 Gbps—160 Gbps), which will only further exacerbate the thermal issues. Additionally, thermal drift will impact fiber alignment through differential expansion of the different components of the package. The optoelectronic packages may include optical devices such as laser diodes, photo diodes, light guides, and fibers. Since the characteristics of many of these components are temperature sensitive, the efficient control of the operating temperatures of the packages is required.