# INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS

2003 EDITION

# **DESIGN**

THE ITRS IS DEVISED AND INTENDED FOR TECHNOLOGY ASSESSMENT ONLY AND IS WITHOUT REGARD TO ANY COMMERCIAL CONSIDERATIONS PERTAINING TO INDIVIDUAL PRODUCTS OR EQUIPMENT.

# **TABLE OF CONTENTS**

| Scope       |                                                                          | 1  |

|-------------|--------------------------------------------------------------------------|----|

| Complexity  | and Crosscutting Challenges                                              | 3  |

| Crosscuttii | ng Challenge 1—Productivity                                              | 4  |

| Crosscuttii | ng Challenge 2—Power                                                     | 5  |

| Crosscuttii | ng Challenge 3—Manufacturing Integration                                 | 5  |

| Crosscuttii | ng Challenge 4—Interference                                              | 5  |

|             | ng Challenge 5—Error Tolerance                                           |    |

| •           | hnology Challenges                                                       |    |

|             | xed-signal and RF-specific DT Trends and Challenges                      |    |

|             | ocess                                                                    |    |

|             | rocess Challenges—Near Term (>50 nm)rocess Challenges—Long Term (<50 nm) |    |

|             |                                                                          |    |

|             | /el Designevel Design Challenges—Near Term (>50 nm)                      |    |

| •           | evel Design Challenges—Long Term (<50 nm)                                |    |

| Logical, Ci | rcuit, and Physical Design                                               | 19 |

| Logical, (  | Circuit, and Physical Design Challenges                                  | 20 |

|             | rification                                                               |    |

|             | erification Challenges—Near Term (>50 nm)                                |    |

| _           | erification Challenges—Long Term (<50 nm)                                |    |

|             | stest Challenges—Near Term (>50 nm)                                      |    |

|             | est Challenges—Long Term (<50 nm)                                        |    |

| _           | Design Technology Requirements                                           |    |

|             | WG Issues                                                                |    |

| Modeling a  | and Simulation                                                           | 36 |

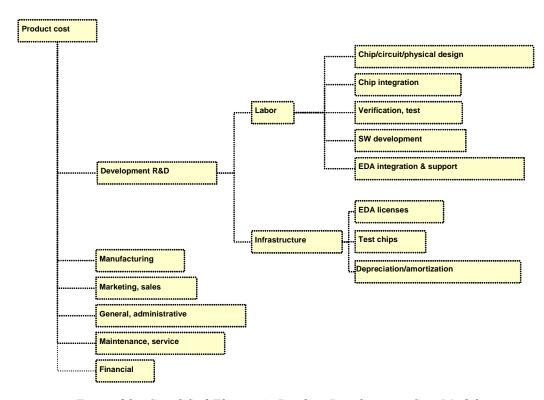

| APPENDÏX    | : DT Cost and Value                                                      | 36 |

| Labor Cos   | ts                                                                       | 37 |

| Infrastruct | ure Costs                                                                | 38 |

| Approxima   | ited Total Design Cost                                                   | 38 |

| _           |                                                                          |    |

| LIST OF FIG |                                                                          |    |

| Figure 13   | Impact of Design Technology on SOC LP-PDA Implementation Cost            | 2  |

| Figure 14   | Landscape of Design Technology                                           | 3  |

| Figure 15   | Required Evolution of Design System Architecture                         | 9  |

| Figure 16   | Current Design Flow                                                      |    |

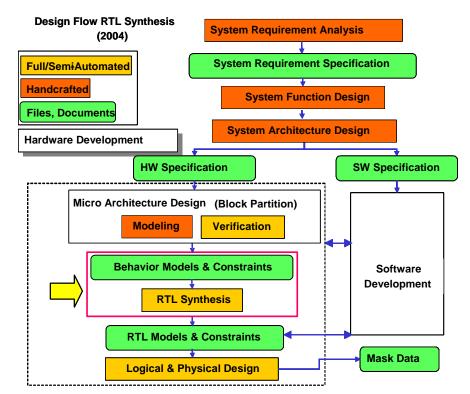

| Figure 17   | RTL Synthesis for Design Flow in year 2004                               | 15 |

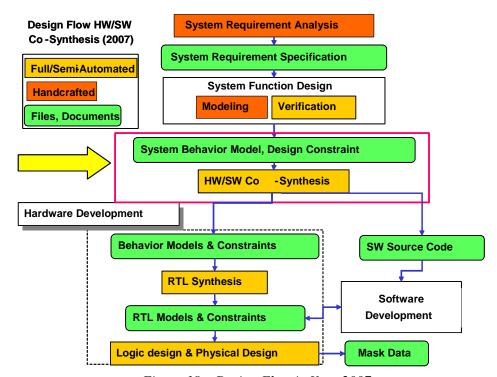

| Figure 18   | Design Flow in Year 2007                                                 |    |

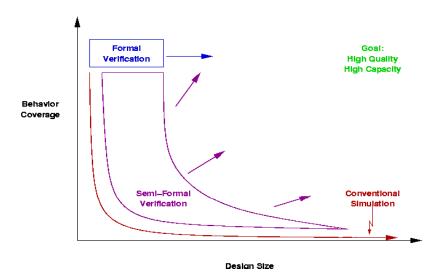

| Figure 19   | Current Verification Tool Landscape                                      |    |

| Figure 20   | Simplified Electronic Product Development Cost Model                     | 37 |

# **LIST OF TABLES**

| Table 13 | Near-term Breakthroughs in Design Technology for AMS               | 7  |

|----------|--------------------------------------------------------------------|----|

|          | Design Process Challenges                                          |    |

| Table 15 | System-level Design Challenges                                     | 16 |

| Table 16 | Logical, Circuit, and Physical Design Challenges                   | 20 |

| Table 17 | Design Verification Challenges                                     | 26 |

| Table 18 | Design Test Challenges                                             | 32 |

| Table 19 | Additional Design Technology Requirements                          | 36 |

| Table 20 | Design Technology Improvements and Impact on Designer Productivity | 38 |

# DESIGN

# SCOPE

Design technology (DT) enables the conception, implementation, and validation of microelectronics-based systems. Elements of DT include tools, libraries, manufacturing process characterizations, and methodologies. DT transforms ideas and objectives of the electronic systems designer into manufacturable and testable representations. The role of DT is to enable profits and growth of the semiconductor industry via cost-effective production of designs that fully exploit manufacturing capability. In the 2003 ITRS, the Design ITWG is responsible for the Design and System Drivers Chapters, along with models for clock frequency, layout density, and power dissipation in support of the Overall Roadmap Technology Characteristics. Specific DT challenges and needs are mapped, as appropriate, to System Drivers. Readers of this chapter are encouraged to also review previous editions of the ITRS Design Chapter, which provide excellent and still-relevant summaries of DT needs.

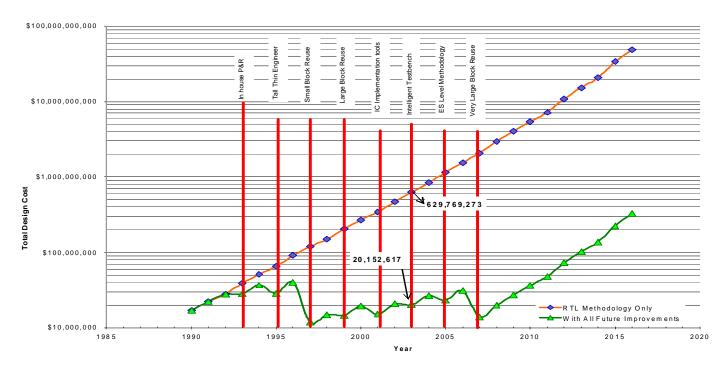

The main message in 2003 remains—Cost (of design) is the greatest threat to continuation of the semiconductor roadmap. Cost determines whether differentiating value is best achieved in software or in hardware, on a programmable commodity platform or on a new IC. Manufacturing non-recurring engineering (NRE) costs are on the order of one million dollars (mask set + probe card); design NRE costs routinely reach tens of millions of dollars, with design shortfalls being responsible for silicon re-spins that multiply manufacturing NRE. Rapid technology change shortens product life cycles and makes time-to-market a critical issue for semiconductor customers. Manufacturing cycle times are measured in weeks, with low uncertainty. Design and verification cycle times are measured in months or years, with high uncertainty. Without foundry amortization and ROI for supplier industries, the semiconductor investment cycle stalls. Previous ITRS editions have documented a design productivity gap: the number of available transistors grows faster than the ability to meaningfully design them. Yet, investment in process technology has by far dominated investment in design technology. The good news is that enabling progress in DT continues. Figure 13 shows that estimated design cost of the system-onchip low-power (SOC-LP) PDA defined in the System Drivers Chapter is \$20M in 2003, versus \$630M had DT innovations between 1993 and 2003 not occurred (analysis details are given in the Appendix). The bad news is that software can account for 80% of embedded-systems development cost; test cost has grown exponentially relative to manufacturing cost; verification engineers outnumber design engineers on microprocessor project teams; etc. Today, many design technology gaps are crises.

Figure 13 Impact of Design Technology on SOC LP-PDA Implementation Cost

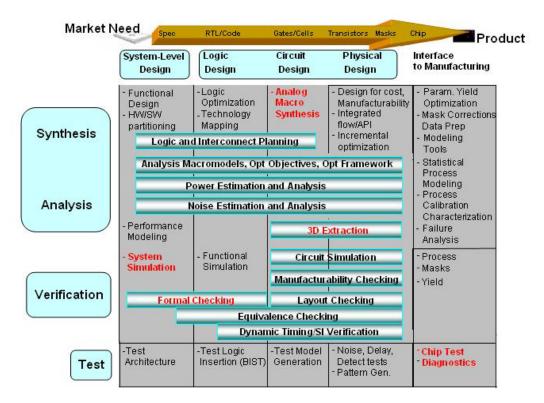

This chapter first presents *silicon complexity* and *system complexity* challenges, followed by five *crosscutting challenges* (productivity, power, manufacturing integration, interference, and error tolerance) that permeate all DT areas. The bulk of the chapter then sets out detailed challenges according to a traditional landscape of DT areas (see Figure 14): design process; system-level design; logical, circuit and physical design; design verification; and design test. These challenges are discussed at a level of detail that is actionable by management, R&D, and academia in the target supplier community, i.e., the electronic design automation (EDA) industry. As appropriate, the detailed challenges are mapped to the MPU, SOC, AMS, and memory system drivers; most challenges map to MPU and SOC, reflecting today's EDA technology and market segmentation. A brief unified overview of AMS-specific DT is given to reflect the rise of application- and driver-specific DT, and the likely organization of future ITRS Design Chapter editions according to system drivers, rather than traditional areas of DT.

<sup>&</sup>lt;sup>1</sup> Additional discussion of analog/mixed-signal circuits issues is contained in the System Drivers Chapter (AMS Driver). Test equipment and the test of manufactured chips are discussed in the Test Chapter, while this chapter addresses design for testability, including built-in self test (BIST).

Figure 14 Landscape of Design Technology.

Roadmapping of DT is different from roadmapping of manufacturing technology. Manufacturing technology seeks to realize (for example, a target tolerance) and faces limits imposed by physical laws and material properties. In contrast, DT seeks to optimize (for example, total wirelength) and faces limitations imposed by computational intractability, the unknown scope of potential applications, and the multi-objective nature of design optimization. Because underlying optimizations are intractable, heuristics are inherent to DT, as are practical trade-offs among multiple criteria such as density, speed, power, testability, or turnaround time. Evaluation of DT quality is thus context-sensitive, and dependent on particular methodologies or design instances. Furthermore, alignment of technology advances with ITRS nodes is less strict for DT. While ITRS nodes occur discretely when all needed technology elements are in place, DT improvements can generally improve productivity or quality even "in isolation," and are thus deployable when developed.

# **COMPLEXITY AND CROSSCUTTING CHALLENGES**

DT faces two basic types of complexity—silicon complexity and system complexity—that follow from roadmaps for ITRS manufacturing technologies.

Silicon complexity refers to the impact of process scaling and the introduction of new materials or device/interconnect architectures. Many previously ignorable phenomena now have great impact on design correctness and value:

- non-ideal scaling of device parasitics and supply/threshold voltages (leakage, power management, circuit/device innovation, current delivery)

- coupled high-frequency devices and interconnects (noise/interference, signal integrity analysis and management, substrate coupling, delay variation due to cross-coupling)

- manufacturing variability (statistical process modeling and characterization, yield, leakage power)

- scaling of global interconnect performance relative to device performance (communication, synchronization)

- *decreased reliability* (gate insulator tunneling and breakdown integrity, joule heating and electromigration, single-event upset, general fault-tolerance)

- complexity of manufacturing handoff (reticle enhancement and mask writing/inspection flow, NRE cost) and

• *process variability* (library characterization, analog and digital circuit performance, error-tolerant design, layout reuse, reliable and predictable implementation platforms)

Silicon complexity places long-standing paradigms at risk, as follows: 1) system-wide synchronization becomes infeasible due to power limits and the cost of robustness under manufacturing variability; 2) the CMOS transistor becomes subject to ever-larger statistical variabilities in its behavior; and 3) fabrication of chips with 100% working transistors and interconnects becomes prohibitively expensive. Available implementation fabrics (like direct-mapped custom through general-purpose software programmable) easily span four orders of magnitude in performance (such as GOps/mW), and there is added opportunity to leave value on the table via ill-advised guard bands, abstractions, or other methodological choices. These challenges demand more broadly trained designers and design technologists, as well as continued mergers between traditionally separated areas of DT (synthesis-analysis, logical-physical, etc.).

System complexity refers to exponentially increasing transistor counts enabled by smaller feature sizes and spurred by consumer demand for increased functionality, lower cost, and shorter time-to-market. Many challenges are facets of the nearly synonymous productivity challenge. Additional complexities (system environment or component heterogeneity) are forms of diversity that arise with respect to system-level SOC integration. Design specification and validation become extremely challenging, particularly with respect to complex operating contexts. Trade-offs must be made between all aspects of value or quality, and all aspects of cost. (A simplistic example: "Moore's Law" for clock frequency might suggest trade-off of design time (= time-to-market) for speed at roughly 1% per week.) Implied challenges include:

- *reuse* (support for hierarchical design, heterogeneous SOC integration (modeling, simulation, verification, test of component blocks) especially for analog/mixed-signal)

- verification and test (specification capture, design for verifiability, verification reuse for heterogeneous SOC, system-level and software verification, verification of analog/mixed-signal and novel devices, self-test, intelligent noise/delay fault testing, tester timing limits, test reuse)

- cost-driven design optimization (manufacturing cost modeling and analysis, quality metrics, co-optimization at diepackage-system levels, optimization with respect to multiple system objectives such as fault tolerance, testability, etc.)

- *embedded software design* (predictable platform-based system design methodologies, codesign with hardware and for networked system environments, software verification/analysis)

- reliable implementation platforms (predictable chip implementation onto multiple circuit fabrics, higher-level handoff to implementation) and

- *design process management* (design team size and geographic distribution, data management, collaborative design support, "design through system" supply chain management, metrics and continuous process improvement)

Together, the silicon and system complexity challenges imply *superexponentially increasing complexity* of the design process. To deal with this complexity, DT must in general 1) provide concurrent optimization and analysis of more complex objectives and constraints, 2) acknowledge additional considerations such as design reuse and manufactured system cost in the design optimization, and 3) encompass additional scope such as embedded software design and interfaces to manufacturing. The tremendous scope of silicon and system complexities is in itself also a challenge to the roadmapping of DT and the EDA industry. Five *crosscutting* challenges—Productivity, Power, Manufacturing Integration, Interference, and Error-Tolerance—are given for which potential solutions are distributed across all areas of DT. The first crosscut challenge, closely linked to system and design process complexity, is by far the most massive and critical. The second through fifth crosscut challenges are narrower in scope, and mostly address silicon complexity issues.

## CROSSCUTTING CHALLENGE 1—PRODUCTIVITY

To avoid exponentially increasing design cost, overall productivity of designed functions on chip must scale at  $> 2 \times$  per node. Reuse productivity (including migration and AMSRF core reuse) of design, verification and test must also scale at  $> 2 \times$  per node. Implied needs are in: 1) verification, which is a bottleneck that has now reached crisis proportions; 2) reliable and predictable silicon implementation fabrics that support ever-high level system design handoff; 3) embedded software design, which has emerged as the most critical challenge to SOC productivity; 4) particularly for the MPU context, improved productivity of large, distributed design organizations that work with tools from a variety of sources; 5) automated methods for analog and mixed-signal (AMS) design and test, which are required by the SOC and AMS

<sup>&</sup>lt;sup>2</sup> A "Law of Observed Functionality," notorious in consumer electronics, states that transistor count increases exponentially while the system value (utility) increases linearly (see T. Claasen, "The Logarithmic Law of Usefulness," Semiconductor International, July 1998). Similarly diminishing returns in the MPU space (Pollack's Rule) are described in the System Drivers Chapter.

system drivers. These improvements will require metrics of normalized design quality as a function of design quality, design NRE cost, manufacturing NRE cost, manufacturing variable cost, and semiconductor product value. Metrics of design technology quality such as stability, predictability, and interoperability must be developed and improved as well. Time-to-market of new design technology must be reduced, such as via standards and platforms for interoperability and DT reuse.

## **CROSSCUTTING CHALLENGE 2—POWER**

Non-ideal scaling of planar CMOS devices, together with the roadmap for interconnect materials and package technologies, presents a variety of challenges related to power management and current delivery. 1) Extrapolation from the Overall Roadmap Technology Characteristics and System Drivers Chapter shows that HP MPU power consumption significantly exceeds the high-performance single-chip package power limits established in the Assembly and Packaging Chapter, even with allowed power densities in excess of 250W/cm². The SOC-LP PDA driver requires flat average and standby power, even as logic content and throughput continue to grow exponentially. DT must address the resulting *power management gap* that is shown in Table 12 of the *System Drivers* chapter. 2) Increasing power densities worsen thermal impact on reliability and performance, while decreasing supply voltages worsen switching currents and noise. These trends stress on-chip interconnect resources (such as to control IR drop in light of the Assembly and Packaging roadmap for bump count and passivation opening size), ATE equipment limits, and burn-in paradigms. 3) Integration of distinct high-performance, low operating power, and low standby power devices demands power optimizations that simultaneously exploit many degrees of freedom, including multi-V<sub>t</sub>, multi-T<sub>ox</sub>, multi-V<sub>dd</sub> coexisting in a single core—while guiding additional power optimizations at the architecture, operating system, and application software levels. 4) Leakage power varies exponentially with key process parameters such as gate length, oxide thickness and threshold voltage; this presents severe challenges in light of both scaling and variability.

#### Crosscutting Challenge 3—Manufacturing Integration

"Red bricks," technology requirements for which no known solutions exist, are increasingly common throughout the ITRS. On the other hand, challenges that are impossible to solve within a single technology area of the ITRS may be solvable (more cost-effectively) with appropriate intervention from, or partnership with, DT. Feasibility of future technology nodes will come to depend on such "sharing of red bricks." Several examples are as follows. 1) Tester equipment cost and speed limitations may be addressed by more rapid adoption of new fault models (for example, crosstalk, path delay), along with corresponding automatic test pattern generation (ATPG) and built-in self-test (BIST) techniques. 2) System implementation cost, performance verification, and overall design TAT may be improved through die-package-board co-optimization and analysis, as well as DT for system-in-package design. 3) CD control requirements in the Lithography, PIDS, Front-End Processing, and Interconnect technology areas may be relaxed by new DT for correctness under manufacturing variability (e.g., variability-aware circuit design, regularity in layout, timing structure optimization, and static performance verification). 4) Manufacturing NRE cost can be reduced through more intelligent interfaces to mask production and inspection flows.

## CROSSCUTTING CHALLENGE 4—INTERFERENCE

Resource-efficient communication and synchronization, already challenged by global interconnect scaling trends, are increasingly hampered by noise and interference. Prevailing signal integrity methodologies in logical, circuit and physical design, while apparently scalable through the 100 nm node, are reaching their limits of practicality. These methodologies include repeater insertion rules for long interconnects, slew rate control rules, power/ground distribution design for inductance management, etc. Scaling and SOC integration of mixed-signal and RF components will require more flexible and powerful methodologies. Issues include noise headroom (especially in low-power devices and dynamic circuits); large numbers of capacitively and inductively coupled interconnects; supply voltage IR drop and ground bounce; thermal impact on device off-currents and interconnect resistivities; and substrate coupling. A basic DT challenge is to improve characterization, modeling, analysis and estimation of noise and interference at all levels of design.

## **CROSSCUTTING CHALLENGE 5—ERROR TOLERANCE**

Relaxing the requirement of 100% correctness for devices and interconnects may dramatically reduce costs of manufacturing, verification, and test. Such a paradigm shift is likely forced in any case by technology scaling, which leads to more transient and permanent failures of signals, logic values, devices, and interconnects. Several example issues are as follows. 1) Beyond 90 nm, single-event upsets (soft errors) severely impact field-level product reliability, not only for embedded memory, but for logic and latches as well. 2) Current methods for accelerated lifetime testing (burn-in) become

infeasible as supply voltages decrease (resulting in exponentially longer burn-in times); even power demands of burn-in ovens become overwhelming. 3) Atomic-scale effects can demand new "soft" defect criteria, such as for non-catastrophic gate oxide breakdown. In general, automatic insertion of robustness into the design will become a priority as systems become too large to functionally test at manufacturing exit. Potential measures include automatic introduction of redundant logic and on-chip reconfigurability for fault tolerance, development of adaptive and self-correcting or self-repairing circuits, and software-based fault-tolerance.

# **DESIGN TECHNOLOGY CHALLENGES**

The remainder of this Chapter details challenges and potential solutions in the five traditional areas of DT. As noted above, most challenges map to MPU and SOC, reflecting today's EDA technology and market segmentation. Nevertheless, we begin with an overview of AMS-specific DT trends and challenges in order to emphasize 1) the trend toward application- and driver-specific DT; 2) the criticality of AMS-specific DT in scaling design productivity and quality; and 3) the likely organization of future ITRS Design Chapter editions according to system drivers. These AMS-specific challenges are also included in the summary Tables 14 through 18.

# ANALOG, MIXED-SIGNAL AND RF-SPECIFIC DT TRENDS AND CHALLENGES

Analog and RF circuits are different compared to digital circuits. They do not contain quantized information that is represented in a defined range of voltage levels for the two states of a bit ("high" ( $V_{dd}$  – noise tolerance) and "low" ( $V_{ss}$  + noise tolerance)) and during a defined discrete time interval (such as clock signal high). Rather the signals processed in analog and RF circuits are continuous in time and amplitude up to a much higher degree of precision (or to a smaller tolerance both in time and amplitude). Therefore non-idealities like linearity, noise, parasitic elements and electrical non-uniformity of the devices used in a circuit directly cause distortion and noise in the analog or RF signals processed in the circuit. Digital circuits have the built-in ability to suppress a high level of these noise sources due to a significant gain in the transition point of each logic gate. This simple signal-recovery principle cannot be used in analog and RF signal processing due to the much higher dynamic range of the involved signals. Speed issues, or simply the fact that a signal-recovery circuit produces more noise and distortion than it prevents the signal from being susceptible to, make these issues much more challenging and less straightforward in the analog domain.

Analog and RF designs have driven the needs for high precision compact modeling as well as for characterization and extraction of all kinds of device non-idealities. However, the above-mentioned problems make extraction of simple rules for higher levels of abstraction in analog and RF circuit design (or even layout) very difficult. Tools used for digital circuits have been in a wrong style but also too inaccurate to be used in analog design. Since the number of analog or even RF transistors per chip increases at a much slower rate compared to digital transistors per chip, historically all these boundary conditions have kept analog and RF designers away from system-level design tools. Circuit and system design has remained mainly at the level covered by the section on Logical, Circuit and Physical Design later in this chapter. Today similar problems to those commonly known for analog and RF designs start to arise in digital designs as well (IR-drop, cross-talk, etc.). SOC digital designs share chip area with analog and RF circuits. The ever-shortened time to market and the need for higher productivity have changed historic paradigms in recent years, and new analog and RF specific challenges for the EDA industry are arising today.

As noted in the System Drivers Chapter, there are many challenges to scaling and migration of AMS designs. These challenges include decreasing supply voltages, increasing relative parametric variations, increasing numbers of analog transistors per chip, increasing signal, clock and intrinsic device speeds, increasing leakage and crosstalk in SOC integration, and a shortage of design skills and automation. Particular challenges include 1) deep submicron effects and higher signal and clock frequencies: even "digital goes to analog," increasing role of parasitics, transmission line effects, and signal integrity; 2) analog synthesis tools to reduce effort spent on analog circuit design by a limited number of analog designers; 3) yield enhancement which requires "design for manufacturing"; 4) close integration of signal processing systems (mostly digital) and analog RF front ends in almost all mobile communication devices; and 5) tight integration of electrical and non-electrical components (such as micro-electro-mechanical systems (MEMS)). These challenges may be elaborated in the context of traditional DT areas, as follows.

In System-Level Design, the critical AMS challenges are non-scalability of analog circuits and analog behavioral modeling and synthesis. Automated analog circuit synthesis and optimization is needed, along with language-level modeling methodologies that permit analysis of overall system function and interfaces with other integrated technologies

(digital, software). Issues include coping with vastly varying time scales (analog frequencies up to 100s of GHz versus digital frequencies up to 1s of GHz) in simulation; creating heterogeneous test benches and ensuring coverage; achieving systematic top-down constraint propagation; and mixing of functional and structural representations.

In Logical, Physical and Circuit Design, the key challenge is *analog synthesis*. Scalable SOC design requires elimination of the analog design bottleneck. A technology need shared with system-level design is for reusable, retargetable analog IP generators. Today's specialized automatic *circuit* syntheses for particular classes of circuits (PLL, op-amp, power amplifier, etc.) must be augmented by more general techniques. Automatic *layout* syntheses must be able to handle the needs for high-performance analog designs (e.g., cross-coupled layout for mismatch sensitive transistors). Analog post-layout simulation must handle increased opportunities for distortion and nonlinearity due to impact ionization, thermal nonlinearity, body contacts acting as low-pass filters, etc. Syntheses must also handle future regimes of increased manufacturing variability, such as by hybrid analog-digital compensation for device mismatch. In the near term, new synthesis tools for optical interface circuits and high-Q CMOS on-chip inductors and tunable resonators are needed. Circuit types of interest in the long term include extremely low-power sensing and sensor interface circuits, as well as micro-optical (beam-steering) devices.

In Design Verification, AMS circuits require checking "to specification" rather than with respect to structure. While ever-faster simulation has been the historical solution, new verification solutions must include *statistical techniques*, better *compact models* that speed up simulation even increasing accuracy, and new *acceptance criteria*. AMS designs also force the long-term issue of *hybrid-systems verification*—a field still in its infancy—into the near term. Thus, an immediate challenge is to provide any support possible to improve the current ad hoc approaches and find a path toward more powerful techniques. As MEMS, electro-optic, and electro-biological devices become more than simple transducers, a further challenge is to model, analyze and verify integrated systems having such heterogeneous parts.

Finally, with respect to Design Test, analog circuitry dominates production test cost despite being a small fraction of the total area of mixed-signal SOCs. The ratio of analog testing cost to total mixed-signal product cost will continue to increase unless changes to analog testing are made. The near-term requirement is for *analog/mixed-signal DFT/BIST*, *especially at higher resolution and/or higher frequencies beyond baseband*. Test techniques for on-chip, high-resolution (>14-16 bits) ADC and high-speed (>1-5GHz) RF components must be not only cost-effective, but also nonintrusive, i.e., they must not degrade performance of embedded analog blocks. Since high-resolution ADCs are usually constructed with multiple stages connected in serial or mash configuration, one possible direction is to utilize this structural knowledge in developing a DFT or self-test strategy.

Although the PIDS Chapter specifies an analog CMOS transistor that has a higher analog supply voltage and is unscaled across 2–3 technology nodes, this does not solve critical cost issues of power, process compatibility, area efficiency, design complexity, or verification and test. Furthermore, AMS design productivity remains a key challenge to development of new mixed-signal parts. A near-term roadmap for AMS DT includes new description languages as well as tools for:

- system exploration

- circuit synthesis and sizing

- schematic validation

- design for manufacturing

- analog/RF layout synthesis

- parasitics extraction, modeling, and simulation and

- analog IP encapsulation and reuse

The following table summarizes near-term AMS design technology breakthroughs expected through 2007. The reader is also referred to the excellent and detailed discussion of AMS DT requirements in the March 2002 *MEDEA+ Design Automation Roadmap*.

Table 13 Near-term Breakthroughs in Design Technology for AMS

| Field Of Breakthrough     | 2003                                  | 2004–2005              | 2006–2007                                 |  |

|---------------------------|---------------------------------------|------------------------|-------------------------------------------|--|

| Specification, validation | Mixed-signal description<br>languages | Multi-language support | Complete specification-driven design flow |  |

| Architectural design      | Algorithm-oriented design             | Language-based         | Synthesizable AMS                         |  |

|                                            |                              | performance evaluation                   | description                                      |

|--------------------------------------------|------------------------------|------------------------------------------|--------------------------------------------------|

| Mixed A/D and RF physical design           | Procedural layout generation | Design centering, performance estimation | Constraint-driven synthesis: behavior to layout  |

| Parasitic extraction, modeling, simulation | EMI simulation               | 2D/3D modeling,<br>order reduction       | Fault-tolerant circuit architectures, robustness |

# **DESIGN PROCESS**

The process of designing and implementing a chip requires a large collection of *techniques*, or *tools*, and an effective *methodology* by which a designer's input predictably leads to a manufacturable product. While considerable attention is given to the tools needed, the equally important subject of design methodology is often neglected. Each technology node requires designers to consider more issues; hence, new analysis methods and tools must be developed to evaluate new phenomena and aid the designer in making critical design decisions. Even more difficult is determining the most effective sequence in which issues should be considered, and design decisions made, in order to minimize iterations. Four major trends govern future leading-edge chip design processes and their supporting design system structures.

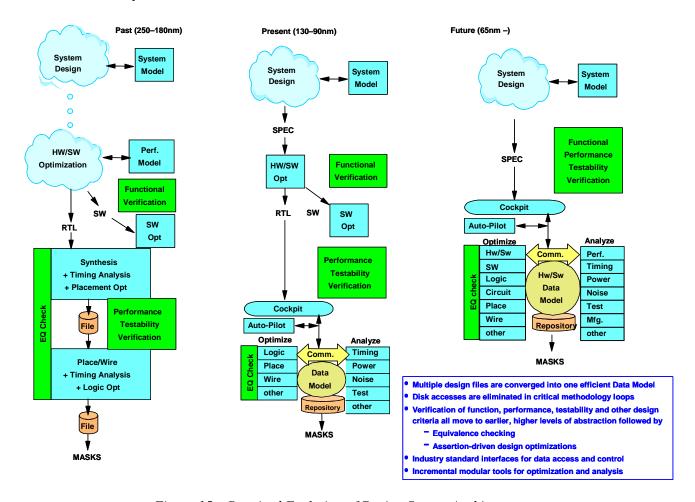

Trend 1: Tight coupling—Design processes that formerly comprised series of batch tools operating from files are evolving into collections of modular applications that operate concurrently and share design data in memory. In modern methodologies, optimization loops can no longer contain slow file accesses, and the plethora of design issues requires simultaneous optimization of multiple criteria. This trend was described in the 1999 ITRS and is visible today in most commercial design systems, where logical optimizations are working together with placement, global routing and timing analysis to close timing on advanced chip designs. Further advances will be needed to avoid noise problems, minimize power dissipation and ensure manufacturability. Figure 15 illustrates this trend. The left column shows a hardware design process, typical of the mid-1990s, where synthesis, timing and some placement are combined to handle the impact of placement on wire delays and synthesis results. Some place and route systems of that era used limited logic changes to reduce routing congestion. The middle column illustrates today's design process, in which suites of analysis and optimization modules cooperate to produce a chip with acceptable performance, power, noise, and area while maintaining testability and manufacturability. The right column illustrates the required design system for the future, in which hardware and software are co-analyzed and co-optimized to achieve an acceptable system implementation.

Trend 2: Design for manufacture—Preparation of mask data for manufacturing is an increasingly critical part of the design process. Past "data prep" applications converted design data into information for mask making. Today, basic shapes that describe a design, along with added shapes that correct process distortions and enhance printability, are handed off to mask making via standard file formats. However, flaws in the current paradigm have caused exponential growth of manufacturing NRE cost. First, corrective shapes (RET, metal fill, etc.) are inserted without complete understanding of effects on the printed wafer or on mask cost; designs are hence "over-corrected." New characterizations of manufacturing process and cost trade-offs are needed to enable more intelligent data preparation. Second, mask inspection and repair is the largest component of cost and delay in mask making, yet is also performed without insight into design intent. Effort is wasted in satisfying identical tolerances for every shape. A standard framework is needed to communicate criticality of design data to the mask making process, and feed manufacturing complexity back to the design process. Such bidirectional communication between design and manufacturing can help contain future costs of chip design and manufacture. Given the growth of mask and foundry outsourcing, this communication must be via an industry standard interface. Finally, new design and analysis tools that use manufacturing characteristics to optimize the design across all phases of the design cycle must work with enhanced manufacturing software to achieve design intent with minimum total cost. Figure 15 shows the influence of manufacturability, for example, previous wiring tools were successful in spacing apart wires to improve critical-area yield. Today there is greater focus on yield-driven layout, and manufacturability is a standard design criterion. In the 65 nm node and beyond, design and manufacturing data must be unified in a single database, so that designers can understand early on the impact on mask cost when making design tradeoffs, and so that manufacturing flows can understand design intent when applying yield- or cost-driven optimizations. In

\_

<sup>&</sup>lt;sup>3</sup> Design methodology is developed jointly by designers and design technologists; it is the sequence of steps by which a design process will reliably produce a design "as close as possible" to the design target while maintaining feasibility with respect to constraints. Design methodology is distinct from design techniques, which pertain to the implementation of the steps that comprise a methodology and are discussed below in the context of their respective DT areas. All known design methodologies combine 1) enforcement of system specifications and constraints via top-down planning and search, with 2) bottom-up propagation of constraints that stem from physical laws, limits of design and manufacturing technology, and system cost limits.

general, manufacturability will join power, performance and signal integrity as a first-class goal of future multi-objective design optimization.

Trend 3: Increasing level of abstraction—While some critical components are still crafted at the device level today, most design is at the gate-level for greater productivity, and register-transfer level (RTL) is used to specify design in a modern flow. Each advance in the level of abstraction requires tremendous innovation to discover the correct primitive concepts that form the basis of the abstraction, and to create the tools that allow trade-offs to be considered at this level, and map results to the next lower level. For continued improvements in designer productivity, an emerging system-level of design, well above RTL, is required.

Figure 15 Required Evolution of Design System Architecture

Higher levels of abstraction allow many forms of verification to be performed much earlier in the design process, reducing time to market and lowering cost by discovering problems earlier. Figure 15 illustrates this trend, with green verification boxes occurring earlier in the design process as DT advances. A finer-grain breakdown of this trend is as follows. 1) Functional verification used to begin when a gate-level implementation was available for simulation; early models were rarely complete or accurate. Today, functional verification can begin at the RT-level with Boolean equivalency checking of the later gate-level implementation. The result is accurate and provides more efficient, earlier functional verification. For future system-level abstraction, "transaction-level" modeling is emerging as a strong possibility, with equivalence checking via lower-level RTL descriptions still required. 2) Performance and timing verification confirm product performance as early as possible, allowing time for redesign. Early performance verification techniques based on mathematical or simulation models yielded early estimates, but required confirmation via later gate-level simulation. RTL modeling now provides earlier estimates, and system-level modeling will provide even earlier feedback (transaction-level models can provide early cycle-accurate performance estimates). While detailed timing analysis is always done at gate or transistor levels where device models are best understood, emergent RT- and system-level timing estimators promise valuable early feedback to designers, earlier in the design process. Tight coupling within design tool suites helps achieve the necessary predictability in meeting design constraints and gives designers more confidence that the RTL implementation process will meet early performance estimates. 4) Testability verification is yet another vital checkpoint in the design process. While this historically required a gate-level implementation, more sophisticated tools and self-test methods now permit a high level of confidence in a design's testability at the RT-level. Similar advances are required to provide confirmation at the system-level of abstraction in very early design stages.

Trend 4: Increasing level of automation—Historically, new levels of abstraction have been established primarily for more efficient simulation and verification of larger designs. However, once designers start to use the new models to specify design intent, opportunities arise for other tools such as synthesis. An important aspect of this trend is the replacement of designer guidance by constraint-driven optimization, so as to reduce the number of iterations in later process steps. Today's RTL design process emerged in this way, and a similar advance is needed at the system level. This trend is also visible in Figure 15. At the left, more comprehensive performance models emerge from what had been a very informal and indirect connection between initial system specification and automated RTL implementation. Executable system-level specification has matured in the current technology node, and in future nodes the system-level specification must include both software and hardware, and become the controlling representation for constraint-driven implementation. More detailed requirements for system-level DT, along with concrete flows that realize the progression of Figure 15, are given in the System-Level Design section, below.

<sup>&</sup>lt;sup>4</sup> In a transaction-level model, both data and time are abstracted. Atomic actions may take multiple cycles and complex data transfers may be represented with simple read and write commands.

Table 14 Design Process Challenges

| Challenges 50 nm/Through 2009      | Summary Of Issues                                         |  |  |

|------------------------------------|-----------------------------------------------------------|--|--|

| Silicon Complexity:                | All—Exponential increase in leakage power                 |  |  |

| devices and interconnects          | S, P, A—Power density and distribution                    |  |  |

|                                    | All—Technology and library characterization               |  |  |

|                                    | S, P, A—High-frequency noise analysis                     |  |  |

|                                    | S, P, A—Transmission-line interconnects                   |  |  |

|                                    | All—eDRAM, eFPGA, SiGe, optical, MEMS                     |  |  |

| System Complexity:                 | S, P—Verifying systems with exploding number of states    |  |  |

| number of states, design diversity | S, P, A—Concurrent multi-factor analysis and optimization |  |  |

|                                    | S, P—Scalable algorithms                                  |  |  |

|                                    | S, A—Design and test of mixed analog and digital designs  |  |  |

|                                    | All—Complex package analysis                              |  |  |

|                                    | S, A—Integrating A/D tools                                |  |  |

| Design Productivity                | S—Integrating third party components                      |  |  |

|                                    | S, P—Design tool interoperability                         |  |  |

|                                    | S, P—Early analysis and verification methods              |  |  |

| Time-to-Market                     | S, A—Support for platform-based design                    |  |  |

|                                    | S, P, A—Exploiting parallel processing                    |  |  |

| Challenges <50 nm/Beyond 2009      |                                                           |  |  |

| Manufacturability                  | All—Cross-chip variability                                |  |  |

|                                    | All—Sub-wavelength mask correction (AltPSM, OPC, RET)     |  |  |

|                                    | All—Design for yield and manufacturability                |  |  |

|                                    | All—Standards for sharing design and manufacturing data   |  |  |

| System-level Design                | S—Common hardware/software (HW/SW) representation         |  |  |

|                                    | S—SW synthesis, HW/SW optimization                        |  |  |

This table summarizes challenges to the design process advances implied by the above four trends. Each challenge is labeled with a list of the most relevant system drivers (S—system on chip, P—microprocessor, A—analog/mixed-signal, M—memory).

Table 14 summarizes challenges to the design process advances implied by the above four trends. Each challenge is labeled with a list of the most relevant system drivers (S = SOC, P = MPU, A = AMS, M = Memory). The remainder of this section gives explanatory comments.

# DESIGN PROCESS CHALLENGES—NEAR TERM (>50 nm)

- 1. Silicon Complexity—This refers to the "silicon complexity" challenges noted above, as well as the second through fifth crosscutting challenges. Potential solution approaches will entail restrictions on design rules (such as layout ground rules) as well as continued improvement in analyses (substrate coupling, crosstalk-induced timing, and IR drop, etc.).

- 2. System Complexity—Potential solution approaches seek increased capacity, use of hierarchical methods, and a higher abstraction level of design. Tool integrations must minimize unproductive data translation time and data redundancy, and support synthesis-analysis tool architectures that execute concurrently on distributed or SMP platforms (for die-packageboard codesign, manufacturability optimization, and power/noise management). Fundamental algorithms must be scalable, so that exponentially growing instance sizes remain effectively solvable on current computing hardware. Within a "construct by correction," successive approximation framework, incremental analyses and optimizations are needed with runtimes proportional to only the amount of design that changes between iterations. At the same time, shrinking feature size and pitch, coupled with increasing frequencies, demand increased levels of detail and accuracy within analysis models for delay, noise/interference, power, and reliability; hence, a broad spectrum of optimizations and analyses require increased awareness of the manufacturing process character. Such characterization must be provided via standard device technology and process specific models that will likely remain under control of that technology or process owner. Consistent interpretation of these models, such as via execution engines, is needed across the DT that uses these models. Finally, a complementary requirement at all levels of the design process is the identification of analysis abstractions and

macromodels that can serve as optimization objectives for upstream steps in the design process. A common data model and database must serve as much of the design flow as possible (certainly, from RTL to manufacturing data generation).

3. Productivity—Designer productivity will be improved through multi-level automation, increased reuse, and "freedom from choice." To systematically advance DT in this direction, the notion of design as "art" rather than "science" must be dispelled, and a mindset of "measure to improve" adopted. To develop methods for continuous design process and design productivity improvement, near-term technology needs begin with metrics of the design process with respect to quality and predictability. These in turn depend on metrics of design quality and design process predictability. Quality metrics assess the extent to which available manufacturing capability is fully exploited by DT. Predictability metrics enable quantified progress toward noise-free algorithms, tools and flows that are predictable and stable with respect to accepted solution metrics. Related needs include infrastructure for calibration and benchmarking. In addition, top-down design and rapid design space exploration require estimators of tool sweet spots ("field of use"), instance-specific tool runtime parameters, and tool output solution quality based on parameterized models of both tools and design instances. Eventually, predictive models of application- or driver-specific silicon implementation are needed. Finally, complementary innovations should measure and improve design technology productivity.

Today, the spectrum of design flows ranges from loosely coupled tools integrated via industry-standard sequential files to tightly integrated systems with closed/proprietary interfaces. In high-end design projects, no single DT vendor, nor the collection of all DT vendors together, provides the full scope of required DT. Hence, internally developed DT must augment multi-vendor design flows. High-end designs can also involve large, geographically distributed design teams from different companies. This mandates the need to share designs and reuse them across DT solutions. To facilitate this, needs include 1) an industry standard method to share design descriptions in real-time across disparate DT's and between design and manufacturing, and 2) industry adoption of this method across all DT solutions. There is a great need to reduce integration costs, currently estimated (Dataquest, 2001)<sup>8</sup> to be 30% of total design costs, and keep them from exceeding raw tool and machine costs while at the same time providing real-time DT interoperability in place of sequential DT data exchange. Improved tool reusability and interoperability, with reduced integration costs, will in the long term enable high-quality implementation flows for multiple platforms and applications (wireless, internetworking, etc.).

4. Time to Market—Obvious approaches to reduce time to market include use of reprogrammable and structured-ASIC fabrics, reuse of predesigned cores and "platform" architectures, and "pervasive automation." In many fast-growing semiconductor markets, the greatest demand is for low-cost, relatively low-performance, and fast time-to-market designs. Products in these markets are typically SOCs with heavy reuse. Addressing this demand requires common information models to describe the characteristics of reusable cores at levels of abstraction that permit efficient design optimization. New tools will be required to support a find-and-try style of reuse-centric design space exploration and design optimization. Development and formalization of design rules that, if followed, assure reusability will require associated design and analysis software to support and enforce such rules. As increasingly heterogeneous fabrics and technologies are integrated in a single SOC or SIP, new design flows must emerge that enable effective integration of hardware, software, digital and possibly analog, MEMS, and memory on a single chip. As already noted, AMS design is a productivity bottleneck that mandates improved ability to synthesize analog (and, in the long-term, mixed-technology) designs with

\_

<sup>&</sup>lt;sup>5</sup> Obvious metrics include speed, power and density relative to process geometry and supply voltage. Reusability, testability, verification coverage, etc. affect ROI of design and manufacturing technology investment, and should also be considered in formulating design quality metrics.

<sup>&</sup>lt;sup>6</sup> Inherent tool noise is the variation in solution quality that results from non-functional changes to the tool input (e.g., renaming variables or instances, permuting lines of a gate-level netlist, etc.). Recent literature measures inherent tool noise of 30% in commercial placement and routing tools; such levels block development of accurate estimation capability and must be reduced.

<sup>7</sup> Several recent studies estimate the worldwide population of design technology researchers and developers (including academics) to be approximately 6,000. Not only must this resource be carefully targeted for maximum impact, but DT productivity (i.e., technology delivery) must be improved. Example measures toward this end include understanding of DT impact on design productivity, and greater reuse of DT intellectual property.

<sup>&</sup>lt;sup>8</sup> Total design NRE cost is comprised of (1) designer and CAD support engineer salaries per unit time, multiplied by design time; (2) tool license cost per unit time, multiplied by design time; (3) machine and other infrastructure cost per unit time, multiplied by design time. "Interoperability cost" is reflected in increased design time (extra translation steps within the flow, and extra design iterations due to errors caused by lack of interoperability), increased CAD support salaries, and increased infrastructure cost (data storage and management). Design NRE cost, which is a function of design turnaround time (TAT) and per-unit time resource costs, should not be confused with design value, which is a function of time-to-market (and hence design TAT) and design quality. Only from knowledge of both design cost and design value can the ROI of design technology be determined. See the Design Cost analysis in the Appendix.

efficiency and quality comparable to digital RTL-based synthesis. Longer-term needs also include higher-level verification of function, performance and manufacturability, as well as supply-chain management and design processes that holistically minimize system implementation cost. The model for EDA may change so that specific platforms, application domains and even individual designs may require the building of customized, design-specific design flows out of interoperable components. This would change the focus of EDA as an industry from building complete flows to building composable parts with standardized interfaces.<sup>9</sup>

# DESIGN PROCESS CHALLENGES—LONG TERM (<50 nm)

- 1. Manufacturability—This refers to issues noted above with respect to the Manufacturing Integration cross-cutting challenge and the trend toward Design for Manufacturability. Potential solution approaches include restricted design rules as well as integrated design and manufacturability optimizations.

- 2. System-Level Design—At 65 nm and below, the transition to system-level design, along with unification of HW–SW design, cannot be avoided. The next section discusses system-level design technology requirements in detail.

# SYSTEM-LEVEL DESIGN

In system-level design<sup>10</sup>, methodological aspects are rapidly becoming much harder than tools aspects: enormous system complexity can be realized on a single die, but exploiting this potential reliably and cost-effectively will require a roughly 50× increase in design productivity over what is possible today. The context is daunting. Silicon complexities such as variability and reliability mean that highly reliable and available systems must be built out of heterogeneous, unreliable device and interconnect components. Global synchronization becomes prohibitively costly due to process variability and power dissipation, and cross-chip signaling can no longer be achieved in a single clock cycle. Thus, system design must comprehend networking and distributed computation metaphors (for example, with communications structures designed first and functional blocks then integrated into the communications backbone), as well as interactions between functional and interconnect pipelining. Furthermore, as emerging hardware platforms become increasingly fixed, embedded software becomes the main focus for product differentiation.

For decades, designers have reasoned about systems at various levels of abstraction (block diagrams, incomplete state charts, program models, etc.) with little support from design automation tools. This situation must change in the near future if necessary advances in productivity are to be achieved. To simplify the specification, verification and implementation of systems including hardware and software, and to enable more efficient design space exploration, a new level of abstraction is needed above the familiar register-transfer level. This will require the following advances along the above-noted trends of increased abstraction and increased automation.

• Reuse-based design in both HW and SW domains—Reusable, high-level functional blocks ("cores" or intellectual-property (IP) blocks) offer the potential for productivity gains that are estimated to be at least 200% (compare to "Very Large Block Reuse" in the Design Cost Model appendix). Pre-verification and reusable tests reduce design complexity, and libraries of reusable software modules can speed embedded software development. Ideally, an SOC designer can rapidly assemble a set of cores into a complex, application-oriented architecture as easily as drawing a block diagram. In practice, some amount of new cores and software will typically be required in the system, somewhat slowing implementation. While reuse has been a requirement for several editions of the ITRS, it has not yet permeated the system design process. At the 90 nm to 65 nm transition, this requirement is critical.

<sup>&</sup>lt;sup>9</sup> Programmable platforms and embedded software-centered system-level design flows (see the System-Level Design section, below) may require highly specialized tools yet generate too few design starts to sustain today's EDA business model. In such a regime, a services-oriented business model for complex system design could emerge, wherein EDA companies (a) build tool and infrastructure pieces from which design systems can be created, then (b) in partnership with system design teams, create design-specific design systems in parallel with the system designs themselves.

At the system-level, silicon resources are defined in terms of abstract functions and blocks; design targets include software (embedded code in high level and assembly language, configuration data, etc.) and hardware (cores, hardwired circuits, busses, reconfigurable cells). "Hardware"(HW) corresponds to implemented circuit elements, and "software"(SW) corresponds to logical abstractions (instructions) of functions performed by hardware. Behavior and architecture are independent degrees of design freedom, with software and hardware being two components of architecture. The aggregate of behaviors defines the system function, while the aggregate of architecture blocks defines a system platform. Platform mapping from system functionality onto system architecture is at the heart of system-level design, and becomes more difficult with increased system complexity and heterogeneity (whether architectural or functional).

- Platform-based design—An extension of core-based design creates highly reusable groups of cores to form a complete hardware "platforms," further simplifying the SOC design process. With highly programmable platforms that include one or more programmable processor(s) and/or reconfigurable logic, derivative designs may be created without fabricating a new SOC. Platform customization for a particular SOC derivative then becomes a constrained form of design space exploration: the basic communications architecture and platform processor choices are fixed, and the design team is restricted to choosing certain customization parameters and optional IP from a library. Platform-based design also entails HW–SW partitioning, which decides the mapping of key processing tasks into either HW or SW, and which has major impact on system performance, energy consumption, on-chip communications bandwidth consumption, and other system figures of merit. Multi-processor systems require "SW–SW" partitioning and codesign, i.e., assignment of SW tasks to various processor options. While perhaps 80–95% of these decisions can be made a priori, particularly with platform-based or derivative SOCs, such codesign decisions usually made for a small number of functions that have critical impact

- System-level verification—Fundamental to raising the abstraction level is a single notation for system-level design. Several years of experimentation with C, C++, and Java variants has led to recent emergence of SystemC as a reasonable form for building interoperable system models of hardware and software for simulation. As noted in the Design Process section, transaction-level modeling shows promise for high-performance system simulation. Formal methods may be able to exploit this higher level of abstraction, allowing application to larger problems.

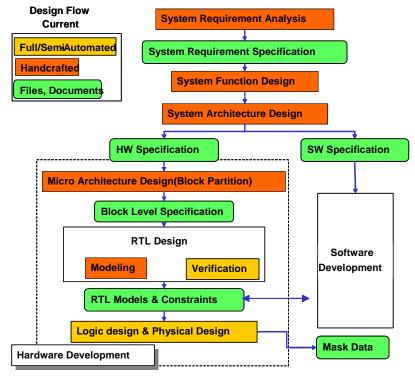

- *Micro-architecture synthesis*—As a standard form for system-level specification is adopted for simulation and verification, other tools will emerge. Although system synthesis is an extremely difficult task, progress can be envisioned according to a sequence of innovations. The first step will likely be automatic creation of an effective RTL specification from a slightly higher-level representation of the hardware in the form of a micro-architecture specification. Figures 16 and 17 illustrate this advance. Figure 16 shows a typical modern design flow (a realization of the left portion of Figure 15) with a mixture of manual steps above RTL and an automated process for RTL implementation. Figure 17 depicts a flow that is required in the near future (~2004); the manual process of mapping micro-architectural design decisions into RTL has been replaced with an automated step.

Figure 16 Current Design Flow

Figure 17 RTL Synthesis for Design Flow in year 2004

Figure 18 Design Flow in Year 2007

• *HW–SW co-synthesis*—The next required advance is the ability to concurrently synthesize a hardware and software implementation to achieve the best overall solution. Figure 18 shows the corresponding design flow, which is required circa 2007; the manual process of mapping a behavioral specification to a software program and a hardware micro-architecture has been replaced with an automated step. A form of HW–SW co-synthesis is "co-processor synthesis," in which software descriptions of algorithms are analyzed and automatically, or semi-automatically, divided into two parts: 1) a control structure which remains as SW running on a standard (on-chip) RISC processor, handling most of the control branching but only a relatively small amount of the computation, and 2) a data-processing/dataflow portion which is implemented in HW as co-processor(s) to complement the control SW. Due to the HW implementation, the latter part can reduce execution time of the overall application up to 90–95%, depending on the amount of control versus dataflow processing and the nature of the hardware fabric to which the data processing is mapped. Co-processor synthesis has already begun to appear commercially with some success, and remains the most likely form for HW–SW co-synthesis in the next several years. A key to the possibilities in this space is a unified (and software-based) representation of an application's implied processing, which can then be partitioned into HW and SW forms without undue manual effort.

Table 15 lists system-level design challenges and issues. The remainder of this section provides explanatory comments.

Table 15 System-level Design Challenges

| Challenges 50 nm/Through 2009             | Summary Of Issues                                                                                                                         |  |  |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| System complexity                         | S—Higher-level abstraction and specification                                                                                              |  |  |

|                                           | S—Dynamism and softness                                                                                                                   |  |  |

|                                           | S, A—System-level reuse                                                                                                                   |  |  |

|                                           | S, A, P—Design space exploration and system-level estimation                                                                              |  |  |

|                                           | S—Efficiency of behavioral synthesis and software compilation                                                                             |  |  |

|                                           | S—Automatic interface synthesis                                                                                                           |  |  |

| System power consumption                  | P, S—Energy-performance-flexibility trade-offs                                                                                            |  |  |

|                                           | P, S—Novel data transfer and storage techniques                                                                                           |  |  |

| Integration of heterogeneous technologies | S, P, A—Codesign (HW–SW, chip-package-board, fixed-reprogrammable)                                                                        |  |  |

|                                           | A, S—Non-scalability of analog circuits; analog behavioral modeling and synthesis                                                         |  |  |

|                                           | P, S, A—Top-down implementation planning with diverse fabrics (digital, AMS, RF, MEMS, EO, SW)                                            |  |  |

| Embedded software                         | S—SW–SW codesign onto highly programmable platforms                                                                                       |  |  |

|                                           | S—System capture and abstraction                                                                                                          |  |  |

|                                           | S—New automation from high level description to HW–SW implementations, including SW synthesis                                             |  |  |

|                                           | S—Formal verification for SW                                                                                                              |  |  |

|                                           | S—HW–SW coverification                                                                                                                    |  |  |

| Links to verification, test and culture   | S—Integration-oriented verification and test architectures                                                                                |  |  |

|                                           | S, P, A—Divergent design practices and cultures                                                                                           |  |  |

| Additional Challenges <50 nm/Beyond 2009  |                                                                                                                                           |  |  |

| System complexity                         | S, P—Communication-centric design and network-based communications on chip                                                                |  |  |

|                                           | All—Design robustness                                                                                                                     |  |  |

| System power consumption                  | P—Non-scaling of centrally organized architectures                                                                                        |  |  |

|                                           | S—Building large systems from heterogeneous SOCs                                                                                          |  |  |

| Integration of heterogeneous technologies | S—Total system integration including new integrated technologies (MEMS, electro-optical, electro-chemical, electro-biological or organic) |  |  |

This table summarizes challenges to the design process advances implied by the above four trends. Each challenge is labeled with a list of the most relevant system drivers (S—system on chip, P—microprocessor, A—analog/mixed-signal, M—memory).

# System-level Design Challenges—Near Term (>50 nm)

1. System complexity—System complexity and design productivity challenges induce the following technology needs.

- *Higher-level abstraction and specification*—Design abstraction levels must be raised above the present-day RT-level for HW and (often processor-dependent) C code level for embedded SW. Models of intended system function in the operating environment, and of both processing and communicating architectural resources, are necessary for design space exploration for complex, multi-function systems. Emerging design language infrastructure for complex models (e.g., C++ derivatives such as SystemC) must be leveraged by industry consensus on use-methodology and abstraction levels.

- Dynamism and softness—Dynamism is a system property that enables the system to adapt at runtime under the influence of use requirements (such as multimedia quality of service). New abstractions are required for such runtime modification of function and architecture. Softness is a system property that enables a system to be modified or reprogrammed. While softness will apply at multiple abstraction levels, such as process, ISA, microarchitecture, and implementation, no methodology yet exists that enables designers to identify and select programmable features of a chip. Architectural innovation is needed to meet SOC opportunities and constraints, and to support such dynamic behavior/architecture.

- System-level reuse—While some progress has been made in RT- and layout-level design reuse, reuse methodologies and associated design tools (for example, for evaluation of IP quality and suitability) are still in their infancy. Design productivity impact requires the reuse of complex HW–SW architectures via methods such as platform-based design. Software reuse can require design methodologies for processors that run "standard" software but are specialized to different cost-performance trade-offs or computational domains.

- Design space exploration and system-level estimation—The increasing range of integratable implementation fabrics requires new tools for optimization of the function-architecture mapping. Criteria for such optimizations include power, area, throughput, etc. Estimation technology is a fundamental and yet-undeveloped adjunct of top-down design space exploration. Estimators allow accurate prediction of the eventual values of the design criteria without going through all details of the design process. Such a capability must increasingly span multiple levels of abstraction (timing estimation at physical, RTL, and system levels) as well as statistical modeling of specific application spaces.

- Efficient behavioral synthesis and SW compilation—To complement eventual reuse solutions, new synthesis methods are required. Automated mappings from function to architecture—behavioral synthesis for hardware, and compilation for software—have limited application today due to poor quality of results (such as inadequate exploitation of processor features and parallelism by compilers). Needs include acceptable synthesis quality for mixed control and dataflow, and retargetable SW compilers that automatically achieve high-quality results on a wide variety of instruction set architectures (control processing and DSP) and design domains.

- Automatic interface synthesis—To better match system constraints, interfaces between HW-HW, HW-SW and SW-SW must be synthesized (or standardized) instead of hand-designed or drawn from parameterized libraries. This is a natural adjunct to emerging communication-centric design approaches.

- 2. System power consumption—Several current processor architecture paradigms (always-on, monolithic processor; high-power VLIW and speculative techniques) will give way in the near term to more massive, heterogeneous parallelism. Effective trade-offs of energy, performance and flexibility must be predictable at the system-level, and will require such techniques as dynamic power control; flexible block shut-down and restart; dynamically variable on-chip voltage supplies; standards-controlled power management; and power-efficient use of reconfigurable logic. The main near-term levers for power consumption at the system level are data transfer, and memory architecture and hierarchy.

- 3. Integration of heterogeneous technologies—Making effective design choices across the range of available component technologies requires new approaches to heterogeneous modeling and codesign.

- Codesign—DT for partitioning and codesign, whether of HW–SW, analog-digital, fixed-reprogrammable, or die-package (-board), must be increasingly aware of cost and risk factors across the entire system development process.

Trade-offs and partitioning across analog-digital boundaries require compatible specification and functional modeling abstractions, as well as the ability to simulate all parts of a system within a single execution and analysis

.

<sup>&</sup>lt;sup>11</sup> Supporting infrastructure for IP reuse (IP certification and validation services, as well as IP protection mechanisms) is required.

- environment. More generally, design optimization must increasingly consider a device in its system context rather than as a standalone entity.

- *Top-down implementation planning with diverse fabrics*—With more integratable fabrics, there is increased need for a single hierarchical mixed-technology planning environment that links system-level objectives and constraints with fabric details (circuit topology, interfaces, and spatial embedding).

- 4. Embedded software (ESW)—Reuse- and SW-centric SOC design is increasingly partitioned into 1) the creation of programmable platforms by a team of hardware-centric and hardware-dependent software-centric designers, and 2) use of the platforms in derivative products by a team of applications and software-centric designers. The system platform (one can think of this as an application programmer's interface, or API) is the intermediate vehicle between the two design teams, and between application domain requirements and underlying silicon capability. For this context, key issues include the following:

- SW-SW codesign onto highly programmable platforms—A highly programmable, application domain-specific platform offers multiple implementation fabrics (SW running on possibly configurable control processors or DSPs, HW implemented with multi-mode dedicated function blocks, reconfigurable logic, etc.) and programmable interfacing resources (SW-SW, HW-HW and HW-SW) to a derivative design. With such softness at multiple levels (software, assembly code, bit streams, etc.) there is a need for "SW-SW codesign"—rapid, reliable and predictable mapping of functions onto programmable processing and communications resources to meet system timing and power constraints.

- System capture and abstraction—Systems are denoted within a variety of models of computation (MOCs), such as discrete event, static and dynamic dataflow, or continuous-time. Designers must be able to model system functional and communication requirements using implementation-independent executable notations that are "natural" for each domain or MOC. These models must be composable into correct, executable system specifications.

Additional technology needs for the SOC context include new automation (including SW synthesis) from high-level description to HW-SW implementations, formal verification for SW, and HW-SW coverification.

- 5. Links to verification, test and culture—Shifting the design focus from block creation to block reuse on SOC platforms has the following implications for verification, test and "cultural" aspects of DT.