# INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS

# 2003 Edition

# **EMERGING RESEARCH DEVICES**

THE ITRS IS DEVISED AND INTENDED FOR TECHNOLOGY ASSESSMENT ONLY AND IS WITHOUT REGARD TO ANY COMMERCIAL CONSIDERATIONS PERTAINING TO INDIVIDUAL PRODUCTS OR EQUIPMENT.

# TABLE OF CONTENTS

| Emerging Research Devices                                                                    | 1  |

|----------------------------------------------------------------------------------------------|----|

| Scope                                                                                        | 1  |

| Difficult Challenges                                                                         |    |

| Emerging Technology Sequence                                                                 |    |

| Emerging Research Devices                                                                    |    |

| Non-classical CMOS                                                                           |    |

| Introduction                                                                                 |    |

| Non-classical CMOS—Definition and Discussion of Table Entries                                | 3  |

| Non-classical CMOS—An Emerging Device Technology Roadmap Scenario                            | 9  |

| Memory Devices                                                                               | 15 |

| Introduction                                                                                 |    |

| Memory Taxonomy                                                                              |    |

| Memory Devices—Definition and Discussion of Table Entries                                    |    |

| Logic Devices                                                                                |    |

| Introduction                                                                                 |    |

| Logic Devices—Definition and Discussion of Table Entries                                     |    |

| Emerging Research Architectures                                                              |    |

| Introduction                                                                                 |    |

| Architectures—Definition and Discussion of Table Entries                                     |    |

| Fine-Grained Parallel Implementations in Nanoscale Cellular Arrays                           |    |

| Defect Tolerant Architecture Implementations.                                                |    |

| Biologically Inspired Architecture Implementations<br>Coherent Quantum Computing             |    |

|                                                                                              |    |

| Emerging Technologies—A Functional Comparison                                                |    |

| Introduction                                                                                 |    |

| Functional Parameterization and Comparison                                                   |    |

| Definition and Discussion of Table Entries                                                   |    |

| Emerging Technologies—A Critical Review                                                      |    |

| Introduction                                                                                 |    |

| Technologies beyond CMOS                                                                     |    |

| Overall Technology Requirements                                                              |    |

| Charge-based Nanoscale Devices                                                               |    |

| Alternate Logic-State-Variable Nanoscale Devices                                             |    |

| Potential Performance and Risk Assessment for Memory and Logic Devices<br>Relevance Criteria |    |

| Appendix MASTAR                                                                              |    |

|                                                                                              |    |

# LIST OF FIGURES

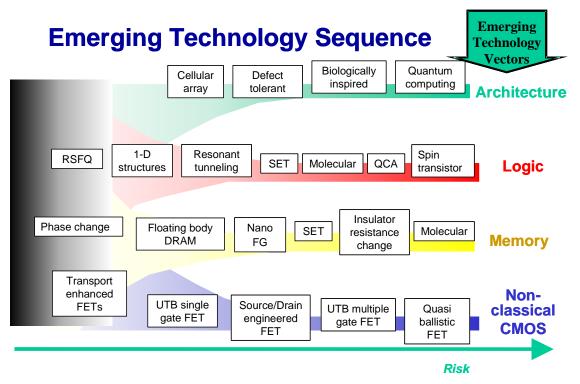

| Figure 38 | Emerging Technology Sequence                                                                                                | 3  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------|----|

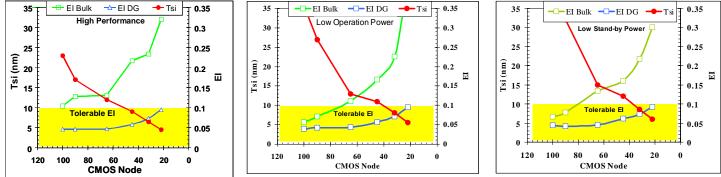

| Figure 39 | Estimation of Electrostatic Integrity (EI) for Bulk and Double-gate FETs                                                    | 11 |

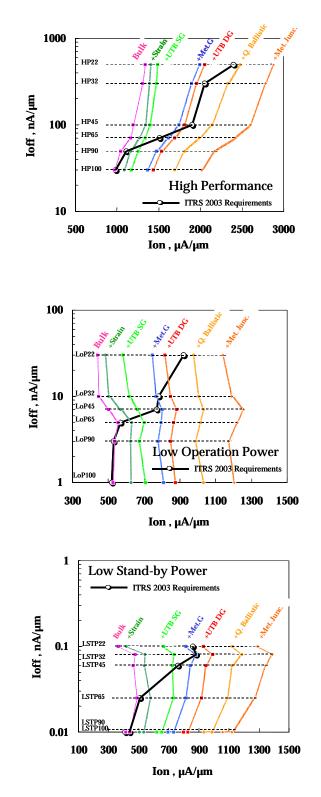

| Figure 40 | Impact of the Technology Boosters on HP, LOP, and LSTP<br>CMOS Roadmaps in Terms of I <sub>on</sub> :I <sub>off</sub> Ratio | 12 |

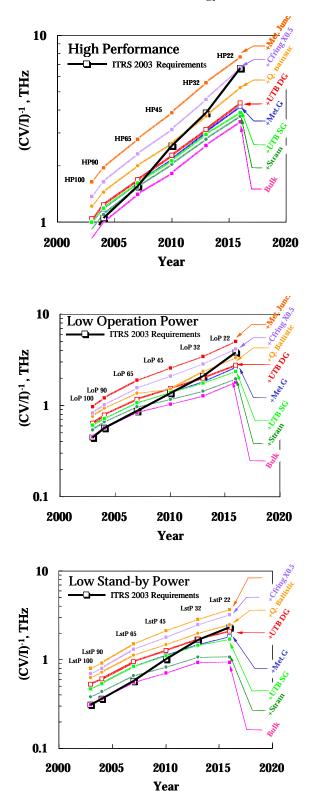

| Figure 41 | Impact of the Technology Boosters on HP, LOP, and LSTP<br>CMOS Roadmaps in Terms of Device Intrinsic Speed (f=1/(CV/I))     | 14 |

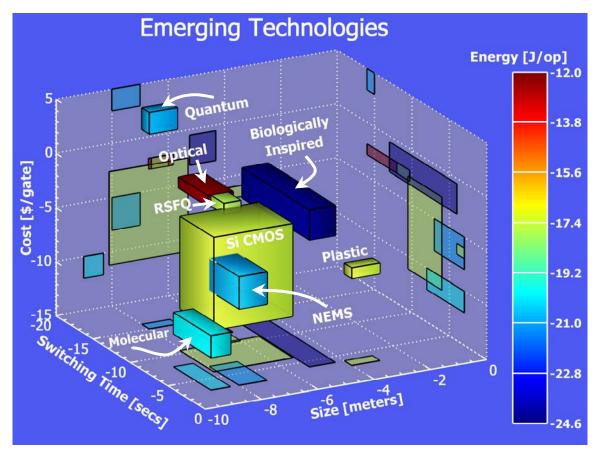

| Figure 42 | Parameterization of Emerging Technologies and CMOS—<br>Speed, Size, Cost, and Switching Energy                              | 41 |

# LIST OF TABLES

| Table 58  | Emerging Technologies Difficult Challenges                                                                      | 2  |

|-----------|-----------------------------------------------------------------------------------------------------------------|----|

| Table 59a | Single-gate Non-classical CMOS Technologies                                                                     | 4  |

| Table 59b | Multiple-gate Non-classical CMOS Technologies                                                                   | 5  |

| Table 60  | Technology Performance Boosters                                                                                 | 10 |

| Table 61  | Memory Taxonomy                                                                                                 | 16 |

| Table 62a | Emerging Research Memory Devices—Projected Parameters                                                           | 17 |

| Table 62b | Emerging Research Memory Devices—Experimental Parameters                                                        | 18 |

| Table 63a | Emerging Research Logic Devices—Projected Parameters                                                            | 23 |

| Table 63b | Emerging Research Logic Devices—Experimental Parameters                                                         | 25 |

| Table 64  | Emerging Research Architecture Implementations                                                                  | 38 |

| Table 65  | Estimated Parameters for Emerging Research Devices<br>and Technologies in the year 2016                         | 42 |

| Table 66  | Technology Performance and Risk Evaluation for<br>Emerging Research Memory Device Technologies (Potential/Risk) | 48 |

| Table 67  | Technology Performance and Risk Evaluation for<br>Emerging Research Logic Device Technologies (Potential/Risk)  | 48 |

# **EMERGING RESEARCH DEVICES**

# SCOPE

The quickening pace of MOSFET scaling is accelerating introduction of new technologies to extend CMOS beyond the 45 nm technology node. This acceleration simultaneously requires the industry to intensify research on two highly challenging thrusts. One is scaling CMOS into an increasingly difficult manufacturing domain well below the 90-nm node, and the other is an exciting opportunity to invent fundamentally new approaches to information and signal processing to sustain functional scaling beyond the domain of CMOS.

The primary goal of this section is to stimulate invention and research leading to feasibility demonstration for one or more Roadmap-extending concepts. This goal is accomplished by addressing the two technology-defining domains identified above—non-classical CMOS structures and memory technologies and completely new technological and architectural concepts for revolutionary Roadmap-extending information and signal processing applications. Technologies addressing CMOS scaling include both new materials and advanced MOSFET structures. The *Front End Processes* chapter discusses new materials required, for example, for the gate stack and for source/drain contacts. The *Process Integration*, *Devices, and Structures* chapter identifies technology requirements for CMOS structures to sustain performance and density scaling. Inclusion of a concept in this section does not in any way constitute advocacy or endorsement of that concept.

An important new theme of this section is to provide balanced technical assessments of leading approaches to nonclassical CMOS device technologies and new information and signal processing approaches. Furthermore, the content has been expanded to provide additional quantitative depth necessary to compare projected and current performance of several emerging new technologies. The intent is two-fold. First is to "cast a broad net" to gather in one place substantive, alternative concepts for memory, logic, and information processing architectures that would, if successful, substantially extend the Roadmap beyond CMOS. As such, this discussion will provide a window into candidate approaches. Second is to provide a balanced, critical assessment of these emerging new device technologies for information processing. This broadened section, therefore, provides an industry perspective on emerging new device technologies and serves as a bridge between bulk CMOS and the realm of microelectronics beyond the end of CMOS scaling.

The discussion is divided into the following four categories: 1) Non-classical CMOS, 2) Memory Devices, 3) Logic Devices and 4) information processing Architectures. The discussions provide some detail regarding their operation principles, advantages, challenges, maturity, and current and projected performance. Also included is a preliminary but interesting comparison of the performance projections and cost attributes for several speculative new approaches to information and signal processing. An interesting observation of this comparison is that the emerging devices, technologies, and architectures, given their successful development, would extend applications of microelectronics to domains not accessible to CMOS, rather than competing directly with CMOS in the same domain.

# **DIFFICULT CHALLENGES**

The microelectronics industry is facing two sets of difficult challenges related to extending integrated circuit technology to and beyond the end of CMOS scaling. One set of challenges relates to logic and the other relates to memory technologies. One difficult challenge related to logic in both the near- and the longer-term is to extend CMOS technology to and beyond the 45 nm node sustaining the historic annual increase of intrinsic speed of high-performance MPUs at 17%. This may require an unprecedented simultaneous introduction of two or more innovations to the device structure and/or gate-stack materials. Another longer-term challenge for logic is invention and reduction to practice of a new manufacturable information and signal processing technology addressing "beyond CMOS" applications. Solutions to the first may be critically important to extension of CMOS beyond the 45 nm node, and solutions to the latter could open opportunities for microelectronics beyond the end of CMOS scaling.

Another difficult challenge is the need of a new memory technology that combines the best features of current volatile and non-volatile memories in a fabrication technology compatible with CMOS process flow. This would provide a memory device fabrication technology required for both stand-alone and embedded memory applications. The ability of

an MPU to execute programs is limited by interaction between the processor and the memory, and scaling does not automatically solve this problem. The current evolutionary solution is to increase MPU cache memory, thereby increasing the floorspace that SRAM occupies on an MPU chip. This trend eventually leads to a decrease of the net information throughput. In addition, volatility of semiconductor memory requires external storage media with slow access (e.g., magnetic hard drives, optical CD, etc.). Therefore, development of *electrically accessible non-volatile* memory with *high speed* and *high density* would initiate a revolution in computer architecture. This development would provide a significant increase in information throughput even if traditional benefits of scaling were fully realized for nanoscale CMOS devices.

| Difficult Challenges≥45 nm/Through 2009                                                                                                                                                                                                                               | Summary of Issues                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Implementation into manufacturing of non-classical MOSFET device structures integrated with new materials and processes (for example, a strained silicon channel integrated with a new high- $\kappa$ gate dielectric material)                                       | Selection of most promising device structure(s) and/or materials<br>technologies ["Technology Booster(s)"] to sustain the required<br>annual 17% increase in performance<br>Introduction of two or more "Technology Booster" options<br>(material, process, and/or device structure changes)<br>simultaneously in a single node |

| Development and implementation into manufacturing of a<br>non-volatile memory technology combining the best<br>performance features of both volatile and non-volatile<br>memory technologies for both stand-alone and embedded<br>applications                        | Realization of a manufacturable, cost-effective fabrication<br>technology for electrically accessible high-speed, high-density<br>non-volatile RAM integrable with the fabrication process flow<br>for CMOS logic                                                                                                               |

| Difficult Challenges <45 nm/Beyond 2009                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                 |

| Toward the end of CMOS scaling or beyond, discovery,<br>reduction to practice, and implementation into<br>manufacturing of novel, non-CMOS devices and<br>architectures integrated (monolithically, mechanically, or<br>functionally) with a CMOS platform technology | Discovery and reduction to practice of new information processing<br>technologies integrable with silicon CMOS<br>Discovery and reduction to practice of new, low-cost methods of<br>manufacturing novel information processing technologies                                                                                    |

Table 58 Emerging Technologies Difficult Challenges

# **EMERGING TECHNOLOGY SEQUENCE**

Figure 38 shows an overview of the organization of the Emerging Research Devices section and illustrates the relationship of particular new concepts to the four functional categories that they each address—Non-classical CMOS, Memory, Logic, and Architectures. A category for Architectures is included to emphasize the point that because both new systems architectures and new device technologies will drive development of the other, synergistic/collaborative development of the two together can be very rewarding. This figure illustrates one simplified example of a richly diverse set of emerging application-specific concepts and technologies addressing different functions. It includes several highly speculative approaches. Many of these concepts likely will not mature to manufacturing or application. The important message here is that the emergence of many new ideas and technologies, several of which are suitable for only certain function(s) and do not have broad application, may be signaling a coming dispersion of microelectronics technologies to address an increasingly diverse set of market-driven applications. Integration of Systems on Chip (SoC) and in a package (SiP) at low cost and within a prescribed form factor will undoubtedly continue use of CMOS as the functional integration platform. This confluence of functions drives the need to integrate dissimilar technologies and functions in a high-performance, low-cost fashion with CMOS platforms.

Figure 38 Emerging Technology Sequence

# **EMERGING RESEARCH DEVICES**

# **NON-CLASSICAL CMOS**

### **INTRODUCTION**

Non-classical CMOS includes those advanced MOSFETs, shown in Tables 59a and 59b, which provide a path to scaling CMOS to the end of the Roadmap using new transistor structural designs and new materials. For digital applications, the scaling challenges include controlling leakage currents and short-channel effects; increasing saturation current while reducing the power supply; control of device parameters (e.g., threshold voltage, leakage) across the chip and from chip to chip. For analog/mixed-signal/RF applications, the challenges additionally include sustaining linearity, low noise figure, power-added-efficiency, and transistor matching. The industry and academic communities are pursuing two avenues to meeting these challenges—new transistor structures and new materials. New transistor structures seek to improve the electrostatics of the MOSFET; provide a platform for introduction of new materials; and accommodate the integration needs of new materials. New materials include those used in the gate stack (high- $\kappa$  dielectric and electrode materials), those used in the conducting channel that have improved carrier transport properties, as well as new materials used in the source/drain regions with reduced resistance and carrier injection properties. Additionally, the combination of new device structures and new materials enables new operating principles that may provide new behavior and functionality beyond the constraints of bulk planar or classical CMOS.

### NON-CLASSICAL CMOS—DEFINITION AND DISCUSSION OF TABLE ENTRIES

*Transport-enhanced FETs*—Improvements in transistor drive current for improved circuit performance can be achieved by enhancing the average velocity of carriers in the channel. Approaches to enhancing transport include mechanically straining the channel layer to enhance carrier mobility and saturation velocity, and employing alternative channel materials such as silicon-germanium, germanium, or III-V compound semiconductors with electron and hole mobilities and carrier velocities higher than those in silicon. A judicious choice of crystal orientation and current transport direction may also provide transport enhancement<sup>1</sup>. However, an important issue is how to fabricate transport enhanced channel layers (such as a strained Si layer) in several of the non-classical CMOS transistor structures (e.g., the multiple gate structures discussed in Table 59b).

<sup>&</sup>lt;sup>1</sup> S. Takagi, "Re-examination of Sub-band Structure Engineering in Ultra-short Channel MOSFETs under Ballistic Carrier Transport," VLSI Technology Symposium (2003) 115.

| Device                                                                              | Transport-enhanced<br>FETs                                                                                                                                                  | Ultra-thin Body SOI FETs                                                                                                                                                                 |                                                                                                                                                                                      | Source/Drain Engineered FETs                                                                                                                           |                                                                                                                         |  |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                     | Strained Si, Ge, SiGe<br>buried oxide ,<br>silicon Substrate                                                                                                                | BOX                                                                                                                                                                                      | FD Si film<br>D<br>Ground BOX (<20nm)<br>Plane Bulk wafer                                                                                                                            | Bias silicide<br>nFET pFET<br>Silicon Schottky barrier<br>isolation                                                                                    | S D<br>Nonoverlapped region                                                                                             |  |

| Concept                                                                             | Strained Si, Ge, SiGe,<br>SiGeC or other<br>semiconductor; on<br>bulk or SOI                                                                                                | Fully depleted SOI<br>with body thinner<br>than 10 nm                                                                                                                                    | Ultra-thin channel<br>and localized ultra-<br>thin BOX                                                                                                                               | Schottky<br>source/drain                                                                                                                               | Non-overlapped<br>S/D extensions on<br>bulk, SOI, or DG<br>devices                                                      |  |

| Application/Driver                                                                  | HP<br>CMOS                                                                                                                                                                  | HP, LOP, and<br>LSTP CMOS                                                                                                                                                                | HP, LOP, and<br>LSTP CMOS                                                                                                                                                            | HP<br>CMOS                                                                                                                                             | HP, LOP, and<br>LSTP CMOS                                                                                               |  |

| Advantages                                                                          | High mobility                                                                                                                                                               | <ul> <li>Improved<br/>subthreshold slope</li> <li>No floating body</li> <li>Potentially lower<br/>E<sub>eff</sub></li> </ul>                                                             | <ul> <li>SOI-like structure<br/>on bulk</li> <li>Shallow junction<br/>by geometry</li> <li>Junction<br/>silicidation as on<br/>bulk</li> <li>Improved S-slope<br/>and SCE</li> </ul> | <ul> <li>Low source/drain<br/>resistance</li> </ul>                                                                                                    | <ul> <li>Reduced SCE and<br/>DIBL</li> <li>Reduced parasitic<br/>gate capacitance</li> </ul>                            |  |

| Particular Strength                                                                 | High mobility<br>without change in<br>device architecture                                                                                                                   | <ul> <li>Low diode leakage</li> <li>Low junction<br/>capacitance</li> <li>No significant<br/>change in design<br/>with respect to<br/>bulk</li> </ul>                                    | <ul> <li>Quasi-DG<br/>operation due to<br/>ground plane effect<br/>enabled by the<br/>ultra thin BOX</li> <li>Bulk compatible</li> </ul>                                             | <ul> <li>No need for abrupt<br/>S/D doping or<br/>activation</li> </ul>                                                                                | <ul> <li>Very low gate<br/>capacitance</li> </ul>                                                                       |  |

| Potential Weakness                                                                  | <ul> <li>Material defects<br/>and diode leakage<br/>(only for bulk)</li> <li>Process<br/>compatibility and<br/>thermal budget</li> <li>Operating<br/>temperature</li> </ul> | <ul> <li>Very thin silicon<br/>required with low<br/>defect density</li> <li>V<sub>th</sub> adjustment<br/>difficult</li> <li>Selective epi<br/>required for<br/>elevated S/D</li> </ul> | <ul> <li>Ground plane<br/>capacitance</li> <li>Selective epi<br/>required for<br/>channel and S/D</li> </ul>                                                                         | <ul> <li>Ultra-thin SOI<br/>required</li> <li>NFET silicide<br/>material not readily<br/>available</li> <li>Parasitic potential<br/>barrier</li> </ul> | <ul> <li>High source/drain resistance</li> <li>Reliability</li> <li>Advantageous only for very short devices</li> </ul> |  |

| Scaling Issues                                                                      | Bandgap usually<br>smaller than Si                                                                                                                                          | Control of Si film<br>thickness                                                                                                                                                          | Process becomes<br>easier with Lg down-<br>scaling (shorter<br>tunnel)                                                                                                               | No particular scaling issue                                                                                                                            | Sensitivity to L <sub>g</sub><br>variation                                                                              |  |

| Design Challenges                                                                   | Compact model needed                                                                                                                                                        | None                                                                                                                                                                                     | None                                                                                                                                                                                 | Compact model needed                                                                                                                                   | Compact model needed                                                                                                    |  |

| Gain/Loss in Layout<br>compared to Bulk                                             | No difference                                                                                                                                                               | No difference                                                                                                                                                                            | No difference                                                                                                                                                                        | No difference                                                                                                                                          | No difference                                                                                                           |  |

| Impact on I <sub>on</sub> /I <sub>off</sub><br>compared to Bulk                     | <ul> <li>Improved by 20–30%</li> <li>(from MASTAR supposing µ<sub>eff</sub>X2)</li> </ul>                                                                                   | <ul> <li>Improved by<br/>15–20%</li> <li>(from MASTAR<br/>supposing E<sub>eff</sub>/2 and<br/>S=75mV/dec)</li> </ul>                                                                     | Improved by<br>15–20%<br>(from MASTAR<br>supposing E <sub>eff</sub> /2 and<br>S=75mV/dec)                                                                                            | <ul> <li>Improved by<br/>10–15%</li> <li>(from MASTAR<br/>supposing R<sub>series</sub>=0)</li> </ul>                                                   | <ul> <li>Both shifted to<br/>lower values</li> </ul>                                                                    |  |

| Impact on CV/I<br>compared to Bulk                                                  | <ul> <li>Lowered by<br/>15–20%</li> <li>(from MASTAR<br/>supposing µ<sub>eff</sub>X2)</li> </ul>                                                                            | <ul> <li>Lowered by<br/>10–15%</li> <li>(from MASTAR<br/>supposing Eeff/2 and<br/>S=75mV/dec)</li> </ul>                                                                                 | <ul> <li>Lowered by<br/>10–15%</li> <li>(from MASTAR<br/>supposing E<sub>eff</sub>/2 and<br/>S=75mV/dec)</li> </ul>                                                                  | <ul> <li>Lowered by<br/>10–15%</li> <li>(from MASTAR<br/>supposing R<sub>series</sub>=0)</li> </ul>                                                    | <ul> <li>Constancy or gain<br/>due to lower gate<br/>capacitance</li> </ul>                                             |  |

| Analog Suitability<br>G <sub>nt</sub> /G <sub>d</sub> advantage<br>compared to Bulk | Not clear                                                                                                                                                                   | Potential for slight<br>improvement                                                                                                                                                      | Potential for slight<br>improvement                                                                                                                                                  | Not clear                                                                                                                                              | Not clear                                                                                                               |  |

Table 59a Single-gate Non-classical CMOS Technologies

| Device                                                                                      |                                                                                           |                                                                                                                              | Multiple Gate FETs                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                |  |  |  |  |  |

|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                                                                             | N-Gate (N>2) FETs                                                                         | N-Gate (N>2) FETs Double-gate FETs                                                                                           |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                |  |  |  |  |  |

|                                                                                             | A STATE                                                                                   | Gate<br>Source Drain                                                                                                         | Source<br>Barbon<br>Bi-<br>Si-substrate<br>STI                                                                                       | to a spectra a s | Gate Gate<br>Drain                                                                                                                                             |  |  |  |  |  |

| Concept                                                                                     | Tied gates<br>(number of channels >2)                                                     | Tied gates,<br>side-wall conduction                                                                                          | Tied gates<br>planar conduction                                                                                                      | Independently<br>switched gates,<br>planar conduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Vertical conduction                                                                                                                                            |  |  |  |  |  |

| Application/<br>Driver                                                                      | HP, LOP, and LSTP<br>CMOS                                                                 | HP, LOP, and LSTP<br>CMOS                                                                                                    | HP, LOP, and LSTP<br>CMOS                                                                                                            | LOP and LSTP<br>CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | HP, LOP, and LSTP<br>CMOS                                                                                                                                      |  |  |  |  |  |

| Advantages                                                                                  | <ul> <li>Higher drive current</li> <li>2× thicker fin<br/>allowed</li> </ul>              | <ul> <li>Higher drive current</li> <li>Improved<br/>subthreshold slope</li> <li>Improved short<br/>channel effect</li> </ul> | <ul> <li>Higher drive current</li> <li>Improved<br/>subthreshold slope</li> <li>Improved short<br/>channel effect</li> </ul>         | Improved short<br>channel effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Potential for 3D     integration                                                                                                                               |  |  |  |  |  |

| Particular<br>Strength                                                                      | Thicker Si body     possible                                                              | Relatively easy process integration                                                                                          | <ul> <li>Process compatible<br/>with bulk and on bulk<br/>wafers</li> <li>Very good control of<br/>silicon film thickness</li> </ul> | Electrically<br>(statically or<br>dynamically)<br>adjustable<br>threshold voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <ul> <li>Lithography<br/>independent Lg</li> </ul>                                                                                                             |  |  |  |  |  |

| Potential<br>weakness                                                                       | <ul> <li>Limited device width</li> <li>Corner effect</li> </ul>                           | <ul> <li>Fin thickness less<br/>than the gate length</li> <li>Fin shape and aspect<br/>ratio</li> </ul>                      | <ul> <li>Width limited to<br/>&lt;1 µm</li> </ul>                                                                                    | <ul> <li>Difficult<br/>integration</li> <li>Back-gate<br/>capacitance</li> <li>Degraded<br/>subthreshold slope</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <ul> <li>Junction profiling<br/>difficult</li> <li>Process integration<br/>difficult</li> <li>Parasitic<br/>capacitance</li> <li>Single gate length</li> </ul> |  |  |  |  |  |

| Scaling<br>Issues                                                                           | <ul> <li>Sub-lithographic fin<br/>thickness required</li> </ul>                           | <ul> <li>Sub-lithographic fin<br/>thickness required</li> </ul>                                                              | <ul> <li>Bottom gate larger<br/>than top gate</li> </ul>                                                                             | <ul> <li>Gate alignment</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <ul> <li>Si vertical channel<br/>film thickness</li> </ul>                                                                                                     |  |  |  |  |  |

| Design<br>Challenges                                                                        | <ul> <li>Fin width<br/>discretization</li> </ul>                                          | <ul> <li>Fin width<br/>discretization</li> </ul>                                                                             | <ul> <li>Modified layout</li> </ul>                                                                                                  | <ul> <li>New device layout</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>New device layout</li> </ul>                                                                                                                          |  |  |  |  |  |

| Gain/Loss in<br>Layout<br>compared to<br>Bulk                                               | No difference                                                                             | No difference                                                                                                                | No difference                                                                                                                        | No difference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <ul> <li>Up to 30% gain in<br/>layout density</li> </ul>                                                                                                       |  |  |  |  |  |

| Advantage in<br>I <sub>on</sub> /I <sub>off</sub><br>compared to<br>Bulk                    | • Improved by 20–30%<br>(from MASTAR<br>assuming E <sub>eff</sub> /2 and<br>S=65V/decade) | • Improved by 20–30%<br>(from MASTAR<br>assuming E <sub>eff</sub> /2 and<br>S=65V/decade)                                    | • Improved by 20–30%<br>(from MASTAR<br>assuming E <sub>eff</sub> /2 and<br>S=65V/decade)                                            | Potential for<br>improvement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <ul> <li>Improved by<br/>20–30%</li> <li>(from MASTAR<br/>assuming E<sub>eff</sub>/2 and<br/>S=65V/decade)</li> </ul>                                          |  |  |  |  |  |

| Advantage in<br>CV/I<br>compared to<br>Bulk                                                 | • Lowered by 15–20%<br>(from MASTAR<br>assuming E <sub>eff</sub> /2 and<br>S=65V/decade)  | • Lowered by 15–20%<br>(from MASTAR<br>assuming E <sub>eff</sub> /2 and<br>S=65V/decade)                                     | • Lowered by 15–20%<br>(from MASTAR<br>assuming E <sub>eff</sub> /2 and<br>S=65V/decade)                                             | Potential for<br>improvement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Lowered by<br>15–20%<br>(from MASTAR<br>assuming E <sub>eff</sub> /2 and<br>S=65V/decade)                                                                      |  |  |  |  |  |

| Analog<br>Suitability<br>G <sub>m</sub> /G <sub>d</sub><br>advantage<br>compared to<br>Bulk | Potential for<br>improvement                                                              | <ul> <li>Potential for<br/>improvement</li> </ul>                                                                            | <ul> <li>Potential for<br/>improvement</li> </ul>                                                                                    | Potential for<br>improvement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Potential for<br>improvement                                                                                                                                   |  |  |  |  |  |

# Table 59b Multiple-gate Non-classical CMOS Technologies

#### References for Table 59a:

Transport-enhanced FETs / Strained Si, Ge, SiGe, SiGeC or other semiconductor; on bulk or SOI / HP CMOS:

- C. Chiu, "A sub-400 Degree C Germanium MOSFET Technology with High-k Dielectric and Metal Gate," IEDM (2002), 437–440.

- H. Shang, "High Mobility p-Channel Germanium MOSFETs with a Thin Ge Oxynitride Gate Dielectric," IEDM (2002), San Francisco, California.

- C.W. Leitz, "Hole Mobility Enhancements in Strained Si/Si/sub 1-y/Ge/sub y/ p-Type Metal-oxide-semiconductor Field-effect Transistors Grown on Relaxed Si/sub 1-x/Ge/sub x/ (x<y) Virtual Substrates," Applied Physics Letters, Vol. 79, No. 25, December 17, 2001.

- M. Lee, "Strained Ge Channel p-Type Metal-oxide-semiconductor Field-effect Transistor Grown on Si x Ge 1-x / Si Virtual Substrates," Applied Physics Letters, Vol. 79, No. 20, November 21, 2001.

- B.H. Lee, "Performance Enhancement on Sub-70 nm Strained Silicon SOI MOSFETs on Ultra Thin Thermally Mixed Strained Silicon/SiGe on Insulator (TM-SGOI) Substrate with Raised S/D," IEDM (December 11, 2002), San Francisco, California.

- T. Mizuno, "High Performance CMOS Operation of Strained-SOI MOSFETs Using Thin Film SiGe-on-Insulator Substrate," VLSI Technology Symposium (June 11–13, 2002), Honolulu, Hawaii.

- T. Tezuka, "High-performance Strained Si-on-Insulator MOSFETs by Novel Fabrication Processes Utilizing Ge-Condensation Technique," VLSI Technology Symposium (June 11–13, 2002), Honolulu, Hawaii.

- N. Collaert, "High-Performance Strained Si/SiGe pMOS Devices With Multiple Quantum Wells," IEEE Trans. Nanotechnology, Vol. 1, No. 4, December 2002, 190–194.

- T. Ernst, "A New Si:C Epitaxial Channel nMOSFET Architecture with Improved Drivability and Short-channel Characteristics," VLSI Technology Symposium, (June 10-12, 2003), Kyoto, Japan.

Qi Xiang, "Strained Silicon NMOS with Nickel-Silicide Metal Gate," VLSI Technology Symposium (June 10-12, 2003), Kyoto, Japan.

J.R. Hwang, "Performance of 70 nm Strained-Silicon CMOS Devices," VLSI Technology Symposium (June 10-12, 2003), Kyoto, Japan.

- T. Mizuno, "(110)-Surface Strained-SOI CMOS Devices with Higher Carrier Mobility," VLSI Technology Symposium (June 10-12, 2003), Kyoto, Japan.

- C.H. Huang, "Very Low Defects and High-performance Ge-On-Insulator p-MOSFETs with Al2O3 Gate Dielectrics," VLSI Technology Symposium (June 10-12, 2003), Kyoto, Japan.

#### Ultra-thin Body SOI FETs / Fully depleted SOI with body thinner than 10 nm / HP, LOP, and LSTP CMOS:

- B. Doris, "Extreme Scaling with Ultra-thin Si Channel MOSFETs," IEDM (December 8–11, 2002), San Francisco, California, 267–270.

- R. Chau, "A 50 nm Depleted-Substrate CMOS Transistor (DST)," IEDM (December 2–5, 2001), Washington, D.C, 621–624.

- H. VanMeer, "70 nm Fully-Depleted SOI CMOS Using a New Fabrication Scheme: The Spacer/Replacer Scheme," VLSI Symposium (June 11–13, 2002), Honolulu, Hawaii.

- T. Schultz, "Impact of Technology Parameters on Inverter Delay of UTB-SOI CMOS," SOI Conference, (October 7–10, 2002), Williamsburg, Virginia, 176–178.

- A. Vandooren, "Ultra-thin Body Fully-depleted SOI Devices with Metal Gate (TaSiN) Gate, High k (HfO2) Dielectric and Elevated Source/Drain Extensions," SOI Conference, (October 7–10, 2002), Williamsburg, Virgina, 205–206.

- B. Yu, "Scaling Towards 35 nm Gate Length CMOS," VSLI Symposium (June 12-14, 2001), Kyoto, Japan, 9-10.

- Y.K. Choi, "Ultra-thin Body PMOSFETs with Selectively Deposited Ge Source/Drain," VSLI symposium (June 12–14, 2001), Kyoto, Japan, 19–20.

- K. Uchida, "Experimental Study on Carrier Transport Mechanism in Ultrathin-body SOI n and p MOSFETs with SOI Thickness Less Than 5 nm," IEDM (December 8–11, 2002), San Francisco, California, 47–50.

#### <u>Ultra-thin Body SOI FETs / Ultra-thin channel and localized ultra-thin BOX / HP, LOP, and LSTP CMOS:</u>

- M. Jurczak, "SON (Silicon On Nothing) A New Device Architecture for the ULSI Era," Symp. VLSI Technology Proceedings, (June 1999), 29– 30.

- T. Skotnicki, "Heavily Doped and Extremely Shallow Junctions on Insulator by SONCTION (SilicON Cut-off Junction) Process," IEDM, (December 1999), 513–516.

- M. Jurczak, "SON (Silicon On Nothing) An Innovative Process for Advanced CMOS," IEEE Transactions on Electron Devices, (November 2000), 2179.

- S. Monfray, "First 80 nm SON (Silicon-On-Nothing) MOSFETs with Perfect Morphology and High Electrical Performance," IEDM, (December 2001), 645–648.

- S. Monfray, "SON (Silicon-On-Nothing) P-MOSFETs with Totally Silicided (CoSi<sub>2</sub>) Polysilicon on 5 nm-Thick Si-films: The Simplest Way to lintegration of Metal Gates on Thin FD Channels," IEDM, (December 2002), 263.

- S. Monfray, "Highly-performant 38 nm SON (Silicon-On-Nothing) P-MOSFETs with 9 nm-Thick Channels," IEEE SOI Conference Proceedings, (October 2002), 20.

- T. Sato, "SON (Silicon On Nothing) MOSFET using ESS (Empty Space in Silicon) Technique for SoC Applications," IEDM, (December 2001), 809.

#### Source/Drain Engineered FETs / Schottky source/drain / HP CMOS

- J. Kedzierski, "Complementary Silicide Source/Drain Thin-body MOSFETs for the 20 nm Gate Length Regime," IEDM (December 2002) San Francisco, California.

- R. Rishton, "New Complementary Metal-oxide Semiconductor Technology with Self-aligned Schottky Source/Drain and Low-resistance Tgates," Journal of Vacuum Science Technology, 1997, 2795–2798.

- J.P. Snyder, "Experimental Investigation of a PtSi Source and Drain Field Emission Transistor," Applied Physics Letters, Vol. 67, No. 10, September 4, 1995.

#### Source/Drain Engineered FETs // Non-overlapped S/D Extensions on Bulk, SOI, or DG devices // HP, LOP, and LSTP CMOS.

- F. Boeuf, "16 nm Planar NMOSFET Manufacturable within State-of-the-art CMOS Process Thanks to Specific Design and Optimization," IEDM, (December 2001), Washington, D.C., 637–640.

- H. Lee, "DC and AC Characteristics of Sub-50-nm MOSFETs with Source/Drain-to-gate Nonoverlapped Structure," IEEE Trans. Nanotechnology, Vol. 1, No. 4, December 2002, 219–225.

#### **References for Table 59b:**

#### Multiple-gate FETs / N-Gate (N>2) FET / Tied gates (number of channels >2) / HP, LOP, and LSTP CMOS

- R.Chau, "Advanced Depleted Substrate Transistor: Single-gate, Double-gate, and Tri-gate," Solid State Device Meeting (2002), 68-69. Fu-Liang Yang, "25 nm CMOS Omega FETs," IEDM (December 2002), 255.

- J. Colinge, "Silicon-on-insolator Gate-all-around Device," IEDM (December 1990), 595.

- B. Doyle, "Tri-gate Fully-depleted CMOS Transistors Fabrication, Design and Layout," VLSI (June 2003), 133.

- Z. Krivokapic, "High Performance 45 nm CMOS Technology with 20 nm Multi-gate Devices," SSDM (September 2003), 760.

#### Multiple-gate FETs | Double-gate FET | Tied-gates, side-wall conduction | HP, LOP, and LSTP CMOS

- Y.K. Choi, "FinFET Process Refinements for Improved Mobility and Gate Work Function Engineering," IEDM (December 2002), 259.

- J. Kedzierski, "Metal-gate FinFET and Fully-depleted SOI Devices Using Total Gate Silicidation," IEDM (December 2002), 247.

- B. Yu, "FinFET Scaling to 10 nm Gate Length," IEDM (December 2002), 251.

- T. Park, "Fabrication of Body-Tied FinFETS (Omega MOSFETS) Using Bulk Si Wafers," VLSI (June 2003), 135.

#### Multiple-gate FETs / Double-gate FET / Tied-gates, planar conduction / HP, LOP, and LSTP CMOS

- S. Monfray, "50 nm Gate All Around (GAA) Silicon On Nothing (SON) Devices: A Simple Way to Co-integration of GAA Transistors with Bulk MOSFET Process," VLSI (June 2002), 108.

- Lee, "A Manufacturable Multiple Gate Oxynitride Thickness Technology for System on a Chip," IEDM (December 1999), 71.

- H.S.P. Wong, "Self Aligned (top and bottom) Double-Gate MOSFET with a 25 nm Thick Silicon Channel," IEDM (December 1997), 427.

- G. Neudeck, "Novel Silicon Epitaxy for Advanced MOSFET Devices," IEDM (December 2000), 169.