# INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS

## 2003 Edition

## INTERCONNECT

THE ITRS IS DEVISED AND INTENDED FOR TECHNOLOGY ASSESSMENT ONLY AND IS WITHOUT REGARD TO ANY COMMERCIAL CONSIDERATIONS PERTAINING TO INDIVIDUAL PRODUCTS OR EQUIPMENT.

## TABLE OF CONTENTS

| Scope                                                        | . 1 |

|--------------------------------------------------------------|-----|

| Difficult Challenges                                         | . 2 |

| Technology Requirements                                      |     |

| Potential Solutions                                          | . 9 |

| Dielectric Potential Solutions                               |     |

| Pre-Metal Dielectric (PMD)                                   |     |

| Intra-Metal Dielectric (IMD)                                 |     |

| Hardmask                                                     |     |

| Etch Stop—Via<br>Etch Stop—Trench                            |     |

| DRAM                                                         |     |

| Conductor Potential Solutions                                |     |

| Barrier Potential Solutions                                  |     |

| Nucleation Potential Solutions                               |     |

| Planarization Potential Solutions                            |     |

| Etch Potential Solutions                                     |     |

| Interconnect Surface Preparation                             |     |

| Passive Devices.                                             |     |

| Introduction                                                 | .32 |

| MIM capacitors                                               | .32 |

| Inductors                                                    | .32 |

| Resistors                                                    | .33 |

| Reliability                                                  | 33  |

| Introduction                                                 | .33 |

| Cu/Low-κ issues                                              | .33 |

| Interfaces                                                   | .33 |

| Reliability Implications of Cu/low-κ Materials and Processes | .34 |

| Modeling and Simulation                                      | .34 |

| Future Reliability Directions                                | .34 |

| Systems and Performance Issues                               | 35  |

| Interconnect Performance                                     | 35  |

| System Level Integration                                     | .35 |

| New Interconnect Concepts                                    | 36  |

| Introduction                                                 | 36  |

| Packaging Intermediated Interconnects                        |     |

| Critical challenges                                          | .37 |

| 3D Interconnects<br>Critical challenges                      |     |

| RF and Microwave Interconnects.                       |    |

|-------------------------------------------------------|----|

| RF and Microwave Interconnects<br>Critical challenges | 37 |

| Optical Interconnects                                 | 37 |

| Critical challenges                                   |    |

| Guided TeraHz wave Interconnects                      | 38 |

| Critical challenges                                   |    |

| Radical Solutions                                     |    |

| Crosscut Issues                                       |    |

| Design, Modeling and Simulation                       | 39 |

| Assembly and Packaging                                | 40 |

| Metrology                                             |    |

| Yield Enhancement                                     | 40 |

| Environment, Safety, and Health                       | 41 |

| Impact of future emerging research devices            |    |

| Conclusion                                            |    |

## LIST OF FIGURES

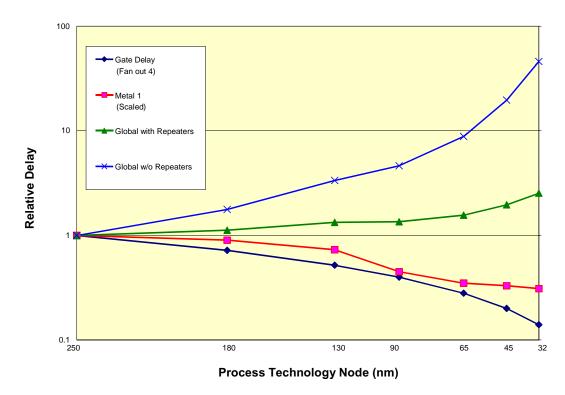

| Figure 54 | Delay for Metal 1 and Global Wiring versus Feature Size | 3  |

|-----------|---------------------------------------------------------|----|

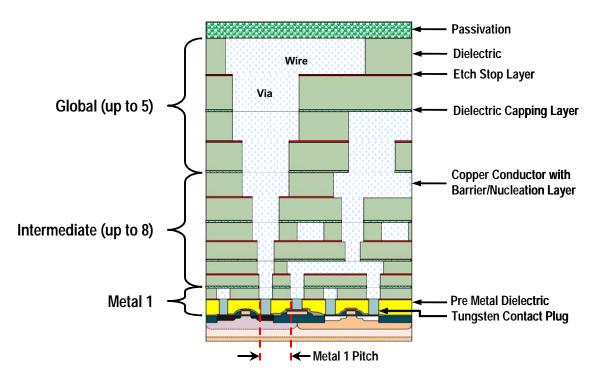

| Figure 55 | Cross-section of Hierarchical Scaling                   | 4  |

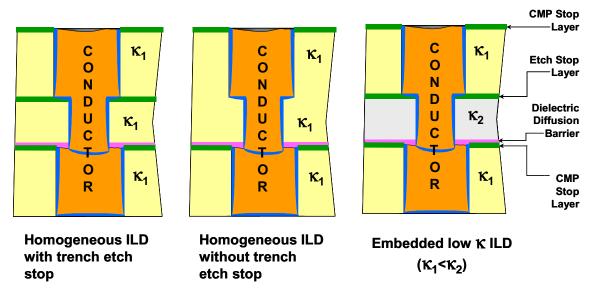

| Figure 56 | Typical ILD Architectures                               | 8  |

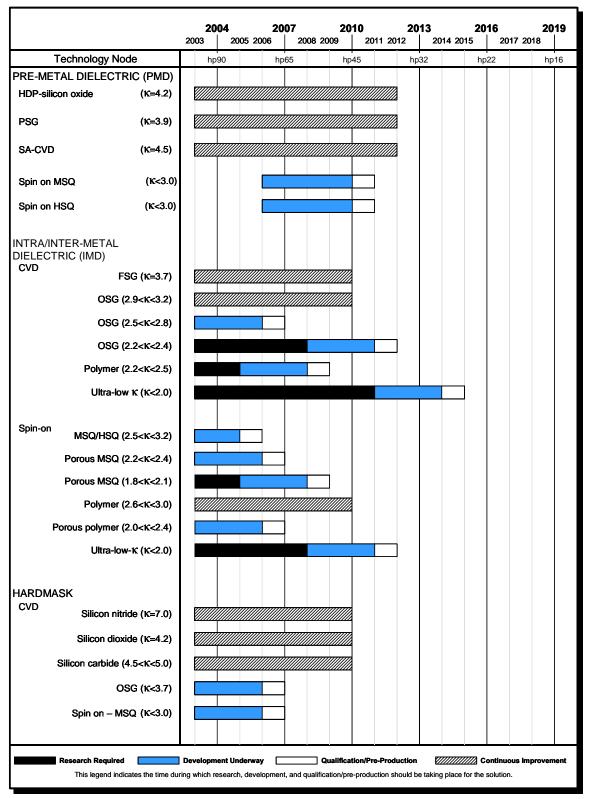

| Figure 57 | Dielectric Potential Solutions                          | 12 |

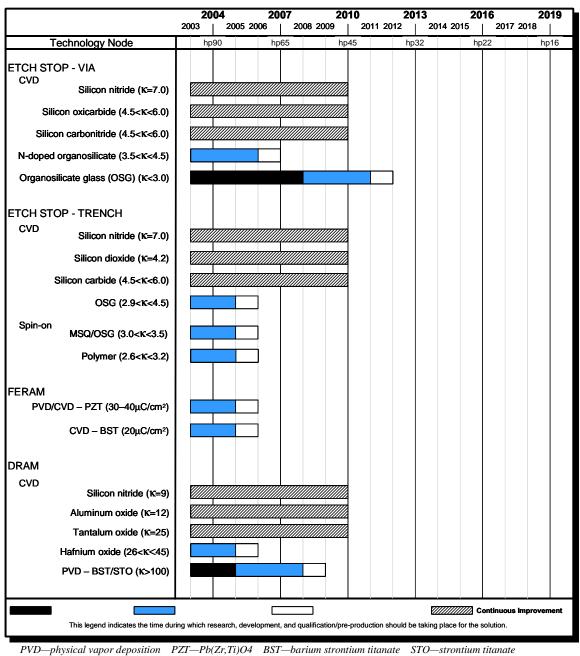

| Figure 58 | Conductor Potential Solutions                           | 15 |

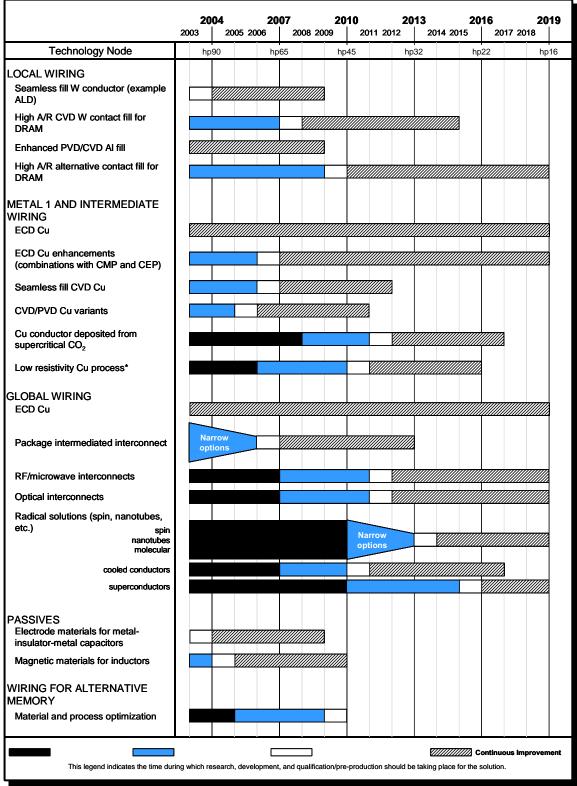

| Figure 59 | Barrier Potential Solutions                             | 17 |

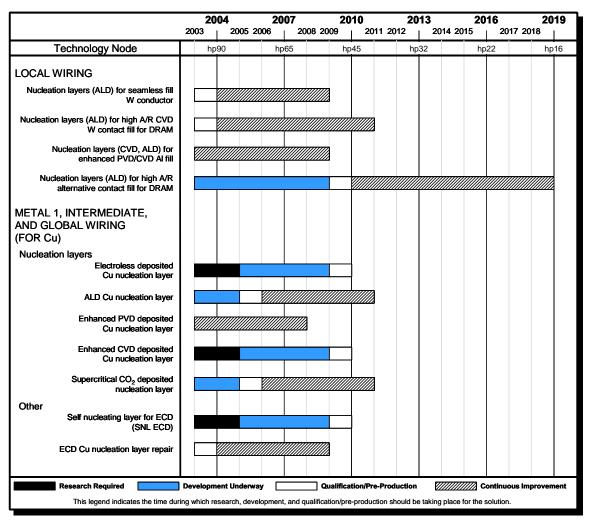

| Figure 60 | Nucleation Potential Solutions                          | 19 |

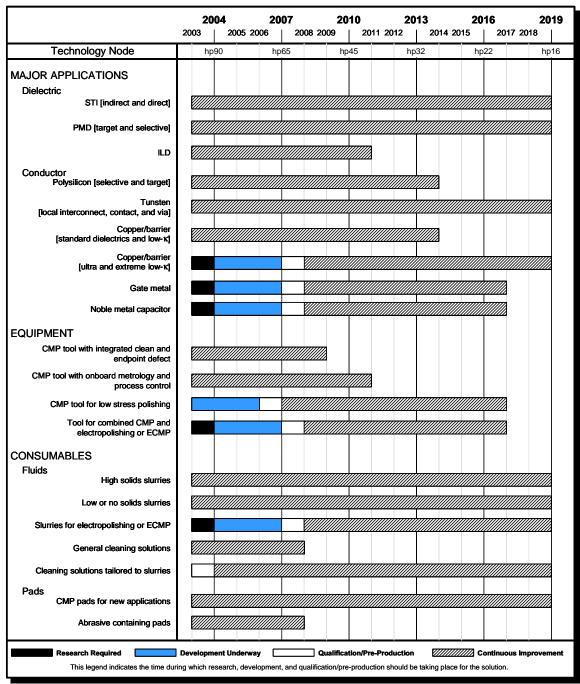

| Figure 61 | Planarization Potential Solutions                       | 22 |

| Figure 62 | Etch Schemes for Dual Damascene                         | 23 |

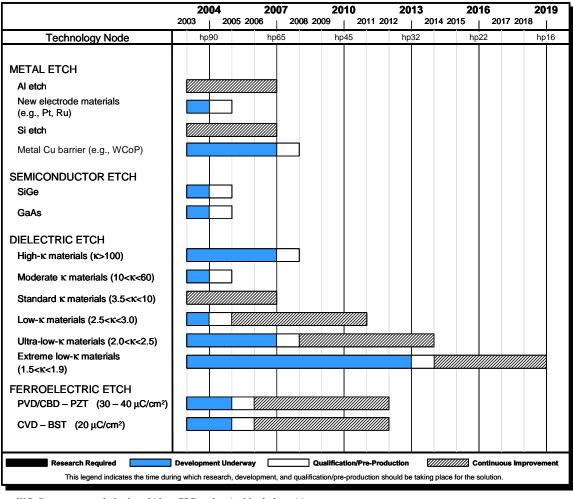

| Figure 63 | Etch Potential Solutions                                | 24 |

| Figure 64 | Interconnect Surface Preparation Potential Solutions    | 30 |

## LIST OF TABLES

| Table 80  | Interconnect Difficult Challenges                                       | 2  |

|-----------|-------------------------------------------------------------------------|----|

| Table 81a | MPU Interconnect Technology Requirements—Near-term                      | 5  |

| Table 81b | MPU Interconnect Technology Requirements—Long-term                      | 6  |

| Table 82a | DRAM Interconnect Technology Requirements—Near-term                     | 7  |

| Table 82b | DRAM Interconnect Technology Requirements—Long-term                     | 7  |

| Table 83a | Interconnect Surface Preparation Technology Requirements*—<br>Near-term | 26 |

| Table 83b | Interconnect Surface Preparation Technology Requirements*—<br>Long-term | 28 |

## INTERCONNECT

## SCOPE

The *Interconnect* chapter of the 1994 National Technology Roadmap for Semiconductors (NTRS) described the first needs for new conductor and dielectric materials that would be necessary to meet the projected overall technology requirements. With the publication of the 1997 edition of the NTRS, the introduction of copper-containing chips was imminent. The 1999 International Roadmap emphasized a continued change to new materials that were being introduced at an unprecedented pace. The 2001 ITRS described continued new materials introductions and highlighted the problem of increases in conductor resistivity as linewidths approach electron mean free paths. The slower than projected pace of low- $\kappa$  dielectric introduction for MPUs and ASICs is one of the central issues for the 2003 ITRS Interconnect area. The technical product driver for the smallest feature size remains the dynamic memory chip, however an emerging classification of chips, system-on-a-chip, or SoC, will challenge microprocessors for increased complexity and decreased design rules. Managing the rapid rate of materials introduction and the concomitant complexity represents the overall near-term challenge. For the long term, material innovation with traditional scaling will no longer satisfy performance requirements. Interconnect innovation with optical, RF, or vertical integration, combined with accelerated efforts in design and packaging will deliver the solution.

The function of an interconnect or wiring system is to distribute clock and other signals and to provide power/ground, to and among, the various circuits/systems functions on a chip. The fundamental development requirement for interconnect is to meet the high-speed transmission needs of chips despite further scaling of feature sizes.

Although copper-containing chips were introduced in 1998 with silicon dioxide insulators, the lowering of insulator dielectric constant predicted by the ITRS has been problematic. The reliability and yield issues associated with integration of these materials with dual-Damascene copper processing proved to be more challenging than predicted. Fluorine doped silicon dioxide ( $\kappa = 3.7$ ) was introduced at the 180 nm technology node, however insulating materials with  $\kappa = 2.6-3.0$  were not widely used at the 130 nm node. These materials are expected to be in use for the 90 nm technology node. The integration of these new low- $\kappa$  materials is rather time invariant,  $\kappa$  values will translate to lower technology nodes with any roadmap acceleration. The  $\kappa$  values of the bulk dielectric materials are defined in the dielectric potential solutions figure and the range of effective  $\kappa$  values for the integrated dielectric stack is listed in the technology requirements tables. (For a more thorough explanation, access the link to the *calculation of the effective . for various integration schemes .*) The introduction of these new low dielectric constant materials, along with the reduced thickness and higher conformality requirements for barriers and nucleation layers, is a difficult integration challenge.

The conductor, barrier, and nucleation potential solutions have been grouped into sections for local, Metal 1 and intermediate wiring levels, global wiring levels, as well as passive devices. Cu resistivity due to electron scattering effects will become an important factor in the long term, and is also an area of focus. Atomic layer deposition (ALD), characterized by excellent conformality and thickness control, is still receiving attention for applications in the deposition of conductors, barriers, nucleation layers and high- $\kappa$  dielectric materials. Links to *expanded references to ALD* are included as supplemental material.

Figure 63 covers etch and Figure 64 addresses strip and clean potential solutions, acknowledging the increased integration challenges of these steps. For example, the etch solution for a dual-Damascene structure with and without an embedded trench etch stop are different. Requirements for pre-etch and post-etch clean, which might utilize novel approaches such as super critical  $CO_2$  have been expanded.

Planarization potential solutions has now been split into sections for planarization of conductors and insulators. One of the primary integration challenges with low- $\kappa$  materials is adhesion failure between barrier or capping materials and the dielectric during planarization. Porous low- $\kappa$  materials are even more problematic and are therefore one of the key focus areas for planarization development efforts. A more detailed *schematic on the dishing/erosion/thinning metrics* shown in the technology requirements tables is found in the supplemental material link.

## **DIFFICULT CHALLENGES**

Table 80 highlights and differentiates the five key challenges in the near term ( $\geq 45$  nm) and long term (< 45 nm). In the near term, the most difficult challenge for interconnect is the introduction of new materials that meet conductivity requirements and reduce the dielectric permittivity. In the long term, the impact of size effects on interconnect structures must be migrated.

| Five Difficult Challenges<br>≥45 nm/Through 2009                                                                                                                           | Summary of Issues                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Introduction of new materials to meet<br>conductivity requirements and reduce the<br>dielectric permittivity*                                                              | The rapid introductions of new materials/processes that are necessary to meet conductivity requirements and reduce the dielectric permittivity create integration and material characterization challenges.                                                                                                                                                                                                                |

| Engineering manufacturable interconnect<br>structures compatible with new materials<br>and processes*                                                                      | Integration complexity, CMP damage, resist poisoning, dielectric constant degradation. Lack of interconnect/packaging architecture design optimization tool                                                                                                                                                                                                                                                                |

| Achieving necessary reliability                                                                                                                                            | New materials, structures, and processes create new chip reliability (electrical, thermal, and mechanical) exposure. Detecting, testing, modeling and control of failure mechanisms will be key.                                                                                                                                                                                                                           |

| Three-dimensional control (3D CD) of<br>interconnect features (with it's associated<br>metrology) is required to achieve necessary<br>circuit performance and reliability. | Line edge roughness, trench depth and profile, via shape, etch bias, thinning due to cleaning,<br>CMP effects. The multiplicity of levels combined with new materials, reduced feature size,<br>and pattern dependent processes create this challenge.                                                                                                                                                                     |

| Manufacturability and defect management<br>that meet overall cost/performance<br>requirements                                                                              | As feature sizes shrink, interconnect processes must be compatible with device roadmaps and meet manufacturing targets at the specified wafer size. Plasma damage, contamination, thermal budgets, cleaning of high A/R features, defect tolerant processes, elimination/reduction of control wafers are key concerns. Where appropriate, global wiring and packaging concerns will be addressed in an integrated fashion. |

| Five Difficult Challenges<br><45 nm/Beyond 2009                                                                                                                            | Summary of Issues                                                                                                                                                                                                                                                                                                                                                                                                          |

| Mitigate impact of size effects in interconnect structures                                                                                                                 | Line and via sidewall roughness, intersection of porous low-κ voids with sidewall, barrier roughness, and copper surface roughness will all adversely affect electron scattering in copper lines and cause increases in resistivity                                                                                                                                                                                        |

| Three-dimensional control (3D CD) of<br>interconnect features (with it's associated<br>metrology) is required                                                              | Line edge roughness, trench depth and profile, via shape, etch bias, thinning due to cleaning,<br>CMP effects. The multiplicity of levels, combined with new materials, reduced feature size<br>and pattern dependent processes, use of alternative memories, optical and RF interconnect,<br>continues to challenge.                                                                                                      |

| Patterning, cleaning, and filling at nano dimensions                                                                                                                       | As features shrink, etching, cleaning, and filling high aspect ratio structures will be challenging, especially for low-κ dual-Damascene metal structures and DRAM at nano dimensions.                                                                                                                                                                                                                                     |

| Integration of new processes and structures,<br>including interconnects for emerging<br>devices                                                                            | Combinations of materials and processes used to fabricate new structures create integration complexity. The increased number of levels exacerbate thermomechanical effects. Novel/active devices may be incorporated into the interconnect.                                                                                                                                                                                |

| Identify solutions which address global<br>wiring scaling issues*                                                                                                          | Traditional interconnect scaling will no longer satisfy performance requirements. Defining and finding solutions beyond copper and low $\kappa$ will require material innovation, combined with accelerated design, packaging and unconventional interconnect.                                                                                                                                                             |

Table 80 Interconnect Difficult Challenges

\* Top three challenges

Dimensional control is a key challenge for present and future interconnect technology generations. The dominant architecture, Damascene, requires tight control of pattern, etch and planarization. To extract maximum performance, interconnect structures cannot tolerate variability in profiles without producing undesirable RC degradation. These dimensional control requirements place new demands on high throughput imaging metrology for measurement of high aspect-ratio structures. New metrology techniques are also needed for in-line monitoring of adhesion and other micro structures, mechanical properties, ultra thin barriers and defects. Larger wafers and the need to limit test wafers will drive the adoption of more *in situ* process control techniques.

Dimensional control, a challenge now, will become even more critical as new materials, such as porous low- $\kappa$  dielectrics and CVD metals, play a role at the tighter pitches and higher aspect ratios (A/R) of intermediate and global levels. At the 45 nm node, feature size effects, such as electron surface scattering, will increase the effective resistivity and new conductor technologies may be required. Cu and low  $\kappa$  will continue to find applications in future chip generations, but

for global wiring, new interconnect solutions incorporating RF or optical propagation will be required, bringing even more material and process integration challenges.

#### **TECHNOLOGY REQUIREMENTS**

To adequately describe the wiring needs of interconnect, near term (2003–2009) and long term (2010–2018) technology requirements and potential solutions are addressed for two specific classes of products: high-performance microprocessors (HP MPU) and dynamic memory (DRAM [Tables 81–82]. For MPUs, Metal 1, intermediate, and global wiring pitches/aspect ratios are differentiated to highlight a hierarchical scaling methodology that has been broadly adopted.

Implementation of copper and low- $\kappa$  materials allows scaling of the intermediate wiring levels and minimizes the impact on wiring delay. Metal 1 wiring levels are relatively unaffected by traditional scaling. RC delay, however, is dominated by global interconnect and the benefit of materials changes alone is insufficient to meet overall performance requirements long-term. Figure 54 shows the delay of Metal 1 and global wiring in future generations. Repeaters can be incorporated to mitigate the delay in global wiring but consume power and chip area.

Figure 54 Delay for Metal 1 and Global Wiring versus Feature Size

As supply voltage is scaled and signal levels reduced, crosstalk has become an issue for all clock and signal wiring levels; the near term solution adopted by the industry is the use of thinner metallization to lower line-to-line capacitance. This approach is more effective for the lower resistivity copper metallization, where reduced aspect ratios can be achieved with less sacrifice in resistance as compared with aluminum metallization. The latter change expands the development timeframe to address the difficulty in integrating low- $\kappa$  dielectrics into a Damascene architecture. The 2003 Roadmap continues to reflect the design trend featuring reduced aspect ratios (as an alternative means of reducing capacitance) and less aggressive scaling of dielectric.

**Typical Chip Cross Section**

*Figure 55 Cross-section of Hierarchical Scaling*

Inductive effects will soon become increasingly important as frequency of operation increases, and additional metal patterns or ground planes may be required for inductive shielding.

To accommodate the need for ground planes or on-chip decoupling capacitors, the growth of metal levels is projected to increase beyond those specified solely to meet performance requirements. Refer to Tables 81a and b. More information regarding *optional levels* is provided through a link to supplemental files.

In the long term, new design or technology solutions (such as co-planar waveguides, free space RF, optical interconnect) will be needed to overcome the performance limitations of traditional interconnect.

| Year of Production                                                                                                          | 2003    | 2004    | 2005    | 2006    | 2007    | 2008    | 2009    |

|-----------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|

| Technology Node                                                                                                             |         | hp90    |         |         | hp65    |         |         |

| DRAM ½ Pitch (nm)                                                                                                           | 100     | 90      | 80      | 70      | 65      | 57      | 50      |

| MPU/ASIC ½ Pitch (nm)                                                                                                       | 120     | 107     | 95      | 85      | 76      | 67      | 60      |

| MPU Printed Gate Length (nm)                                                                                                | 65      | 53      | 45      | 40      | 35      | 32      | 28      |

| MPU Physical Gate Length (nm)                                                                                               | 45      | 37      | 32      | 28      | 25      | 22      | 20      |

| Number of metal levels                                                                                                      | 9       | 10      | 11      | 11      | 11      | 12      | 12      |

| Number of optional levels - ground planes/capacitors                                                                        | 4       | 4       | 4       | 4       | 4       | 4       | 4       |

| Total interconnect length (m/cm <sup>2</sup> ) – active wiring only, excluding global levels [1]                            | 579     | 688     | 907     | 1002    | 1117    | 1401    | 1559    |

| FITs/m length/cm <sup>2</sup> × 10 <sup>-3</sup> excluding global levels [2]                                                | 8.6     | 7.3     | 5.5     | 5.0     | 4.5     | 3.6     | 3.3     |

| Jmax (A/cm <sup>2</sup> ) – intermediate wire (at 105°C)                                                                    | 3.7E05  | 5.0E05  | 6.8E05  | 7.8E05  | 1.0E06  | 1.4E06  | 2.5E06  |

| Metal 1 wiring pitch (nm) *                                                                                                 | 240     | 214     | 190     | 170     | 152     | 134     | 120     |

| Metal 1 A/R (for Cu)                                                                                                        | 1.6     | 1.7     | 1.7     | 1.7     | 1.7     | 1.8     | 1.8     |

| Interconnect RC delay (ps) for 1 mm Metal 1 line                                                                            | 191     | 224     | 284     | 355     | 384     | 477     | 595     |

| Line length (mm) where $\tau = RC$ delay (Metal 1 wire)                                                                     | 79      | 65      | 55      | 46      | 41      | 34      | 28      |

| Cu thinning at minimum pitch due to erosion (nm), 10% $\times$ height, 50% areal density, 500 $\mu m$ square array          | 19      | 18      | 16      | 14      | 13      | 12      | 11      |

| Intermediate wiring pitch (nm)                                                                                              | 320     | 275     | 240     | 215     | 195     | 174     | 156     |

| Intermediate wiring dual Damascene A/R (Cu wire/via)                                                                        | 1.7/1.5 | 1.7/1.5 | 1.7/1.5 | 1.7/1.6 | 1.8/1.6 | 1.8/1.6 | 1.8/1.6 |

| Interconnect RC delay (ps) for 1 mm intermediate line                                                                       | 105     | 139     | 182     | 224     | 229     | 288     | 358     |

| Line length (mm) where $\tau = RC$ delay (intermediate wire)                                                                | 107     | 83      | 69      | 58      | 53      | 43      | 37      |

| Cu thinning at minimum intermediate pitch due to erosion (nm), $10\% \times$ height, 50% areal density, 500 µm square array | 27      | 23      | 20      | 18      | 18      | 15      | 10      |

| Minimum global wiring pitch (nm)                                                                                            | 475     | 410     | 360     | 320     | 290     | 260     | 234     |

| Ratio range (global wiring pitches/intermediate wiring pitch)                                                               | 1.5–5.0 | 1.5–6.7 | 1.5–6.7 | 1.5–6.7 | 1.5–8.0 | 1.5–8.0 | 1.5-8.0 |

| Global wiring dual Damascene A/R (Cu wire/via)                                                                              | 2.1/1.9 | 2.1/1.9 | 2.2/2.0 | 2.2/2.0 | 2.2/2.0 | 2.3/2.0 | 2.3/2.0 |

| Interconnect RC delay (ps) for 1 mm global line at minimum pitch                                                            | 42      | 55      | 69      | 87      | 92      | 112     | 139     |

| Line length (mm) where $\tau = RC$ delay (global wire at minimum pitch)                                                     | 169     | 132     | 112     | 93      | 83      | 69      | 59      |

| Cu thinning of maximum width global wiring due to dishing and erosion (nm), $10\% \times \text{height}$ , 80% areal density | 168     | 193     | 176     | 158     | 172     | 160     | 144     |

| Cu thinning global wiring due to dishing (nm), 100 µm wide feature                                                          | 30      | 29      | 24      | 21      | 19      | 17      | 15      |

| Conductor effective resistivity ( $\mu\Omega$ -cm) Cu intermediate wiring                                                   | 2.2     | 2.2     | 2.2     | 2.2     | 2.2     | 2.2     | 2.2     |

| Barrier/cladding thickness (for Cu intermediate wiring) (nm) [3]                                                            | 12      | 10      | 9       | 8       | 7       | 6       | 6       |

| Interlevel metal insulator (minimum expected) – effective dielectric constant $(\kappa)$                                    | 3.3–3.6 | 3.1–3.6 | 3.1–3.6 | 3.1–3.6 | 2.7–3.0 | 2.7–3.0 | 2.7–3.0 |

| Interlevel metal insulator (minimum expected) – bulk dielectric constant ( $\kappa$ )                                       | <3.0    | <2.7    | <2.7    | <2.7    | <2.4    | <2.4    | <2.4    |

Table 81a

MPU Interconnect Technology Requirements—Near-term

\*Refer to Executive Summary Figure 4 for definition of Metal 1 pitch

Manufacturable solutions exist, and are being optimized

Notes for Tables 81a and 81b:

[1] Calculated by assuming that only one of every three minimum pitch wiring tracks for local and semi-global wiring levels are populated. The wiring lengths for each level are then summed to calculate the total interconnect length per square centimeter of active area. [2] This metric is calculated by assuming that a 5 FIT reliability budget is apportioned to interconnect for the highest reliability grade MPUs. This number is then divided by the total interconnect length to arrive at the FITs per meter of wiring per one square centimeter of active area.

[3] Calculated for a conformal layer in intermediate wiring to meet minimum effective conductor resistivity.

|                                                                                                                             | <i>j</i> 110 <i>q</i> 111 | 00      | Long    |         |         |         |

|-----------------------------------------------------------------------------------------------------------------------------|---------------------------|---------|---------|---------|---------|---------|

| Year of Production                                                                                                          | 2010                      | 2012    | 2013    | 2015    | 2016    | 2018    |

| Technology Node                                                                                                             | hp45                      |         | hp32    |         | hp22    |         |

| DRAM ½ Pitch (nm)                                                                                                           | 45                        | 35      | 32      | 25      | 22      | 18      |

| MPU/ASIC ½ Pitch (nm)                                                                                                       | 54                        | 42      | 38      | 30      | 27      | 21      |

| MPU Printed Gate Length (nm)                                                                                                | 25                        | 20      | 18      | 14      | 13      | 10      |

| MPU Physical Gate Length (nm)                                                                                               | 18                        | 14      | 13      | 10      | 9       | 7       |

| Number of metal levels                                                                                                      | 12                        | 12      | 12      | 13      | 14      | 14      |

| Number of optional levels – ground planes/capacitors                                                                        | 4                         | 4       | 4       | 4       | 4       | 4       |

| Total interconnect length (m/cm <sup>2</sup> ) – active wiring only, excluding global levels [1]                            | 1784                      | 2214    | 2544    | 3544    | 4208    | 5035    |

| FITs/m length/cm <sup>2</sup> × 10 <sup>-3</sup> excluding global levels [2]                                                | 2.8                       | 2.3     | 2.0     | 1.4     | 1.2     | 1.0     |

| Jmax $(A/cm^2)$ – intermediate wire (at 105°C)                                                                              | 3.0E06                    | 3.7E06  | 4.3E06  | 5.1E06  | 5.8E06  | 6.9E06  |

| Metal 1 wiring pitch (nm) *                                                                                                 | 108                       | 84      | 76      | 60      | 54      | 42      |

| Metal 1 A/R (for Cu)                                                                                                        | 1.8                       | 1.8     | 1.9     | 1.9     | 2       | 2       |

| Interconnect RC delay (ps) for 1 mm Metal 1 line                                                                            | 616                       | 963     | 970     | 1510    | 2008    | 2679    |

| Line length (mm) where $\tau = RC$ delay (Metal 1 wire)                                                                     | 25                        | 18      | 15      | 11      | 9       | 6       |

| Cu thinning at minimum pitch due to erosion (nm), $10\% \times \text{height}$ , 50% areal density, 500 µm square array      | 10                        | 8       | 7       | 6       | 5       | 4       |

| Intermediate wiring pitch (nm)                                                                                              | 135                       | 110     | 95      | 78      | 65      | 55      |

| Intermediate wiring dual Damascene A/R (Cu wire/via)                                                                        | 1.8/1.6                   | 1.9/1.7 | 1.9/1.7 | 1.9/1.7 | 2.0/1.8 | 2.0/1.8 |

| Interconnect RC delay (ps) for 1 mm intermediate line                                                                       | 380                       | 552     | 614     | 908     | 1203    | 1582    |

| Line length (mm) where $\tau = RC$ delay (intermediate wire)                                                                | 32                        | 23      | 19      | 14      | 11      | 8       |

| Cu thinning at minimum intermediate pitch due to erosion (nm),<br>10% 'height, 50% areal density, 500 µm square array       | 12                        | 10      | 9       | 7       | 7       | 6       |

| Minimum global wiring pitch (nm)                                                                                            | 205                       | 165     | 140     | 117     | 100     | 83      |

| Ratio range (global wiring pitches/intermediate wiring pitch)                                                               | 1.5–10                    | 1.5–10  | 1.5–13  | 1.5–13  | 1.5–16  | 1.5–16  |

| Global wiring dual-Damascene A/R (Cu wire/via)                                                                              | 2.3/2.1                   | 2.3/2.1 | 2.4/2.2 | 2.4/2.2 | 2.5/2.3 | 2.5/2.3 |

| Interconnect RC delay (ps) for 1 mm global line at minimum pitch                                                            | 143                       | 220     | 248     | 354     | 452     | 618     |

| Line length (mm) where $\tau = RC$ delay (global wire at minimum pitch)                                                     | 52                        | 37      | 30      | 23      | 19      | 13      |

| Cu thinning of maximum width global wiring due to dishing and erosion (nm), $10\% \times \text{height}$ , 80% areal density | 155                       | 127     | 148     | 122     | 130     | 130     |

| Cu thinning global wiring due to dishing (nm), 100 µm wide feature                                                          | 14                        | 13      | 10      | 9       | 8       | 7       |

| Conductor effective resistivity ( $\mu\Omega$ -cm) Cu intermediate wiring                                                   | 2.2                       | 2.2     | 2.2     | 2.2     | 2.2     | 2.2     |

| Barrier/cladding thickness (for Cu intermediate wiring) (nm) [3]                                                            | 5                         | 4       | 3.5     | 3       | 2.5     | 2       |

| Interlevel metal insulator – effective dielectric constant ( $\kappa$ )                                                     | 2.3-2.6                   | 2.3-2.6 | 2.0-2.4 | 2.0-2.4 | <2.0    | <2.0    |

| Interlevel metal insulator (minimum expected) – bulk dielectric constant ( $\kappa$ )                                       | <2.1                      | <2.1    | <1.9    | <1.9    | <1.7    | <1.7    |

|                                                                                                                             |                           |         |         |         |         |         |

Table 81b MPU Interconnect Technology Requirements—Long-term

\*Refer to Executive Summary Figure 4 for definition of Metal 1 pitch

Manufacturable solutions exist, and are being optimized

Manufacturable solutions are known

Interim solutions are known

Manufacturable solutions are NOT known

#### Notes for Tables 81a and 81b:

[1] Calculated by assuming that only one of every three minimum pitch wiring tracks for local and semi-global wiring levels are populated. The wiring lengths for each level are then summed to calculate the total interconnect length per square centimeter of active area.

[2] This metric is calculated by assuming that a 5 FIT reliability budget is apportioned to interconnect for the highest reliability grade MPUs. This number is then divided by the total interconnect length to arrive at the FITs per meter of wiring per one square centimeter of active area. [3] Calculated for a conformal layer in intermediate wiring to meet minimum effective conductor resistivity.

| Year of Production                                                      | 2003     | 2004     | 2005     | 2006     | 2007     | 2008     | 2009     |

|-------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|

| Technology Node                                                         |          | hp90     |          |          | hp65     |          |          |

| DRAM ½ Pitch (nm)                                                       | 100      | 90       | 80       | 70       | 65       | 57       | 50       |

| MPU/ASIC <sup>1</sup> / <sub>2</sub> Pitch (nm)                         | 107      | 90       | 80       | 70       | 65       | 57       | 50       |

| MPU Printed Gate Length (nm)                                            | 65       | 53       | 45       | 40       | 35       | 32       | 28       |

| MPU Physical Gate Length (nm)                                           | 45       | 37       | 32       | 28       | 25       | 22       | 20       |

| Number of metal layers                                                  | 4        | 4        | 4        | 4        | 4        | 4        | 4        |

| Contact A/R – stacked capacitor                                         | 13       | 15       | 15       | 16       | 16       | 17       | 17       |

| Metal 1 wiring pitch (nm) *                                             | 180      | 160      | 140      | 130      | 114      | 100      | 90       |

| Specific contact resistance ( $\Omega$ -cm <sup>2</sup> )               | 1.00E-07 | 8.50E-08 | 7.00E-08 | 5.00E-08 | 4.00E-08 | 3.50E-08 | 3.00E-08 |

| Specific via resistance ( $\Omega$ -cm <sup>2</sup> )                   | 1.10E-09 | 9.00E-10 | 7.50E-10 | 5.80E-10 | 5.00E-10 | 4.00E-10 | 3.50E-10 |

| Conductor effective resistivity ( $\mu\Omega$ -cm)                      | 3.3      | 3.3      | 3.3      | 3.3      | 2.2      | 2.2      | 2.2      |

| Interlevel metal insulator – effective dielectric constant ( $\kappa$ ) | 3.6–4.1  | 3.6–4.1  | 3.6–4.1  | 3.6–4.1  | 3.1–3.6  | 3.1–3.6  | 3.1–3.6  |

Table 82a DRAM Interconnect Technology Requirements—Near-term

\*Refer to Executive Summary Figure 4 for definition of Metal 1 pitch

|                                                                         | 00111010 | 8, 1090  | in entern | 5 Long   | 5 101111 |          |

|-------------------------------------------------------------------------|----------|----------|-----------|----------|----------|----------|

| Year of Production                                                      | 2010     | 2012     | 2013      | 2015     | 2016     | 2018     |

| Technology Node                                                         | hp45     |          | hp32      |          | hp22     |          |

| DRAM ½ Pitch (nm)                                                       | 45       | 35       | 32        | 25       | 22       | 18       |

| MPU/ASIC ½ Pitch (nm)                                                   | 45       | 35       | 32        | 25       | 22       | 18       |

| MPU Printed Gate Length (nm)                                            | 25       | 20       | 18        | 14       | 13       | 10       |

| MPU Physical Gate Length (nm)                                           | 18       | 14       | 13        | 10       | 9        | 7        |

| Number of metal levels                                                  | 4        | 4        | 4         | 4        | 4        | 4        |

| Contact A/R – stacked capacitor                                         | >20      | >20      | >20       | >20      | >20      | >20      |

| Metal 1 wiring pitch (nm) *                                             | 80       | 64       | 57        | 44       | 40       | 32       |

| Specific contact resistance ( $\Omega$ -cm <sup>2</sup> )               | 2.30E-08 | 1.60E-08 | 1.20E-08  | 7.70E-09 | 5.50E-09 | 3.90E-09 |

| Specific via resistance ( $\Omega$ -cm <sup>2</sup> )                   | 3.20E-10 | 2.20E-10 | 1.60E-10  | 1.00E-10 | 7.60E-11 | 5.00E-11 |

| Conductor effective resistivity ( $\mu\Omega$ -cm)                      | 2.2      | 2.2      | 2.2       | 2.2      | 2.2      | 2.2      |

| Interlevel metal insulator – effective dielectric constant ( $\kappa$ ) | 2.7–3.1  | 2.7–3.1  | 2.7–3.1   | 2.7–3.1  | 2.0-2.4  | 2.0-2.4  |

Table 82b

DRAM Interconnect Technology Requirements—Long-term

\*Refer to Executive Summary Figure 4 for definition of Metal 1 pitch

Manufacturable solutions exist, and are being optimized

Manufacturable solutions are known

Interim solutions are known

Manufacturable solutions are NOT known

DRAM interconnect technology reflects the most aggressive metal pitch and highest aspect ratio contacts and will continue to provide the most significant challenges in dimensional control and defect management (refer to Table 82). The introduction of low- $\kappa$  dielectric materials (FSG) is underway and copper at the 65 nm ½ pitch is required to meet the performance of high-speed memory products. However, the pricing sensitivity of the marketplace may delay introduction if cost savings associated with copper are not realized. This suggests that capability for aluminum processing must be continuously improved and extended.

Damascene processing flows dominate MPU/ASIC fabrication methodologies and usage in DRAM is expected to broaden. Figure 56 illustrates several typical interlevel dielectric (ILD) architectures. While current copper Damascene

processes utilize physical vapor deposited (PVD) Ta-based barriers and Cu nucleation layers, continued scaling of feature size requires development of other materials and nucleation layer deposition solutions. Continuous improvement of tools and chemistries will extend electrochemically deposited (ECD) Cu to the 22 nm generation but small, high A/R features necessitate the simultaneous development and subsequent selection of alternative filling techniques. A thin barrier is also needed to maintain the effective conductor resistivity in these features. Nucleation layer conformality requirements become more stringent to enable Cu ECD filling of Damascene features. Surface segregated, CVD, ALD, and dielectric barriers represent intermediate potential solutions; zero thickness barriers are desirable but not required.

Near-term dielectric needs include lower permittivity materials for wire insulators and etch stops, higher permittivity materials for decoupling and metal insulator metal (MIM) capacitors and materials with high remanent polarization for ferroelectric memories. The thermal, mechanical, and electrical properties of these new materials present a formidable challenge for process integration. In the longer term, dielectric characteristics at high frequency will become more important, and optical materials will be required that have sufficient optical contrast to serve as low-loss waveguides.

Figure 56 Typical ILD Architectures

Continuous improvement in dielectric CMP and post-CMP defect reduction will be needed in the near term. The development of alternative planarization techniques is a potential long-term solution. For copper CMP, minimization of erosion and dishing will be necessary to meet performance needs as the wiring thickness is scaled. Planarization processes (with associated end-point) that are compatible with low- $\kappa$  dielectrics that may have low density and poor mechanical strength must be developed. Improvements in post-CMP clean will be critical in achieving the low defect densities required for future devices. Etch, resist strip, and post-etch cleans must be developed which maintain the desired selectivity to etch stop layers and diffusion barriers, but which do not degrade low- $\kappa$  dielectrics. Low or no device damage during etch and deposition processes is the goal, especially as thinner gate oxides and/or new gate dielectric materials are introduced.

## **POTENTIAL SOLUTIONS**

#### **DIELECTRIC POTENTIAL SOLUTIONS**

The previous ITRS documents have indicated a growing concern that the changes in the dielectric materials used through the 130 nm technology node are minor compared to the future technology needs and far more revolutionary in nature than the evolutionary path followed to date. This range of new dielectric material requirements encompasses both conventional and novel device architectures as well as almost every existing end use. Some dielectric materials are finding additional uses in alternate locations of the BEOL structure with new emphasis on required electrical, mechanical and processing properties. Even with new ever more stringent requirements for future technology nodes, the lifetime of the existing class of dielectric materials has been extended because of problems with the properties or integration of the new materials. The two most obvious and often cited examples are the delay in implementation of high- $\kappa$  materials for DRAM capacitor structures and the failure to achieve integration of true low- $\kappa$  ( $\kappa$ <3.0) interlayer dielectric (ILD) materials in large volume manufacturing.

The following three overall BEOL dielectric challenges remain valid throughout the 15-year scope of this roadmap:

- Development of true low- $\kappa$  materials and manufacturing processes capable of achieving the minimum effective permittivity ( $\kappa_{eff}$ ) possible, for maximum device performance at a viable performance/price ratio, for Cu dual-Damascene technology

- Development of moderate (κ>20) to high (κ>100) permittivity materials and manufacturing processes capable of achieving continually higher bit density at a viable bit/price ratio for stand-alone memory applications, decoupling and (MIM) capacitors for MPU/ASICs and system-on-a-chip (SoC).

- Sufficient development activity focused on invention and integration of new materials for emerging technologies to replace conventional wiring based electronics with alternatives, such as RF, optical and bio-based interconnect.

To address the range of dielectric material requirements and add focus to each specific application within the BEOL, which will encompass the dielectric requirements for Pre-Metal Dielectric (PMD) for the first time, the Dielectric Potential Solutions figure has been divided into applications instead of arbitrary groupings by dielectric permittivity.

#### PRE-METAL DIELECTRIC (PMD)

Improvements or changes in the technology used to deposit pre-metal dielectric (PMD) layers will be required. These changes will be driven by the move to NiSi, increases in the aspect ratios of spaces between adjacent gates in DRAMs and the simultaneous requirement for high phosphorous doping concentrations and low thermal budgets in NOR-type flash memories.

The increasing use of NiSi doped junctions and gate conductors in logic circuits will challenge those deposition technologies that require anneals above 450°C to 490°C. Thermal budget restrictions should also accompany the introduction of metal gates, however, these are likely to fall within the same range dictated by NiSi. This problem is intensified when high phosphorous doping concentrations are also required. Some NOR-type flash memories already incorporate NiSi while requiring PMD phosphorous concentrations as high as 10% to meet charge retention requirements. This could prove to be an insurmountable challenge for purely thermal deposition processes.

The aspect ratios of the spaces between adjacent gates in DRAMs are expected to reach 16:1 by 2005 and continue to increase thereafter. As a result, DRAM PMD deposition by plasma-based processes could become increasingly problematic. Plasma induced damage (PID) of thin gate dielectrics by plasma based PMD deposition processes has not proven to be a significant issue to date. However, it will continue to be an area of concern as gate dielectrics become thinner and/or are replaced by new high- $\kappa$  materials.

Finally, low- $\kappa$  dielectrics will be required for DRAMs for the layer incorporating bitlines in order to reduce capacitance. For example,  $\kappa_{eff}$  values ranging from 2.7 to 3.1 will be required by 2010, decreasing to 2.0 to 2.4 by 2018. It is conceivable that future PMD deposition processes will incorporate multiple steps, and possibly multiple process types, in order to satisfy the requirements of gap fill, thermal budget and doping concentration.

#### INTRA-METAL DIELECTRIC (IMD)

The introduction of FSG ( $\kappa$ =3.7) at the 180 nm technology node in conjunction with Cu dual-Damascene process integration represented the first major break in the historical extension of silicon dioxide ( $\kappa$ =4.1) and aluminum in the IC

industry. Although relatively minor in variation from silicon dioxide, issues of fluorine mobility, reactivity with refractory metal based barrier layers, adhesion and moisture sensitivity required the expenditure of significant engineering resource over a number of years to develop a truly robust manufacturing process.

The daunting task of implementing low- $\kappa$  interlayer dielectric materials ( $\kappa$ <3.0) has magnified these integration challenges by at least one or two orders of magnitude. Concurrent with this low- $\kappa$  materials introduction is a migration of metal barrier deposition technologies (PVD $\rightarrow$ CVD $\rightarrow$ ALD) as well as the continued reduction in barrier thickness to maintain the targeted Cu resistivity. The combination of these integration challenges, coupled with design improvements to alternately address projected cross-talk and RC delay problems, has resulted in an extension in the industry wide implementation of low- $\kappa$  ILD material past that proposed in the last three ITRS documents.

The preferred integration scheme for silicon-based dielectric materials continues to be the original "full-via-first" process implemented with silicon dioxide at the 250 nm node. Organic-based dielectric materials have usually adopted a dual inorganic hardmask scheme. In an effort to optimize performance and minimize integration complexity, organic/inorganic hybrid dielectrics have been discussed.

Many electrical simulation models exist to extrapolate these values from well-controlled test structures within a die. In the *supplemental file* simulation extraction results for representative low- $\kappa$  integration schemes are presented for several technology nodes. The model inputs are specific to the ITRS targets for layer thickness, aspect ratios and dielectric materials projected to be commercially available concurrent with proposed manufacturing ramp timings.

Several integration challenges associated with etch selectivity/damage, 193 nm photoresist, Cu CMP and packaging process compatibility are still areas of significant effort across almost all low- $\kappa$  dielectric materials. Historically derived material property relationships of physical, mechanical and electrical properties have not reliably predicted integration success. Therefore a steep learning (reinventing) curve is in progress throughout the industry. Fortunately, no new electrical or electromigration failure modes have been identified and attributed directly to any low- $\kappa$  dielectric material. The technical community still maintains a healthy debate about microstructure requirements for porous dielectric materials with respect to pore size, pore shape, aspect ratio and degree of interconnectivity (open *versus* closed).

#### HARDMASK

This is a generic term used to describe the dielectric film deposited on top of the trench level intra-metal dielectric. It has two main functions—1) to assist in patterning of the dual-Damascene structure for subsequent metal fill and 2) as a highly selective CMP stop layer. In addition, this layer is called upon to prevent fast diffusion of acid or base moieties that could interact detrimentally with the traditional acid catalyzed photoresist systems employed at 248 nm and 193 nm. Depending on the efficiency of CMP and acid/base moiety inhibition, this layer could be inconsequential to the over all  $\kappa_{eff}$  or a significant contributor. For most integration schemes, the composition of this layer can be chosen independently of most other dielectric layer choices. However, in the case of the hybrid integration scheme it is best to have the hardmask dielectric material and the via layer dielectric material similar to simplify the etch sequence. There are currently both spin-on and CVD deposited solutions available with dielectric constant values down to at least 3.0. Some spin-on offerings are available down to a dielectric constant value of 2.2.

#### ETCH STOP-VIA

The via etch stop layer also has two main functions. It must have significant enough etch selectivity with respect to the via dielectric layer so that etching of the underlying IMD adjacent to non-landed vias is avoided. This via etch stop also serves as the capping layer for the underlying Cu wiring layer. It must be a Cu diffusion barrier and have acceptable adhesion and interface properties so that Cu electromigration requirements are met. The via etch stop layer can also be a significant contributor to overall  $\kappa_{eff}$  so its thickness and  $\kappa$  value should both be minimized.

#### ETCH STOP—TRENCH

The primary function of this dielectric layer is to provide enough etch selectivity, as compared to the trench level dielectric, to form a smooth, well-defined trench bottom. Significant trench bottom roughness can be a reliability issue if it affects metal barrier coverage. Variability in trench depth can be a significant contributor to variation in metal line resistance. Alternate integration schemes, like a hybrid ILD structure, have eliminated the need for a discrete trench etch stop layer by incorporating these requirements in the via level dielectric.

#### DRAM

DRAM technology has just begun the arduous process of implementing the assortment of medium dielectric constant materials ( $5 < \kappa < 40$ ) in stacked capacitor structures. The trench defined DRAM technology could possibly delay the implementation of these medium dielectric materials for an additional technology node because of the enhanced active area available. Both DRAM technologies will develop an understanding of these medium dielectric constant materials as a stepping-stone to the higher  $\kappa$  (> 40) alternatives. These high dielectric constant materials, again, are most likely to be implemented in stacked capacitor structures (DRAM) initially, followed by trench capacitor structures, before they are considered as replacements for silicon dioxide gates.

HDP—high density plasma SA-CVD—sub atmospheric CVD PSG—phospho-silicate glass MSQ—methyl silsesquioxane HSQ—hydrogen silsesquioxane FSG—fluorinated silicate glass OSG—organosilicate glass

Figure 57 Dielectric Potential Solutions

Figure 57 Dielectric Potential Solutions (continued)

### **CONDUCTOR POTENTIAL SOLUTIONS**

Local wiring, which is sometimes called M0, is limited to very short lengths for contacts and adjacent transistors. Tungsten will continue to be used for local wiring and for the contact level to the devices in microprocessors, ASICs and DRAMs. ALD, in conjunction with CVD techniques, is being utilized first in the W deposition area to accomplish a seamless W fill. The absence of seams at the local wiring or contact level is especially important when the subsequent wiring level is ECD copper in order to avoid defect issues associated with retained plating solution.

Continued development of ALD tungsten deposition will be needed to accomplish W fill of high aspect ratio (17:1 in 2009) contacts for stacked capacitor DRAM designs. Alternate materials and techniques may ultimately be needed to address the long-term requirements of DRAM stacked capacitor contacts, which are projected to have aspect ratios greater than 20:1 by 2012. Aluminum may continue to be used for local wiring and enhanced CVD/PVD flow techniques will continue to be improved for Damascene architectures.

Cu will be the preferred solution for the Metal 1 and intermediate wiring levels in microprocessors and ASICs and electrochemical deposition will continue to dominate the market in the near term. There will be continuous improvement in the plating chemistry and ECD tool design to allow seamless fill of smaller geometry higher aspect ratio structures. Development is also underway to accomplish both deposition and planarization in a single tool by combining ECD with CMP or CEP.

CVD Cu fill may become competitive as a fill technology if the same "superfilling" behavior and microstructure characteristic of ECD can be achieved. Alternatively combinations of CVD and PVD Cu may be employed to accomplish seamless fill at smaller geometries. Deposition of Cu and other conductors from supercritical CO<sub>2</sub> solutions is still in the research phase but is also a promising technology.

Metal 1 Cu wiring will be the first to be impacted by the size effects that will increase Cu resistivity toward the end of this decade. Soon thereafter, size effects will also increase Cu resistivity for the intermediate wiring levels. This is much more problematic since intermediate wiring traverses longer lengths and is more likely to impact performance than Metal 1 wiring. Cu interfaces, microstructure and impurity levels will need to be engineered to alleviate the impact of this resistivity rise for a few additional technology generations.

Global wiring levels, with their much larger linewidths, will be the last to be impacted by size effects in Cu. However, scaling at each technology generation has the largest impact on global wiring levels that nominally traverse lengths on the order of the die size. This problem is currently being addressed by the intelligent use of repeaters, or by oversized drivers, but they impact both chip size and power. The most likely near term solutions are appropriate use of design and signaling options, packaging or 3D interconnects to minimize the effect of these resistive global wires. A great deal of research is also underway on the use of either RF or optical techniques to resolve this issue. More radical solutions include cooled conductors, superconductors, nanotubes etc. All of the above global wiring alternatives are discussed in greater detail in the new concepts section of the Interconnect roadmap.

The increasing market for wireless devices and telecom applications will spur a focus on processes and materials for passive devices within the interconnect structure. In particular, there will be a focus on new processes and materials for forming the electrodes of metal-insulator-metal (MIM) capacitors to improve yield and reliability. Both Al and Cu are currently in use for standard spiral inductors, but in the future various magnetic materials may emerge with different inductor designs to reduce the area of these devices.

*ALD—atomic layer deposition ECD—electrochemical deposition CMP—chemical mechanical planarization CEP—chemically enhanced planarization*

\*Cu process with optimized interfaces, microstructures, and impurities to alleviate resistivity rise at small critical dimensions

Figure 58 Conductor Potential Solutions

#### **BARRIER POTENTIAL SOLUTIONS**

Barriers for tungsten local wiring and contact fill will continue to utilize Ti/TiN films. There will be continuous improvement on established deposition techniques such as long throw and ionized PVD and CVD to improve compatibility with the new seamless W technology. CVD Ti/TiN barriers will continue to be improved for high aspect ratio contacts (e.g., DRAM stacked capacitors) filled with W conductor. Development of ALD Ti/TiN along with ALD W is underway and is likely to improve the overall seamless W fill process by eliminating the "pinch off" of the contact hole characteristic of other deposition techniques.

Conventional PVD and CVD barrier technologies will be continuously improved to allow Al fill to be extended to higher aspect ratio structures, however it is likely that ALD barriers will also replace these techniques in the future. Research is also underway to explore alternate materials and fill techniques for high aspect ratio contact structures that would allow simplification of the current contact/barrier/conductor film stack.

Barrier materials used for Cu wiring must prevent Cu diffusion into the adjacent dielectric and must form a suitable, high quality interface with Cu to limit vacancy diffusion and achieve acceptable electromigration lifetimes. TaN/Ta has become the predominant industry solution but other nitrides and silicon nitrides of Ta, Ti, and W have also shown promise.

Long throw, ionized PVD, and CVD depositions will continue to be improved to meet the very challenging sidewall coverage requirements of future dual-Damascene structures. However, even the most advanced of these deposition techniques tend to narrow the upper part of the dual-Damascene trench and limit the fill capability of the ECD Cu process. A great deal of effort is underway to develop ALD barriers that are expected to become the predominant future solution for copper.

One major obstacle to the adoption of ALD for barriers is penetration of the precursor materials into the porous low- $\kappa$  dielectrics targeted for future technology nodes. *In situ* modification of the etched low- $\kappa$  sidewalls may be used either with ALD or as a standalone barrier solution to resolve this issue. Development is also underway to explore deposition of barriers by electroless techniques and from supercritical CO<sub>2</sub>.

Another focus area for metal barriers is the top surface of the Cu dual-Damascene structure. Dielectric Cu barriers such as Si<sub>3</sub>N<sub>4</sub>, SiCN and SiC currently predominate for this application, however they are not the preferred solution because their higher  $\kappa$  values increase the overall  $\kappa_{eff}$  of the structure. Selective metal capping barriers such as W or CoWP are being explored for this application.

Finally, a great deal of research and development in the area of advanced barrier materials and deposition techniques will be needed. Engineering the smoothness and other properties of the Cu barrier interface will be key to ameliorating the expected Cu resistivity increase due to electron scattering effects.

|                                                                                                                         | <b>20</b><br>2003 | <b>04</b><br>20 | 05 200 | <b>20</b><br>96 | -  | 08 200 | <b>20</b><br>09 |    | 11 20 | <b>20</b><br>12 |    | 14 20 | -  | 1 <b>6</b><br>20 | 17 20 | <b>20</b><br>18 | )19<br> |

|-------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|--------|-----------------|----|--------|-----------------|----|-------|-----------------|----|-------|----|------------------|-------|-----------------|---------|

| Technology Node                                                                                                         | hp                | 90              |        | hp              | 65 |        | hp              | 45 |       | hp              | 32 |       | hp | 22               |       | hp              | 1<br>16 |

| LOCAL WIRING<br>Barriers for seamless fill W<br>conductor (PVD, long throw PVD,<br>CVD)<br>Barriers for complete fill W |                   |                 |        |                 |    |        |                 |    |       |                 |    |       |    |                  |       |                 |         |

| Barriers for seamless fill W<br>conductor (ALD)                                                                         |                   |                 |        |                 |    |        |                 |    |       |                 |    |       |    |                  |       |                 |         |

| Barriers for high A/R CVD W<br>contact for DRAM (CVD)                                                                   |                   |                 |        |                 |    |        |                 |    |       |                 |    |       |    |                  |       |                 |         |

| Barriers for high A/R CVD W<br>contact for DRAM (ALD)                                                                   |                   |                 |        |                 |    |        |                 |    |       |                 |    |       |    |                  |       |                 |         |

| Barriers for enhanced PVD/CVD AI<br>fill (PVD, ionized PVD, long throw<br>PVD, CVD)                                     |                   |                 |        |                 |    |        |                 |    |       |                 |    |       |    |                  |       |                 |         |

| Barriers for enhanced PVD/CVD AI<br>fill (ALD)                                                                          |                   |                 |        |                 |    |        |                 |    |       |                 |    |       |    |                  |       |                 |         |

| Barriers for high A/R alternative<br>contact fill for DRAM (ALD)                                                        |                   |                 |        |                 |    |        |                 |    |       |                 |    |       |    |                  |       |                 |         |

| METAL 1 AND INTERMEDIATE<br>WIRING (FOR Cu)                                                                             |                   |                 |        |                 |    |        |                 |    |       |                 |    |       |    |                  |       |                 |         |

| Long throw PVD, ionized PVD, CVD<br>of nitrides and Si nitrides of Ta, Ti,<br>and W                                     |                   |                 |        |                 |    |        |                 |    |       |                 |    |       |    |                  |       |                 |         |

| ALD of nitrides and Si nitrides of Ta,<br>Ti, and W                                                                     |                   |                 |        |                 |    |        |                 |    |       |                 |    |       |    |                  |       |                 |         |

| In situ dielectric formation modification                                                                               |                   |                 |        |                 |    |        |                 |    |       |                 |    |       |    |                  |       |                 |         |

| Electroless deposited barriers                                                                                          |                   | -               |        |                 |    |        |                 |    |       |                 |    |       |    |                  |       |                 |         |

| Barriers deposited from supercritical CO <sub>2</sub>                                                                   |                   |                 |        |                 |    |        |                 |    |       |                 |    |       |    |                  |       |                 |         |

| Capping barriers (CoWP, selective W, and others)                                                                        |                   |                 |        |                 |    |        |                 |    |       |                 |    |       |    |                  |       |                 |         |

| Engineered barriers for low<br>resistance Cu process                                                                    |                   |                 |        |                 |    |        |                 |    |       |                 |    |       |    |                  |       |                 |         |

| GLOBAL WIRING                                                                                                           |                   |                 |        |                 |    |        |                 |    |       |                 |    |       |    |                  |       |                 |         |

| 3D interconnects                                                                                                        |                   |                 |        |                 |    |        |                 |    |       |                 |    |       |    |                  |       |                 |         |

| Barriers for RF/Microwave<br>interconnects                                                                              |                   |                 |        |                 |    |        |                 |    |       |                 |    |       |    |                  |       |                 |         |

| Barriers for optical interconnects                                                                                      |                   |                 |        |                 |    |        |                 |    |       |                 |    |       |    |                  |       |                 |         |

| Barriers compatible with cooled<br>conductors                                                                           |                   |                 |        |                 |    |        |                 |    |       |                 |    |       |    |                  |       |                 |         |

| Barriers compatible with cooled<br>superconductors                                                                      |                   |                 |        |                 |    |        |                 |    |       |                 |    |       |    |                  |       |                 |         |

| ALTERNATIVE MEMORY                                                                                                      |                   |                 |        |                 |    |        |                 |    |       |                 |    |       |    |                  |       |                 |         |

| Barriers for alternative memory<br>materials (SBT, PZT)                                                                 |                   |                 |        |                 |    |        |                 |    |       |                 |    |       |    |                  |       |                 |         |

SBT—strontium barium titanate

Figure 59 Barrier Potential Solutions

#### **NUCLEATION POTENTIAL SOLUTIONS**

The conformality and coverage of the nucleation layer is often the critical factor in determining whether the subsequent conductor deposition will be seamless or free of voids. For local wiring and contact fill, there will be continued improvement in ALD W nucleation layers that have been used to enable seamless or high aspect ratio W fill. In the area of Al fill, the CVD Al nucleation layer may be extended to ALD to allow continuous improvement in the fill characteristics of this technology.

Development is still underway for alternative materials and processes for high aspect ratio DRAM contacts but ALD nucleation layers will likely be needed for this technology.

For Metal 1, Intermediate and Global wiring, enhanced PVD Cu, deposited through either long throw or various ionized techniques, continues to be the dominant nucleation layer for ECD Cu. There will be improvement of these enhanced PVD techniques and they will continue to be used, especially on the global wiring levels with larger critical dimensions. However, these enhanced PVD techniques have marginal extendibility to next generation dual Damascene structures and various Cu nucleation layer alternatives are being explored.

There continues to be research for both electroless and CVD Cu nucleation layers and development is already well underway on deposition of Cu nucleation layers using either ALD or supercritical CO<sub>2</sub>. Another potential solution to the problem of marginal PVD Cu sidewall coverage is repair of the nucleation layer through ECD techniques. A more elegant solution to the problem involves modification of the ECD process and/or barrier to be self-nucleating thereby eliminating the need for a Cu nucleation layer.

Figure 60 Nucleation Potential Solutions

#### **PLANARIZATION POTENTIAL SOLUTIONS**

Increasingly, planarization has become an enabling step for interconnect technology. As materials and structures become less conventional and demands on planarization tolerances become more exacting, planarization processes themselves become more closely coupled to the choice of integration scheme. Chemical-mechanical polishing (CMP) and near alternatives remain the leading planarization technologies for current and future manufacturing. The combinations of materials and structures that define a CMP application continue to grow. Each application has unique needs and may dictate unique solutions.

The CMP of doped silicon dioxide for pre-metal dielectrics (PMD) and CMP of tungsten for local interconnect and contacts will remain a requirement for the foreseeable future. PMD is an example of where multiple applications can exist with similar materials. Target PMD CMP stops at a target thickness within a film, similar to interlevel dielectric (ILD) CMP. Selective PMD stops on or in an underlying film with selectivity to optimize topography. Polysilicon CMP is utilized today in making memory devices.

ILD CMP and tungsten via CMP are slowly being reduced. They are being replaced with Cu dual-Damascene CMP with the adoption of copper damascene processes.

Copper and barrier CMP are standard processes for leading edge logic devices and adoption for memory devices and other logic devices will follow. The dielectric materials into which copper damascene features are built are on a path of decreasing  $\kappa$  values over time. Each change in dielectric materials brings new metal planarization challenges. Among these is the need to reduce the mechanical forces applied to the wafer during CMP, in order to prevent adhesive/cohesive failures in the dielectric, due to the reduced mechanical strength of ULK dielectrics. Although this problem can be alleviated through integration choices, including the use of capping layers, an effective dielectric constant performance penalty is likely. Integration can also include hardmask films that need to be removed to avoid the penalty.

As minimum wire dimensions scale with each new technology node, the primary influence that planarization has on control of wire thickness becomes increasingly important. Thickness variation of Metal 1 and intermediate Cu wiring at minimum pitch is a result of pattern erosion during CMP. Thickness variation of the global wiring results from both pattern erosion and dishing of the individual wires. With the projected scaling of wire thickness, it is likely that Cu variation due to CMP must be limited to less than 10% of the nominal thickness for any interconnect level.