# INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS

2003 EDITION

# **METROLOGY**

THE ITRS IS DEVISED AND INTENDED FOR TECHNOLOGY ASSESSMENT ONLY AND IS WITHOUT REGARD TO ANY COMMERCIAL CONSIDERATIONS PERTAINING TO INDIVIDUAL PRODUCTS OR EQUIPMENT.

# **TABLE OF CONTENTS**

| Scope                   |                                                                      | 2        |

|-------------------------|----------------------------------------------------------------------|----------|

| Infrastructu            | re Needs                                                             | 2        |

| Difficult Cha           | llenges                                                              | 3        |

| Metrology To            | echnology Requirements and Potential Solutions                       | 4        |

| Measureme<br>Reaching A | ents for Processes Facing Statistical Limits and Physical Structures | <i>F</i> |

|                         | /                                                                    |          |

|                         | / Metrology                                                          |          |

|                         | Processes Metrology                                                  |          |

|                         | ct Metrology                                                         |          |

|                         | nd Contamination Characterization                                    |          |

| Integrated I            | Metrology and Advanced Process Control                               | 32       |

|                         | ation and Metrology for Emerging Device Technologies                 |          |

| Molecular E             | Electronics                                                          | 34       |

| Nanowires               |                                                                      | 35       |

| Spintronics             |                                                                      | 35       |

| Reference M             | Neasurement System                                                   | 35       |

| Reference               | Materials                                                            | 36       |

| _                       |                                                                      |          |

| List of Fig             | GURES                                                                |          |

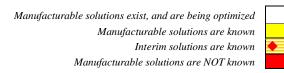

| Figure 81               | Lithography Metrology—CD Measurement Potential Solutions             | 17       |

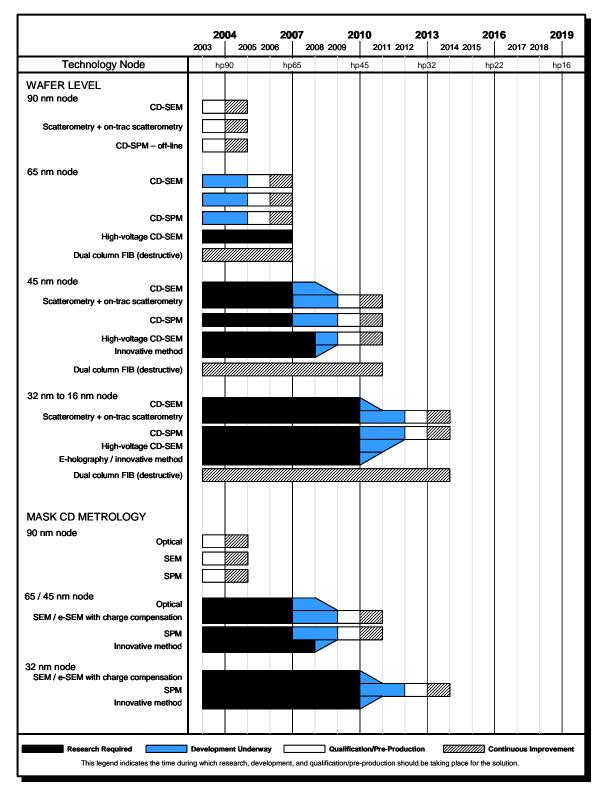

| Figure 82               | Lithography Metrology—Overlay Potential Solutions                    |          |

| Figure 83               | Front End Processes Metrology Potential Solution                     |          |

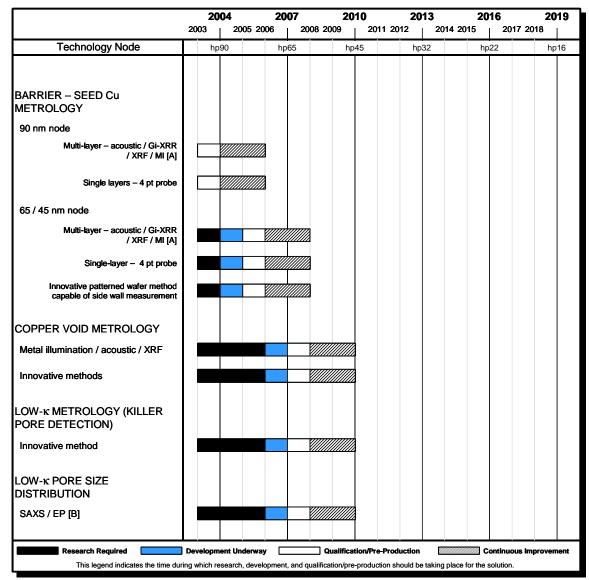

| Figure 84               | Interconnect Metrology Potential Solutions                           |          |

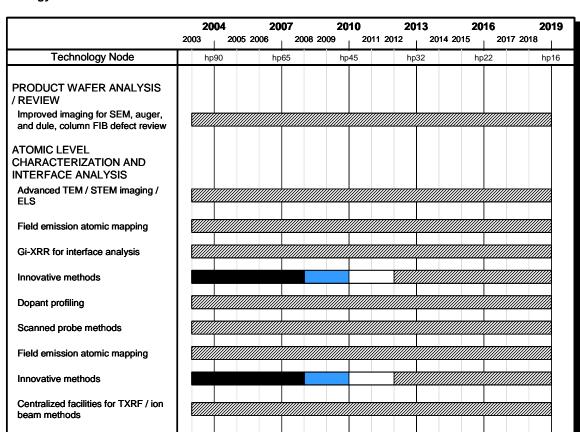

| Figure 85               | Materials and Contamination Potential Solutions                      |          |

# **LIST OF TABLES**

| Table 115  | Metrology Difficult Challenges                                               | 3  |

|------------|------------------------------------------------------------------------------|----|

| Table 116a | Metrology Technology Requirements—Near-term                                  |    |

| Table 116b | Metrology Technology Requirements—Long-term                                  | 5  |

| Table 117a | Lithography Wafer Metrology Technology Requirements—Near-term                | 10 |

| Table 117b | Lithography Metrology Technology Requirements—Long-term                      | 11 |

| Table 118a | Lithography Metrology (Mask) Technology Requirements: Optical—Near-term      | 12 |

| Table 118b | Lithography Metrology (Mask) Technology Requirements: EUV—Near and Long-term | 13 |

| Table 118c | Lithography Metrology (Mask) Technology Requirements: EPL—Near and long-term | 15 |

| Table 119a | Front End Processes Metrology Technology Requirements—Near-term              | 19 |

| Table 119b | Front End Processes Metrology Technology Requirements—Long-term              | 21 |

| Table 120a | Interconnect Metrology Technology Requirements—Near Term                     | 26 |

| Table 120b | Interconnect Metrology Technology Requirements—Long-term                     | 27 |

# **METROLOGY**

Metrology, including materials characterization, continues to enable the introduction and manufacture of new materials, processes, and structures. The pace of feature size reduction challenges traditional measurement technology, and the uncertain nature of device design adds to the challenge. Long-term research into nano-devices may provide both new measurement methods and potential test vehicles for metrology. Although most metrology done inside new manufacturing facilities uses in-line equipment, the evolution to in situ continues. All metrology is connected to factorywide automation that include database and intelligent information from data capability. Off-line materials characterization is also evolving toward compatibility with factory-wide automation. Although thorough materials characterization is a critical part of materials and process development, predicting the necessary metrology for manufacturing remains an elusive goal. Issues resolved by process improvements leave open the question of what to measure during manufacturing to ensure reliability.

The relationship between metrology and process technology development needs fundamental restructuring. In the past the challenge has been to develop metrology ahead of target process technology. Today we face major uncertainty from unresolved choices of fundamentally new materials and radically different device designs. Understanding the interaction between metrology data and information and optimum feed forward and real-time process control are key to restructuring the relationship between metrology and process technology. A new section has been added to the Metrology Roadmap that covers metrology needs for emerging technology paradigms such as spintronics and molecular electronics.

Research and development of new as well as evolutionary metrology technology must keep pace with the three-year schedule for introduction of new technology generations. The roadmap for feature size reduction drives the timeline for metrology solutions for new materials, process, and structures. New substrate materials such as silicon on insulator and strained silicon channels add to the complexity of measurements. Metrology development must be done in the context of these issues. Metrology enables tool improvement, ramping in pilot lines and factory start-ups, and improvement of yield in mature factories. Metrology can reduce the cost of manufacturing and the time-to-market for new products through better characterization of process tools and processes. The increasing diversity of chip types will spread already limited metrology resources over a wider range of challenges. The metrology community including suppliers, chip manufacturers, consortia, and research institutions must provide cooperative research, development, and prototyping in order to meet the ITRS timeline. The forefront developments in measurement technology must be commercialized in a timely manner. The feature sizes and materials a decade away in the 2003 Roadmap already greatly challenge the measurements used in process and materials development.

The near term challenges for metrology revolve around the need for controlling scaling as well as new materials and processes used for gate stack, ultra-shallow junctions, and copper/low-κ interconnect. The large number of candidate materials being considered for each node require characterization in evaluation and control in development and process. Moreover, it is entirely possible that different materials will be used by different manufacturers at a given node, potentially requiring different metrologies. Advances in electrical and physical metrology for high- and low-κ dielectric films must continue, and new metrology for pore size distribution and voids in copper lines are being evaluated. The increasing emphasis on active area measurements instead of test structures in scribe (kerf) lines places new demands on metrology. Long-term needs are difficult to address due to the lack of clarity of device design and interconnect technology. The selection of a replacement for copper interconnect remains a research challenge. Although materials characterization and some existing in-line metrology apply to new device and interconnect structures, development of manufacturing capable metrology requires a more certain knowledge of materials, devices, and interconnect structures.

All areas of measurement technology (especially those covered in the Yield Enhancement chapter) are being combined with computer integrated manufacturing (CIM) and data management systems for information-based process control. Although Integrated Metrology still needs a universal definition, it has become the term associated with the slow migration from offline to inline and in situ measurements. The proper combination of offline, inline, and in situ measurements will enable advanced process control and rapid yield learning.

Metrology tool development requires access to new materials and structures if it is to be successful. It requires the availability of state-of-the-art capabilities to be made available for fabrication of necessary standards and development of metrology methodologies in advance of production. This requires a greater attention to expanding close ties between metrology development and process development. When the metrology is well matched to the process tools and

processes, ramping times for pilot lines and factories are reduced. An appropriate combination of well-engineered tools and appropriate metrology is necessary to maximize productivity while maintaining acceptable cost of ownership.

# SCOPE

The metrology topics covered in the 2003 Metrology roadmap are microscopy; critical dimension (CD) and overlay; film thickness and profile; materials and contamination analysis; dopant profile; in situ sensors and cluster stations for process control; reference materials; correlation of physical and electrical measurements; and packaging. These topics are reported in the following sections: Measurements for Processes Facing Statistical Limits and Physical Structures Reaching Atomic Dimensions; Microscopy; Lithography Metrology; Front End Processes Metrology; Interconnect Metrology; Materials and Contamination Characterization; Integrated Metrology; Reference Measurement Systems, Reference Materials; and Characterization and Metrology for Emerging Devices.

International cooperation in the development of new metrology technology and standards will be required. Both metrology and process research and development organizations must work together with the industry including both the supplier and IC manufacturer. Earlier cooperation between IC manufacturers and metrology suppliers will provide technology roadmaps that maximize the effectiveness of measurement equipment. Metrology, process, and standards research institutes, standards organizations, metrology tool suppliers, and the university community should continue to cooperate on standardization and improvement of methods and on production of reference materials. Despite the existence of standardized definitions and procedures for metrics, individualized implementation of metrics such as measurement precision to tolerance (P/T) ratio is typical. The P/T ratio for evaluation of automated measurement capability for use in statistical process control relates the measurement variation (precision) of the metrology tool to the product specification limits. Determination of measurement tool variations is sometimes carried out using reference materials that are not representative of the product or process of interest. Thus, the measurement tool precision information may not reflect measurement-tool induced variations on product wafers. It is also possible that the sensitivity of the instrument could be insufficient to detect small but unacceptable process variations. There is a need for metrics that accurately describe the resolution capability of metrology tools for use in statistical process control. The inverse of the measurement precision-to-process variability is sometimes called the signal-to-noise ratio or the discrimination ratio. However, because the type of resolution depends on the process (e.g., thickness and width require spatial resolution while levels of metallics on the surface require resolution of atomic percent differences), topic-specific metrics may be required. A new need is for standardized approach to determination of precision when the metrology tool provides discrete instead of continuous data. This situation occurs, for example, when significant differences are smaller than the instrument resolution.

The principles of Integrated Metrology can be applied to stand-alone and sensor based metrology itself. Factors that impact tool calibration and measurement precision such as small changes in ambient temperature and humidity could be monitored and used to improve metrology tool performance and thus improve statistical process control.

Wafer manufacturers, process tool suppliers, pilot lines, and factory start-ups all have different timing and measurement requirements. The need for a shorter ramp-up time for pilot lines means that characterization of tools and processes prior to pilot line startup must improve. However, as the process matures, the need for metrology should decrease. As device dimensions shrink, the challenge for physical metrology will be to keep pace with inline electrical testing that provides critical electrical performance data.

# INFRASTRUCTURE NEEDS

A healthy industry infrastructure is required if suppliers are to provide cost-effective metrology tools, sensors, controllers, and reference materials. New research and development will be required if opportunities such as MEMS based metrology and nano-technology are to make the transition from R&D to commercialized products. Many metrology suppliers are small companies that find the cost of providing new tools for leading-edge activities prohibitive. Initial sales of metrology tools are to tool and process developers. Sustained, high-volume sales of the same metrology equipment to chip manufacturers does not occur until several years later. The present infrastructure cannot support this delayed return on investment. Funding that meets the investment requirements of the supplier community is needed to take new technology from proof of concept to prototype systems and finally to volume sales.

<sup>&</sup>lt;sup>1</sup> For example, refer to SEMI E89-0999 "Guide For Measurement System Capability Analysis."

# **DIFFICULT CHALLENGES**

Many short-term metrology challenges listed below will continue beyond the 45 nm node. Metrology needs after 2009 will be affected by unknown new materials and processes. Thus, it is difficult to identify all future metrology needs. Shrinking feature sizes, tighter control of device electrical parameters, such as threshold voltage and leakage current, and new interconnect materials will provide the main challenges for physical metrology methods. To achieve desired device scaling, metrology tools must be capable of measurement of properties on atomic distances. Table 115 presents the ten major challenges for metrology.

Table 115 Metrology Difficult Challenges

| Five Difficult Challenges ≥ 45 nm/Through 2009                                                                                                                                                                                                                                                                                                                                               | Summary of Issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Factory level and company wide metrology integration for real-time <i>in situ</i> , integrated, and inline metrology tools; continued development of robust sensors and process controllers; and data management that allows integration of add-on sensors.                                                                                                                                  | Standards for process controllers and data management must be agreed upon. Conversion of massive quantities of raw data to information useful for enhancing the yield of a semiconductor manufacturing process. Better sensors must be developed for trench etch end point, ion species /energy /dosage (current), and wafer temperature during RTA.                                                                                                                                                                                                                                                                                                                   |

| Starting materials metrology and manufacturing metrology are impacted by the introduction of new substrates such as SOI. Impurity detection (especially particles) at levels of interest for starting materials and reduced edge exclusion for metrology tools. CD, film thickness, and defect detection are impacted by thin SOI optical properties and charging by electron and ion beams. | Existing capabilities will not meet Roadmap specifications. Very small particles must be detected and properly sized. Capability for SOI wafers needs enhancement. Challenges come from the extra optical reflection in SOI and the surface quality.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Control of high-aspect ratio technologies such as Damascene challenges all metrology methods. Key requirements are dimensional control, void detection in copper lines, and pore size distribution and detection of killer pores in patterned low- $\kappa$ dielectrics.                                                                                                                     | New process control needs are not yet established. For example, 3D (CD and depth) measurements will be required for trench structures in new, low- $\kappa$ dielectrics. Sidewall roughness impacts barrier integrity and the electrical properties of lines and vias.                                                                                                                                                                                                                                                                                                                                                                                                 |

| Measurement of complex material stacks and interfacial properties including physical and electrical properties.                                                                                                                                                                                                                                                                              | Reference materials and standard measurement methodology for new, high-κ gate and capacitor dielectrics with engineered thin films and interface layers as well as interconnect barrier and low-κ dielectric layers, and other process needs. Optical measurement of gate and capacitor dielectric averages over too large an area and needs to characterize interfacial layers. Carrier mobility characterization will be needed for stacks with strained silicon and SOI substrates. The same is true for measurement of barrier layers. High frequency dielectric constant measurements have shown a constant frequency response and are no longer a pressing need. |

| Measurement test structures and reference materials.                                                                                                                                                                                                                                                                                                                                         | The area available for test structures is being reduced especially in the scribe lines. There is a concern that measurements on test structures located in scribe lines do not correlate with in die performance.  Overlay and other test structures are sensitive to process variation, and test structure design must be improved to ensure correlation between measurements in the scribe line and on chip properties.  Standards institutions need rapid access to state of the art development and manufacturing capability to fabricate relevant reference materials.                                                                                            |

| Five Difficult Challenges < 45 nm/Beyond 2009                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Nondestructive, production worthy wafer and mask level microscopy for critical dimension measurement for 3D structures, overlay, defect detection, and analysis                                                                                                                                                                                                                              | Surface charging and contamination interfere with electron beam imaging. CD measurements must account for sidewall shape. CD for Damascene process may require measurement of trench structures. Process control such as focus exposure and etch bias will require greater precision and 3D capability.                                                                                                                                                                                                                                                                                                                                                                |

| New strategy for in-die metrology must reflect across chip and across wafer variation.                                                                                                                                                                                                                                                                                                       | Correlation of test structure variations with in die properties is becoming more difficult as device shrinks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Statistical limits of sub-45 nm process control                                                                                                                                                                                                                                                                                                                                              | Controlling processes where the natural stochastic variation limits metrology will be difficult. Examples are low-dose implant, thin gate dielectrics, and edge roughness of very small structures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Structural and elemental analysis at device dimensions.                                                                                                                                                                                                                                                                                                                                      | Materials characterization and metrology methods are needed for control of interfacial layers, dopant positions, and atomic concentrations relative to device dimensions. One example is 3D dopant profiling.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Determination of manufacturing metrology when device and interconnect technology remain undefined.                                                                                                                                                                                                                                                                                           | The replacement devices for the transistor and structure and materials replacement for copper interconnect are being researched.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

<sup>\*</sup> SPC—statistical process control parameters are needed to replace inspection, reduce process variation, control defects, and reduce waste.

# METROLOGY TECHNOLOGY REQUIREMENTS AND POTENTIAL SOLUTIONS

Selected measurement requirements for metrology tools are listed in Tables 116–120. The microscopy resolution refers to the ability of a CD measurement tool to distinguish between lines that differ in width. The spatial resolution requirements for 2- and 3-dimensional (2D and 3D) dopant profiling are based on the requirements of Modeling & Simulation. Meeting 2D dopant profiling requirements will be difficult, and methods with slightly less spatial resolution may provide useful information. Measurement accuracy for all metrology requires appropriate reference materials.

Table 116a Metrology Technology Requirements—Near-term

| Year of Production                                                                                                                                     | 2003     | 2004     | 2005     | 2006     | 2007     | 2008     | 2009     | Driver   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|

| Technology Node                                                                                                                                        |          | hp90     |          |          | hp65     |          |          |          |

| DRAM ½ Pitch (nm)                                                                                                                                      | 100      | 90       | 80       | 70       | 65       | 57       | 50       |          |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                                                                                                     | 120      | 107      | 95       | 85       | 76       | 67       | 60       | MPU/ASIC |

| MPU/ASIC Un-contacted Poly ½ Pitch (nm)                                                                                                                | 107      | 90       | 80       | 70       | 65       | 57       | 50       |          |

| MPU Printed Gate Length (nm)                                                                                                                           | 65       | 53       | 45       | 40       | 35       | 32       | 28       |          |

| MPU Physical Gate Length (nm)                                                                                                                          | 45       | 37       | 32       | 28       | 25       | 22       | 20       |          |

| Microscopy                                                                                                                                             |          | •        | •        |          |          |          | •        | •        |

| Inline, nondestructive microscopy process resolution (nm) for P/T=0.1                                                                                  | 0.40     | 0.33     | 0.29     | 0.25     | 0.22     | 0.20     | 0.18     | MPU Gate |

| Microscopy capable of measurement of                                                                                                                   | 13       | 15       | 15       | 16       | 16       | 17       | 17       |          |

| patterned wafers having maximum aspect ratio / diameter (nm) (DRAM contacts) [A]                                                                       | 120      | 107!     | 95       | 85       | 76       | 67       | 60       | D1/2     |

| Materials and Contamination Characterization                                                                                                           | n        |          |          |          |          |          |          |          |

| Real particle detection limit (nm) [B]                                                                                                                 | 45       | 37       | 32       | 28       | 25       | 22       | 20       | MPU      |

| Minimum particle size for compositional<br>analysis (dense lines on patterned wafers)<br>(nm)                                                          | 33       | 30       | 27       | 23       | 22       | 19       | 17       | D1/2     |

| Specification limit of total surface contamination for critical GOI surface materials (atoms/cm <sup>2</sup> ) [C]                                     | 5.00E+09 | MPU Gate |

| Surface detection limits for individual elements for critical GOI elements (atoms/cm <sup>2</sup> ) with signal-to-noise ratio of 3:1 for each element | 5.00E+08 | MPU Gate |

Notes for Tables 116a and 116b:

<sup>[</sup>A] Metal and via aspect ratios are additive for dual-Damascene process flow.

<sup>[</sup>B] This value depends on surface microroughness and layer composition.

<sup>[</sup>C] The requirements for metal contamination have been changed based on less stringent requirements found in Front End Processes chapter Surface Preparation Technology Requirements table, Note F.

2010 2012 2013 2016 Year of Production 2015 2018 Driver Technology Node hp45 hp32 hp22DRAM 1/2 Pitch (nm) 45 32 18 35 25 22 MPU/ASIC Metal 1 (M1) ½ Pitch (nm) 54 42 38 30 27 21 MPU/ASIC Un-contacted Poly 1/2 Pitch (nm) 45 35 32 25 22 18 25 14 13 10 MPU Printed Gate Length (nm) 20 18 MPU Physical Gate Length (nm) 18 14 13 10 9 7 Microscopy Inline, nondestructive microscopy process resolution 0.08 0.16 0.13 0.12 0.09 0.06 (nm) for P/T=0.1>20 Microscopy capable of measurement of patterned >20 >20 >20 >20 >20 wafers having maximum aspect ratio / diameter (nm) 50 35 30 25 21 18 (DRAM contacts) [A] Materials and Contamination Characterization Real particle detection limit (nm) [B] 18 14 13 10 9 7 Minimum particle size for compositional analysis 15 7 12 11 8 6 (dense lines on patterned wafers) (nm) Specification limit of total surface contamination for 5.00E+09 5.00E+09 5.00E+09 5.00E+09 5.00E+09 5.00E+09 critical COI surface materials (atoms/cm<sup>2</sup>) [C] Surface detection limits for individual elements for critical GOI elements (atoms/cm<sup>2</sup>) with signal-to-noise 5.00E+08 5.00E+08 5.00E+08 5.00E+08 5.00E+08 5.00E+08 ratio of 3:1 for each element

Table 116b Metrology Technology Requirements—Long-term

Manufacturable solutions exist, and are being optimized

Manufacturable solutions are known

Interim solutions are known

Manufacturable solutions are NOT known

# MEASUREMENTS FOR PROCESSES FACING STATISTICAL LIMITS AND PHYSICAL STRUCTURES REACHING ATOMIC DIMENSIONS

As the dimensions of integrated circuit devices continue to shrink, the finite dimensions of the atoms within the structures will lead to statistical variations in critical dimensions and thus device properties. Furthermore, as dimensions of structures continue to shrink, the physical properties will deviate from the bulk properties because of quantum mechanical and mean free path effects. For instance, the lattice spacing of silicon atoms in a 35 nm gate represents about 1% of the gate length. The effects of statistical variations may be even more pronounced in gate dielectric structures composed of multi-layers of different components, each only several atoms thick. The engineering of such structures must take these statistical variations of dopant atoms and intrinsic defects and the quantum mechanical effects of confined structures into account to obtain sufficiently uniform device and circuit performance for large-scale integration.

Advances in interconnect technology are introducing conductor materials such as copper that must be excluded from the semiconductor itself and low- $\kappa$  interconnect structures. Process and process modeling advances are required to deposit barrier layers of the order of only a few atomic layers that are pin hole-free. Metrology must be developed to ensure the integrity of barrier layers. As the conductor cross-section shrinks to the order of the mean free path of electrons, the bulk conductivity model no longer applies.

Several issues challenge measurement of transistor structures. Metrology of gate dielectric structures requires a practical standardized model of the quantum mechanical effects at the silicon—dielectric interface and gate—dielectric interface. Stochastic modeling strategies will be required to supplement deterministic (continuum) modeling techniques that have been used thus far. Significant advances in two- and three-dimensional dopant profiling metrology will be required to validate modeling. Mechanical stress changes the transport properties of transistors, and this can be either advantageous or detrimental. Metrology and modeling needs to be developed to manage stress effects.

These and other statistical variations in real materials and structures are independent of measurement uncertainties, and will add quadratically to the total uncertainty to the total uncertainty of the values of measured quantities. In addition, they must be taken into account in circuit and process design in ways that are not yet envisioned. It appears that the measurement uncertainties of a number of parameters specified for future device generations elsewhere in the Roadmap cannot be met for fundamental physical reasons having little to do with metrology *per se*.

## **MICROSCOPY**

Microscopy is used in most of the core technology processes where two-dimensional distributions, i.e., digital images of the shape and appearance of integrated circuit (IC) features reveal important information. Usually, imaging is the first, but many times the only one step in the "being able to see it, measure it, and control it" chain. Microscopes typically employ light, electron beam, or scanned probe methods. Beyond imaging, online microscopy applications include critical dimension (CD) and overlay measurements along with detection, review and automatic classification of defects and particles. Because of the high value and quantity of wafers, the need for rapid, non-destructive, inline imaging and measurement is growing. Due to the changing aspect ratios of IC features, besides the traditional lateral feature size, e.g. linewidth measurement, full three-dimensional shape measurements are gaining importance and should be available inline. Development of new metrology methods that use and take the full advantage of advanced digital image processing and analysis techniques, telepresence, and networked measurement tools will be needed to meet the requirements of near future IC technologies. Microscopy techniques and measurements based on them must serve the technologists better giving fast, detailed, adequate information on the processes in ways that help to establish process control in a more automated manner. Refer to the *supplemental material for more details on Microscopy*.

*Electron Microscopy*—There are many different microscopy methods that use electron beams as sources of illumination. These include scanning electron microscopy, transmission electron microscopy, scanning transmission electron microscopy, electron holography, and low-energy electron microscopy. Scanning electron microscopy and electron holography are discussed below, and transmission electron microscopy, scanning transmission electron microscopy, and low-energy electron microscopy are discussed in the section on Materials and Contamination Characterization.

Scanning Electron Microscopy (SEM)—continues to provide at-line and inline imaging for characterization of crosssectional samples, particle and defect analysis, inline defect imaging (defect review), and CD measurements. Improvements are needed for effective CD and defect review (and SEM detection in pilot lines) at or beyond the 65 nm generation. New inline SEM technology, such as the use of ultra-low-energy electron beams (< 250 eV) and high energy SEM may be required for overcoming image degradation due to charging, contamination, and radiation damage of the sample surface, while maintaining adequate resolution. Improving the resolution of the SEM by the reduction of spherical aberration leads to an unacceptably small depth of field and SEM imaging with several focus steps and/or use of algorithms that take the beam shape into account might be needed. Aberration correction lens technology has migrated from transmission electron microscopy to SEM providing a significant increase in capability. Other non-traditional SEM imaging techniques such as the implementation of nano-tips, and electron holography need to be developed, if they can prove to be production-worthy methodologies. A new alternative path could be high-pressure or environmental microscopy, which opens the possibility for higher accelerating voltage high-resolution imaging and metrology. Binary and phase-shifting chromium-on-quartz optical photomasks have been successfully investigated with this mode of highresolution scanning electron microscopy. It has been found that the gaseous sample environment minimizes sample charging and contamination. This methodology also holds good potentials for the inspection, imaging and metrology of wafers.

To be able to make statistically sound SEM measurements it is essential to collect the right kind and right amount of information. The collection of more then needed information leads to loss of throughput, not enough or wrong type to loss of control. It is important to develop metrology methods that reveal and express the needed information with the indication of the validity of the measurements. Data analysis methods that adhere to the physics of the measurement and do use all information collected were demonstrated to be better than arbitrary methods. Measured and modeled image and fast and accurate comparative techniques are likely to gain importance in SEM dimensional metrology.

A better understanding of the relationship between the physical object and the waveform analyzed by the instrument is expected to improve CD measurement. Sample damage, which arises from direct ionization damage of the sample and the deposition of charge in gate structures, may set fundamental limits to the utility of all microscopies relying on charged particle beams.

Determination of the real 3D shape for sub-90 nm contacts/vias, transistor gates, interconnect lines or damascene trenches will require continuing advances in existing microscopy and sample preparation methods. Cross sectioning by FIB and lift-out for imaging in a TEM or a STEM has been successfully demonstrated.

Scanning probe microscopy (SPM)—may be used to calibrate CD-SEM measurements. Stylus microscopes offer 3D measurements that are insensitive to the material scanned. Flexing of the stylus degrades measurements, when the probe is too slender. The stylus shape and aspect ratio must, therefore, be appropriate for the probe material used and the forces encountered. High stiffness probe materials, such as short carbon nano-tubes, may alleviate this problem.

Far-field optical microscopy—is limited by the wavelength of light. Deep ultra-violet sources and near-field microscopy are being developed to overcome these limitations. Improved software allowing automatic classification of defects is needed. Optical microscopes will continue to have application in the inspection of large features, such as solder bump arrays for multi-chip modules.

For *defect detection*—each technology has limitations. A defect is defined as any physical, electrical, or parametric deviation capable of affecting yield. Existing SEMs and SPMs are considered too slow for the efficient detection of defects too small for optical microscopes. High-speed scanning has been demonstrated with arrayed SPMs, (that might be faster than SEMs) but issues associated with stylus lifetime, uniformity, characterization, and wear need to be addressed. This technology should be pursued both by expanding the size of the array and in developing additional operational modes. Arrayed micro-column SEMs have been proposed as a method of improving SEM throughput and operation of a single micro-SEM has been demonstrated. Research is needed into the limits of electrostatic and magnetic lens designs.

# LITHOGRAPHY METROLOGY

Lithography metrology continues to be challenged by rapid advancement of patterning technology. New materials in all process areas add to the challenges faced by Lithography Metrology. A proper control of the variation in transistor gate length starts with mask metrology. Although the overall features on a mask are four times larger than as printed, phase shift and optical proximity correction features are roughly half the size of the printed structures. Indeed, larger values for Mask Error Factor (MEF) might require a tighter process control at mask level, too; hence, a more accurate and precise metrology have to be developed. Mask metrology includes measurements that determine that the phase of the light correctly prints. Both on-wafer measurement of critical dimension (CD) and overlay are also becoming more challenging. CD control for transistor gate length continues to be a critical part of manufacturing IC's with increasing clock speeds. Acceleration of research and development activities for CD and overlay are essential if we are to provide viable metrology for future technology generations. All of these issues require improved methods for evaluation of measurement capability.

Although a number of potential solutions for CD measurement exist, there is no unique technique that matches every measurement requirement. Often, special test structures are measured during manufacturing. When this is the case, active device dimension are not measured. CD-SEM continues to be used for wafer and mask measurement of lines and via/contact. A considerable effort has been aimed at overcoming electron beam damage to photoresist used by 193 nm exposures and that will continue when 157 nm exposure tools are introduced. Stack materials, surface condition, line shape and even layout in the line vicinity may affect CD-SEM waveform and, therefore, extracted line CD. These effects unless they are accurately modeled and corrected increase measurement variation and, therefore, total uncertainty of CD SEM measurements. Developments in electron beam source technology that improve resolution and precision are being tested. CD-SEM is facing an issue with poor depth of field unless a new approach to SEM based CD measurement is found. High-voltage CD-SEM and low loss detectors have been proposed as means of extending CD-SEM.<sup>2</sup> Scatterometry has moved into manufacturing, and does provide line shape metrology. Here, scatterometry refers to both single wavelength - multi angle optical scattering and to multi-wavelength - single angle methods. Recent advances have resulted in the ability to determine CD and line shape without the aid of a library of simulated results. Scatterometry has already been shown to provide a tighter distribution of key transistor electrical properties when used in an Advanced Process Control mode. The next step is the development of scatterometry for contact and via structures. Scatterometry models assume uniform optical property of line and background materials. Surface anomalies and non-uniform dopant distribution may affect scatterometry results. Therefore, scatterometry models need calibration and periodic verification. Litho and etch microloading effects may noticeably affect line CD. Since scatterometry makes measurements on special test structures, other CD metrology techniques (such as SEM or AFM) need to be employed to establish correlation between CD of the scatterometry structure and CDs of the circuit. Scatterometry needs to be capable of measuring smaller

<sup>&</sup>lt;sup>2</sup> A.C. Diebold and D. Joy. CD measurements for Future Technology Generations. Solid State Technology, June 2003.

test structures while improving measurement precision. The use of "feed forward" control concepts must be extended to lithography metrology taking data from resist measurements and controlling subsequent processing, such as etch, to improve product performance. The use of overlay measurement equipment for CD control has also been reported. This method is based on the fact that the change in line width also affects the length of the photoresist lines that can then be measured using the optical microscope of the overlay system. A special test structure with arrays of line and arrays of spaces is required. CD-AFM measurements are an excellent means of verifying line shape and calibrating CD measurements. New probe tip technology and 3-D tiltable cantilever is required if CD-AFM is to be applied to dense line measurement below 90 nm node. Focus - Exposure correlation studies (especially for contact/via) can be done using all of the above methods as well as by the dual beam FIB (SEM plus focused ion beam) where there is an immediate correlation with line shape. Electron holography has been proposed as a long term CD measurement technology.

Line edge roughness (LER) is an important part of lithography process control. Line width roughness (LWR) is an important part of etch process control. The Lithography Roadmap provides metrics for both LER and LWR. In 2001, LWR requirements were listed as LER. LWR was included in the 2001 ITRS because it was correlated to an increase in transistor leakage current but not to changes in drive current. It is important to note that the precision requirement for LER are several years ahead of those required for CD as indicated below. Although CD-SEM and lithography process simulation systems have software that determines LER, there is no standard method of determining line edge roughness. Thus standardized assessment of the status of LEW and LWR versus roadmap requirements is not possible.

Critical dimension measurement capability does not meet precision requirements that comprehend measurement variation from individual tool reproducibility, tool to tool matching and sample-to-sample measurement bias variation. Precision is defined by SEMI as a multiple of reproducibility. As indicated in the introduction, reproducibility includes repeatability, variation from reloading the wafer, and long-term drift. In practice, reproducibility is determined by repeated measurements on the same sample over an extended period of time. Although the precision requirements for CD measurement in the ITRS have always included the effects of line shape and materials variation, repeated measurements on the same sample would never detect measurement uncertainty related to sample-to-sample bias variation. Therefore, with the current methodology the uncertainty of measurement associated with variation of line shape, material, layout or any other parameter will not be included in the precision. Typically, reference materials for CD process control are specially selected optimum or "golden" wafers from each process level. Thus, industry practice is to determine measurement precision as a reproducibility of the measurement for each process level. The measurement bias is not detected. This approach misses measurement bias variation component of measurement uncertainty. In light of this, a new metric, total measurement uncertainty, (TMU), has been proposed. The components of total uncertainty need to be properly assessed for every metrology tool. This would allow meaningful comparisons and improved tool matching. Total measurement variation defines a new precision-like variable P(TMU). P(TMU) would be determined using a technology representative set of samples that accounts for variations in measurement bias associated with each process level. One way to reduce TMU is to correct CD measurement bias at each process level.

Calibration of in-line CD metrology equipment requires careful implementation of the calibration measurement equipment. For example, laboratory based, cross-sectional SEM or CD-AFM must have precision that matches or exceeds in-line CD and have to be frequently calibrated. Reference materials used during manufacturing must be representative to the actual process level and structure. Due to the importance of maintaining control of transistor gate length as well as other structures, different metrology systems may be selected for transistor gate control. Reports of this approach already exist

CD measurement has been extended to line shape control. Tilt beam CD-SEM, comparison of line scan intensity variation versus line scans from a golden wafer, scatterometry, CD-AFM, and the dual beam FIB (electron and ion beam systems) have all been applied to line shape measurement. Sidewall angle has been proposed as the key process variable. Already, photoresist lines have shapes that are not well described by a single planar description of the sidewall. Line edge and line width roughness along a line, vertical line edge roughness, and rounded top shapes are important considerations in process control. As mentioned above, precision values change with each process level. This adds to the difficulty in determination of etch bias (the difference in CD before and after etch). Electrical CD measurements provide a monitoring of gate and interconnect line width, but only after the point where reworking the wafers is no longer possible and does not allow a real-time correction of process parameter.

\_

<sup>&</sup>lt;sup>3</sup> K. Patterson, J.L. Sturtevant, J. Alvis, N. Benavides, D. Bonser, N. Cave, C. Nelson-Thomas, B. Taylor, K. Turnquest, Experimental Determination of the Impact of Polysilicon LER on sub-100 nm Transistor Performance, In Metrology, Inspection, and Process Control for Microlithography XV, SPIE Vol 4344, 2001, pp 809–814.

Lithography metrology consists not only of overlay and CD metrology (essentially microscopy to measure width, depth, and shape of printed features after completion of the lithography step), but also includes the process control and characterization of materials needed for lithography process, especially photoresists, phase shifters, and antireflective coatings (ARCs). As these lithography materials become more complex, the materials characterization associated with them also increases in difficulty. Additionally, most (non-lithography) materials used in the wafer fabrication process (gate oxides, metals, low-κ dielectrics, SOI substrates, etc) enter the lithography process indirectly, since their optical properties affect the reflection of light at a given wavelength. Even a small variation in process conditions for a layer not normally considered critical to the lithography process (e.g. the thickness of the buried oxide in SOI wafers) can change the dimensions or shapes of the printed feature, if this process change affected the optical response of the layer.

As a minimum, the complex refractive index (refractive index n and extinction coefficient  $\kappa$ ) of all layers needs to be known at the lithography wavelength. Literature data for such properties are usually not available or obsolete and not reliable (derived from obsolete reflectance measurements on materials of unknown quality followed by Kramers-Kronig transform). In ideal cases, n and  $\kappa$  can be measured inline using spectroscopic ellipsometry at the exposure wavelength. Especially below 157 nm, such measurements are very difficult and usually performed outside of the fab by engineering personnel. EUV optical properties can only be determined using specialized light sources (such as a synchrotron). Therefore, materials composition is often used as a figure of merit, when direct measurement of the optical properties is not practical. But even two materials with the same composition can have different optical properties (take amorphous and crystalline Si as an example).

Additional complications in the determination of the optical properties of a material arise from surface roughness, interfacial layers, birefringence or optical anisotropy (often seen in photoresists or other organic layers responding to stress), or depth-dependent composition. For some materials for a wafer fab, it is impossible to determine the optical properties of such material, since the inverse problem of fitting the optical constants from the ellipsometric angles is underdetermined. Therefore, physical materials characterization must accompany the determination of optical properties, since physical characteristics, materials properties, and optical constants are all inter-related.

Overlay measurements are challenged by phase shift and optical proximity correction masks, and the use of different exposure tools for metal trench and via will compound the difficulty.

Future overlay metrology requirements, along with problems caused by low contrast levels, will drive the development of new optical or SEM methods along with scanning probe microscopy (SPM). The need for new target structures has been suggested as a means of overcoming the issues associated with phase shift mask and optical proximity mask alignment errors not detectable with traditional targets. Overlay for on-chip interconnect will continue to be challenging. The use of chemical mechanical polishing for planarization degrades target structures. Thus as requirements for tighter overlay control are introduced, the line edge of overlay targets in interconnect are roughened. The low- $\kappa$  materials used as insulators will continue to make overlay more difficult especially as porous low  $\kappa$  move into manufacturing.

The Lithography Metrology Requirements Tables are divided into wafer and mask requirements. The mask metrology requirements are further divided into the needs for each type of exposure technology: optical, EUV, and electron projection .

Table 117a Lithography Wafer Metrology Technology Requirements—Near-term

| Year of Production                                                                                                                             | 2003         | 2004  | 2005  | 2006 | 2007 | 2008  | 2009 |

|------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|-------|------|------|-------|------|

| Technology Node                                                                                                                                |              | hp90  |       |      | hp65 |       |      |

| DRAM ½ Pitch (nm)                                                                                                                              | 100          | 90    | 80    | 70   | 65   | 57    | 50   |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                                                                                             | 120          | 107   | 95    | 85   | 76   | 67    | 60   |

| MPU/ASIC Un-contacted Poly ½ Pitch (nm)                                                                                                        | 107          | 90    | 80    | 70   | 65   | 57    | 50   |

| MPU Printed Gate Length (nm)                                                                                                                   | 65           | 53    | 45    | 40   | 35   | 32    | 28   |

| MPU Physical Gate Length (nm)                                                                                                                  | 45           | 37    | 32    | 28   | 25   | 22    | 20   |

| Printed gate CD control (nm) Uniformity (variance) is 10% of CD Allowed lithography variance = 4/5 total variance of physical gate length [A]* | <b>4.0</b>   | 3.3   | 2.9   | 2.5  | 2.2  | 2.0   | 1.8  |

| Wafer dense line CD control (nm) * Uniformity is 15% of CD Allowed lithography variance = 2/3 total variance                                   | 12.2         | 11.0  | 9.8   | 8.6  | 8.0  | 7.0   | 6.1  |

| Wafer minimum contact hole (nm, post etch) from lithography tables                                                                             | 115          | 100   | 90    | 80   | 70   | 65    | 55   |

| Wafer contact CD control (nm)* Uniformity is 15% of CD = minimum contact hole size Allowed lithography variance = 2/3 total variance           | 14.1         | 12.2  | 11.0  | 9.8  | 8.6  | 8.0   | 6.7  |

| Line width roughness (nm, 3 σ) <8% of CD ***                                                                                                   | <b>♦</b> 3.6 | 3.0   | 2.6   | 2.2  | 2.0  | 1.8   | 1.6  |

| Wafer CD metrology tool precision (nm) * $3\sigma$ at P/T = 0.2 for isolated printed and physical lines [A]                                    | 0.8          | ♦ 0.7 | 0.6   | 0.5  | 0.4  | 0.4   | 0.4  |

| Wafer CD metrology tool precision (nm) * ( P/T=.2 for dense lines**)                                                                           | 2.4          | 2.2   | 2.0   | 1.7  | 1.6  | 1.4   | 1.2  |

| Wafer CD metrology tool precision (nm) * (P/T=.2 for contacts**)                                                                               | 2.8          | 2.4   | 2.2   | 2.0  | 1.7  | 1.6   | 1.3  |

| Wafer CD metrology tool precision (nm) * (P/T=.2) for LWR***                                                                                   | 0.72         | 0.592 | 0.512 | 0.4  | 0.4  | 0.352 | 0.32 |

| Maximum CD measurement bias (%) [B]                                                                                                            | 10           | 10    | 10    | 10   | 10   | 10    | 10   |

| Wafer overlay control (nm)                                                                                                                     | 35           | 32    | 28    | 25   | 23   | 21    | 19   |

| Wafer overlay output metrology precision (nm, 3 $\sigma$ )* P/T=.1                                                                             | 3.5          | 3.2   | 2.8   | 2.5  | 2.3  | 2.1   | 1.9  |

<sup>\*</sup> All precision values are 3 Sigma in nm and include metrology tool-to-tool matching.

LER—Local line-edge variation (3 sigma total, all frequency components included, both edges) evaluated along a distance that allows determination of spatial wavelength equal to two times the technology node. LWR is defined as LWR=sqrt(2)LER for uncorrelated line edge roughness.

Manufacturable solutions exist, and are being optimized

Manufacturable solutions are known

Interim solutions are known

Manufacturable solutions are NOT known

<sup>\*\*</sup> Measurement tool performance needs to be independent of target shape, material, and density.

<sup>\*\*\*</sup> The Lithography roadmap has changed from line edge roughness (LER) to line width roughness (LWR).

Table 117b Lithography Metrology Technology Requirements—Long-term

| Year of Production                                                                                                                              | 2010  | 2012  | 2013  | 2015 | 2016  | 2018  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|-------|-------|

| Technology Node                                                                                                                                 | hp45  |       | hp32  |      | hp22  |       |

| DRAM ½ Pitch (nm)                                                                                                                               | 45    | 35    | 32    | 25   | 22    | 18    |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                                                                                              | 54    | 42    | 38    | 30   | 27    | 21    |

| MPU/ASIC Un-contacted Poly ½ Pitch (nm)                                                                                                         | 45    | 35    | 32    | 25   | 22    | 18    |

| MPU Printed Gate Length (nm)                                                                                                                    | 25    | 20    | 18    | 14   | 13    | 10    |

| MPU Physical Gate Length (nm)                                                                                                                   | 18    | 14    | 13    | 10   | 9     | 7     |

| Printed gate CD control (nm) Uniformity (variance) is 10% of CD Allowed lithography variance = 4/5 total variance of physical gate length [A] * | 1.6   | 1.3   | 1.2   | 0.9  | 0.8   | 0.6   |

| Wafer dense line CD control (nm) * Uniformity is 15% of CD Allowed lithography variance = 2/3 total variance                                    | 5.5   | 4.3   | 3.9   | 3.1  | 2.7   | 2.2   |

| Wafer minimum contact hole (nm, post etch) from lithography tables                                                                              | 50    | 35    | 30    | 25   | 21    | 18    |

| Wafer contact CD control (nm)* Uniformity is 15% of CD = minimum contact hole size Allowed lithography variance = 2/3 total variance            | 6.1   | 4.3   | 3.7   | 3.1  | 2.6   | 2.2   |

| Line width roughness (nm, 3 σ) <8% of CD ***                                                                                                    | 1.4   | 1.1   | 1.0   | 0.8  | 0.7   | 0.6   |

| Wafer CD metrology tool precision (nm) * $3\sigma$ at P/T = 0.2 for isolated printed and physical lines [A]                                     | 0.3   | 0.3   | 0.2   | 0.2  | 0.2   | 0.1   |

| Wafer CD metrology tool precision (nm) * (P/T=.2 for dense lines**)                                                                             | 1.1   | 0.9   | 0.8   | 0.6  | 0.5   | 0.4   |

| Wafer CD metrology tool precision (nm) * (P/T=.2 for contacts**)                                                                                | 1.2   | 0.9   | 0.7   | 0.6  | 0.5   | 0.4   |

| Wafer CD metrology tool precision (nm) * (P/T=.2) for LWR***                                                                                    | 0.288 | 0.224 | 0.208 | 0.16 | 0.144 | 0.112 |

| Maximum CD measurement bias (%) [B]                                                                                                             | 10    | 10    | 10    | 10   | 10    | 10    |

| Wafer overlay control (nm)                                                                                                                      | 18    | 14    | 12.8  | 10   | 8.8   | 7.2   |

| Wafer overlay output metrology precision (nm, 3 σ)* P/T=.1                                                                                      | 1.8   | 1.4   | 1.3   | 1.0  | 0.9   | 0.7   |

<sup>\*</sup> All precision values are 3 sigma in nm and include metrology tool-to-tool matching.

LER-Local line-edge variation (3 sigma total, all frequency components included, both edges) evaluated along a distance that allows determination of spatial wavelength equal to two times the technology node. LWR is defined as LWR=sqrt(2)LER for uncorrelated line edge roughness.

Notes for Tables 117a and 117b:

[A] The orange designation for CD measurement for isolated lines in the near term is a result of roadmap process range and need for tool matching in the precision requirement also makes this requirement very difficult to achieve. A work around for isolated line CD measurement is to use a single tool and avoid tool matching. Long term, CD measurement for 25 nm linewidths requires a technology breakthrough because extension of known methods may not be possible.

<sup>\*\*</sup> Measurement tool performance needs to be independent of target shape, material, and density.

<sup>\*\*\*</sup> The Lithography roadmap has changed from line edge roughness (LER) to line width roughness (LWR).

Table 118a Lithography Metrology (Mask) Technology Requirements: Optical—Near-term

| Year of Production                                                                                                                   | 2003         | 2004         | 2005         | 2006         | 2007 | 2008 | 2009 |

|--------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|--------------|------|------|------|

| Technology Node                                                                                                                      | 2003         | hp90         | 2003         | 2000         | hp65 | 2000 | 2007 |

| DRAM ½ Pitch (nm)                                                                                                                    | 100          | 90           | 80           | 70           | 65   | 57   | 50   |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                                                                                   | 120          | 107          | 95           | 85           | 76   | 67   | 60   |

| MPU/ASIC Un-contacted Poly ½ Pitch (nm)                                                                                              | 107          | 90           | 80           | 70           | 65   | 57   | 50   |

| MPU Printed Gate Length (nm)                                                                                                         | 65           | 53           | 45           | 40           | 35   | 32   | 28   |

| MPU Physical Gate Length (nm)                                                                                                        | 45           | 37           | 32           | 28           | 25   | 22   | 20   |

| Printed gate CD control (nm) allowed lithography variance                                                                            | 73           |              |              |              |      |      | 20   |

| = 4/5 total variance of physical gate length [A] *                                                                                   | <b>4.0</b>   | 3.3          | 2.9          | 2.5          | 2.2  | 2.0  | 1.8  |

| Wafer overlay control (nm)                                                                                                           | 35           | 32           | 28           | 25           | 23   | 21   | 19   |

| Wafer minimum contact hole (nm, post etch) from lithography tables                                                                   | 115          | 100          | 90           | 80           | 70   | 65   | 55   |

| Wafer contact CD control (nm)* Uniformity is 15% of CD = minimum contact hole size Allowed lithography variance = 2/3 total variance | 14.1         | 12.2         | 11.0         | 9.8          | 8.6  | 8.0  | 6.7  |

| Mask nominal image size (nm) [B]                                                                                                     | 260          | 212          | 180          | 160          | 140  | 128  | 112  |

| Mask minimum primary feature size [C]                                                                                                | 182          | 148.4        | 126          | 112          | 98   | 89.6 | 78.4 |

| Optical                                                                                                                              | Section      |              |              |              |      |      |      |

| Minimum OPC size (opaque at 4×, nm) [D]                                                                                              | 130          | 106          | 90           | 80           | 70   | 64   | 56   |

| Image placement (multipoint at 4×, nm)                                                                                               | 21           | 19           | 17           | 15           | 14   | 13   | 12   |

| CD uniformity allocation to mask (assumption)                                                                                        | 0.4          | 0.4          | 0.4          | 0.4          | 0.4  | 0.4  | 0.4  |

| Mask error factor (MEF) from lithography tables isolated lines, binary                                                               | 1.4          | 1.4          | 1.4          | 1.4          | 1.6  | 1.6  | 1.6  |

| MEF isolated lines, alternating phase shift [G]                                                                                      | 1            | 1            | 1            | 1            | 1    | 1    | 1    |

| MEF dense lines [G]                                                                                                                  | 2            | 2            | 2            | 2            | 2.5  | 3    | 3    |

| MEF contacts [G]                                                                                                                     | 3            | 3            | 3            | 3            | 3.5  | 4    | 4    |

| CD Uniformity (3 Sigma at 4×, nm) Refer to Lithography Chapter Table for                                                             | Optical Mas  | sk Requiren  | ients        |              |      |      |      |

| Isolated lines (MPU gates), binary Uniformity is 10% of CD [E], [F]                                                                  | 4.6          | 3.8          | 3.3          | 2.9          | 2.2  | 2.0  | 1.8  |

| Isolated lines (MPU gates), alternated Uniformity is 10% of CD [E], [G]                                                              | 6.4          | 5.3          | 4.6          | 4.0          | 3.6  | 3.1  | 2.9  |

| Dense lines (DRAM half-pitch) Uniformity is 15% of CD [E], [H]                                                                       | 9.8          | 8.8          | 7.8          | 6.9          | 5.1  | 3.7  | 3.3  |

| Wafer minimum contact hole (nm, post etch) from lithography tables                                                                   | 115          | 100          | 90           | 80           | 70   | 65   | 55   |

| Mask contact CD control (nm)* Uniformity is 15% of CD = minimum contact hole size Allowed lithography variance = 2/3 total variance  | 5.0          | 4.4          | 3.9          | 3.5          | 2.6  | 2.1  | 1.8  |

| Mask image placement metrology (precision, P/T=0.1)                                                                                  | 2.1          | 1.9          | 1.7          | 1.5          | 1.4  | 1.3  | 1.2  |

| Mask CD metrology tool precision* (P/T=0.2 for isolated lines, binary**)                                                             | ♦ 0.9        | 8.0          | 0.7          | 0.6          | 0.4  | 0.4  | 0.4  |

| Mask CD metrology tool precision* (P/T=0.2 for isolated lines, alternated**)                                                         | <b>•</b> 1.3 | <b>•</b> 1.1 | 0.9          | 0.8          | 0.7  | 0.6  | 0.6  |

| Mask CD metrology tool precision* (P/T=0.2 for dense lines**)                                                                        | <b>•</b> 2.0 | <b>1.8</b>   | <b>•</b> 1.6 | <b>•</b> 1.4 | 1.0  | 0.7  | 0.7  |

| Mask CD metrology tool precision* (P/T=0.2 for contact/vias**)                                                                       | <b>◆</b> 1.0 | ♦ 0.9        | 0.8          | 0.7          | 0.5  | 0.4  | 0.4  |

| Specific Requirements                                                                                                                |              |              |              |              |      |      |      |

| Alternated PSM phase mean deviation                                                                                                  | 2            | 2            | 2            | 1            | 1    | 1    | 1    |

| Phase metrology precision, P/T=0.2                                                                                                   | 0.4          | 0.4          | 0.4          | 0.2          | 0.2  | 0.2  | 0.2  |

| Alternated PSM phase uniformity (±degrees)                                                                                           | 2            | 2            | 2            | 1            | 1    | 1    | 1    |

| Phase uniformity metrology precision, P/T=0.2                                                                                        | 0.4          | 0.4          | 0.4          | 0.2          | 0.2  | 0.2  | 0.2  |

Manufacturable solutions exist, and are being optimized

Manufacturable solutions are known

Interim solutions are known

Manufacturable solutions are NOT known

Table 118b Lithography Metrology (Mask) Technology Requirements: EUV—Near and Long-term

| Year of Production                                                                             | 2008  | 2009        | 2010  | 2012  | 2013  | 2015  | 2016  | 2018  |

|------------------------------------------------------------------------------------------------|-------|-------------|-------|-------|-------|-------|-------|-------|

| Technology Node                                                                                |       |             | hp45  |       | hp32  |       | hp22  |       |

| DRAM ½ Pitch (nm)                                                                              | 57    | 50          | 45    | 35    | 32    | 25    | 22    | 18    |